双向端口应用实例

描述

双向端口简介

三态缓冲器也称三态门,其典型应用是双向端口,常用于双向数据总线的构建。在数字电路中,逻辑输出有两个正常态:低电平状态(逻辑0)和高电平状态(逻辑1),此外,电路还有不属于0和1的高阻态(逻辑Z)。所谓高阻,即输出端属于浮空状态,只有很小的漏电流流动,其电平随外部电平的高低而定,门电平放弃对输出电路的控制。或者可以理解为输出和电路是断开的。

在应用代码中,verilog HDL程序模块首先进行端口(input:输入端口;output:输出端口;inout:输入/输出端口)定义,然后是逻辑功能的描述。在verilog HDL中,output端口信号可以被定义为reg类型,并在always块中赋值使用,而inout端口不能被定义为reg类型,不能再always块中直接赋值使用,这一点与VHDL中的双向端口使用方法不同。

由于FPGA需要与外部存储器或CPU进行频繁的数据交换,以及引脚资源有限,使用双向端口设计可以成倍的节省数据引脚线。在设计中需要注意两点:其一,要用三态门的控制来处理实现双向端口;其二,要分别指定双向端口作为输入、输出端口时,对外部对象的数据操作。

2. 双向端口应用实例

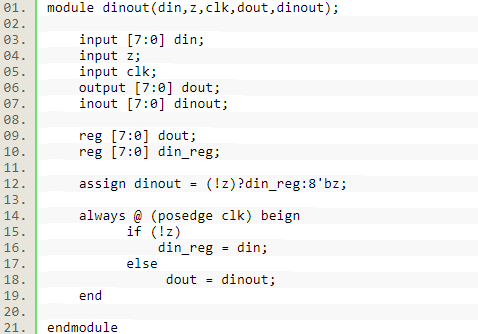

1. 双向端口的verilog HDL描述

如果输入输出端口都是16位,那么总共需要32根数据线,使用双向端口,只需要16根数据线。实例:

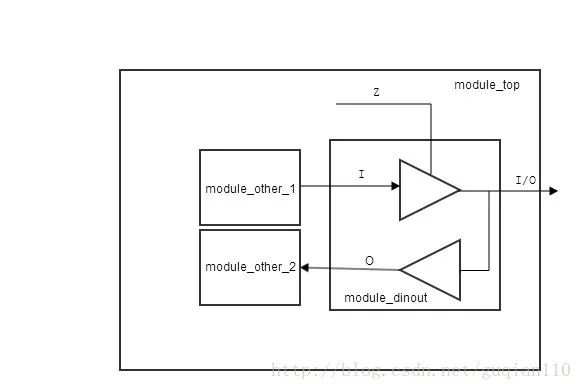

模块示意图:

dinout为双向端口,即可作为输入端口,又可作为输出端口;

当 z = 0 时,三态门选通,从模块module_other_1 输出的数据 data 的流动方向为 I ---> I/O ,I/O 作为系统(module_top)的输出端口;(对于模块module_dinout,I 的类型是input,I/O的类型声明为inout,此时作为输出端口)

当 z = 1 时,三态门关闭,数据 data 的流动方向为 O <--- I/O ,data输入到模块module_other_2 中,供其使用,I/O 作为系统(module_top)的输入端口;(对于模块module_dinout,O 的类型是output,I/O的类型声明为inout,此时作为输入端口)

2. 双向端口的仿真

编写测试模块时,对于inout类型的端口,需要定义成wire类型,而其他输入端口定义为reg类型。此外,对于双向端口本身,仿真输出端口和输入端口的语法是不同的。

输出端口仿真

当作为输出端口时,不需要对其进行初始化,只要开通三态门即可。

输入端口仿真

当作为输入端口时,需要对其进行初始化赋值并关闭三态门。而如果直接把它跟一般的输入口一样直接初始化赋值,则会出错,因为它的定义是wire类型而不是reg类型。这里需要用到force命令。

审核编辑 :李倩

-

VHDL中双向inout端口的实现2012-04-01 0

-

请教各位有关双向端口的使用问题2012-11-10 0

-

怎么连接Vhdl中的两个双向端口2019-01-29 0

-

【verilog每日一练】“inout” 双向端口类型的使用2023-08-03 0

-

PPPoE配置实例(单以太端口2600路由器接ADSL Mo2010-01-13 584

-

FPGA中双向端口IO的研究2011-09-27 2424

-

移相占空比控制的三端口双向直流变换器_王政2017-01-08 927

-

单片机端口“准双向”的机理剖析2018-01-24 614

-

如何进行STC12单片机双向端口的设置2019-09-04 1004

-

使用扩展芯片实现端口扩展的实例资料合集免费下载2019-07-25 877

-

Arduino进行端口通信的实例程序免费下载2019-05-13 844

-

单BuckBoost 集成三端口双向DCDC 变换器研究2021-09-27 951

-

交错并联双向BuckBoost集成LLC谐振型三端口直流变换器2021-09-27 1060

-

verilog双向端口的使用2024-02-23 348

全部0条评论

快来发表一下你的评论吧 !