x86巨头英特尔也开始发力RISC

x86巨头英特尔也开始发力RISC

描述

在如今的AI研究领域,知识图谱的概念越来越普及。这种符号化的人工智能依靠的不是字符串,而是图之间的关系来解决查询、推理的挑战,从而做到更擅长理解的AI。然而如今传统的计算架构可以说只认数字不认图,在数据规模一大的情况下,就会出现性能瓶颈,而这里的瓶颈不是计算能力,而是通信带宽。

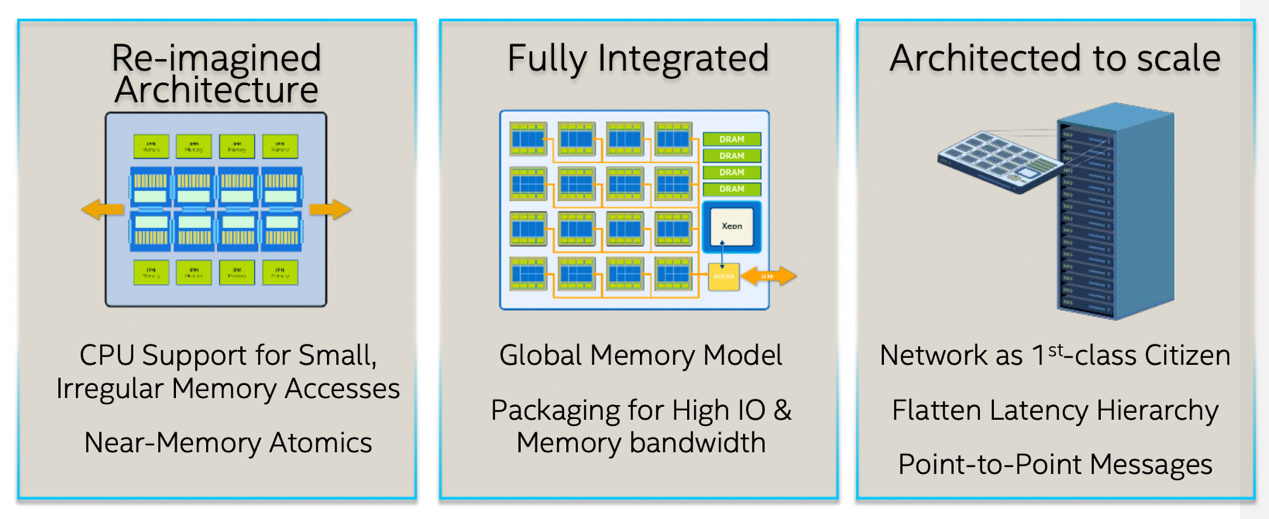

为此,英特尔开发出了一个新的架构PIUMA(可编程集成统一内存架构)。这一架构可以用比传统硬件架构更快的速度遍历图表,获得实时分析。受益于没有交换机、极高带宽和计算与I/O平衡的优势,PIUMA可以实现超低的延迟下分析数百TB乃至PB级规模的数据。

为此,英特尔开发出了一个新的架构PIUMA(可编程集成统一内存架构)。这一架构可以用比传统硬件架构更快的速度遍历图表,获得实时分析。受益于没有交换机、极高带宽和计算与I/O平衡的优势,PIUMA可以实现超低的延迟下分析数百TB乃至PB级规模的数据。

PIUMA架构 / 英特尔

根据英特尔的说法,一个PIUMA核心等于多个处理器流水线+多线程,而且该架构用到了他们自研的全新64位RISC指令集,并专门针对图做了指令优化。再加上每一个核心都能访问的全局地址空间,PIUMA可以做到极高的扩展性,让所有节点共用这一地址网络。

英特尔指出,传统的架构追求的如何实现更高的TOPS算力,因此在计算、内存和I/O中,计算一直是占大头,接着才轮到内存和I/O。而PIUMA追求的是如何实现更高的TTEPS(每秒多少遍历边缘),同时又不至于低算力,因此对计算、内存和I/O进行了平衡。

英特尔对RISC-V的看法

看到这里,你可能会有疑问,英特尔为何不直接用RISC-V呢?很大程度上是因为PIUMA这一架构还是面向图表AI这类的应用,并非通用架构。此外,RISC-V已经成了市面上增长最快的第三大ISA,虽然动力很足,但英特尔表示这一ISA还在发展初期,而他们目前想做的,只是成为这一架构的助推者。

此前英特尔传出过收购SiFive的消息,但这事最终没成,可英特尔并没有选择放弃自己对RISC-V的支持,不过不是直接用于自己的产品(除了Mobileye的自动驾驶芯片),而是转为促进RISC-V生态的发展,靠的正是其代工业务IFS。

要知道,开源架构对整个半导体IP产业来说,还是相对较新的事物,因为用户有了自由针对独特的应用定制处理器核心,做到差异化。IFS已经和晶心科技、Esperanto、SiFive和Ventana这样的RISC-V IP厂商合作,为他们提供IFS最好的PPA表现。代工的不仅限于CPU核心,还有Chiplet已经封装好的产品。

RISC-V的未来

几日前,RISC-V国际基金会CEO Calista Redmond表示,她希望RISC-V有朝一日能“统治世界”,不过她的意思还是期望RISC-V、ARM和x86能够同台竞技,毕竟其余两者都在各自擅长的领域做到了一定程度的垄断。

不过,谷歌的计算机架构师,此前曾任职NUVIA副总裁的Jon Masters表示,RISC-V目前面临的最大的挑战之一就是防止碎片化,充分践行标准的概念。如果RISC-V不建立起标准信仰的话,很有可能会走上MIPS的老路。

他认为,对于嵌入式设备来说,灵活、碎片化的架构没什么不好,至少可以让市场上不只是Xtensa、ARM等少量RISC玩家。但要想更进一步,就必须尽早放弃这套“一切均可自定义”的概念。除非RISC-V拥有一个像PC或智能手机这样“无聊”的通用硬件平台,那么很难做到真正的“统治一切”,哪怕是ARM也花了十年的时间,才使得一小部分生态变得“无聊”。

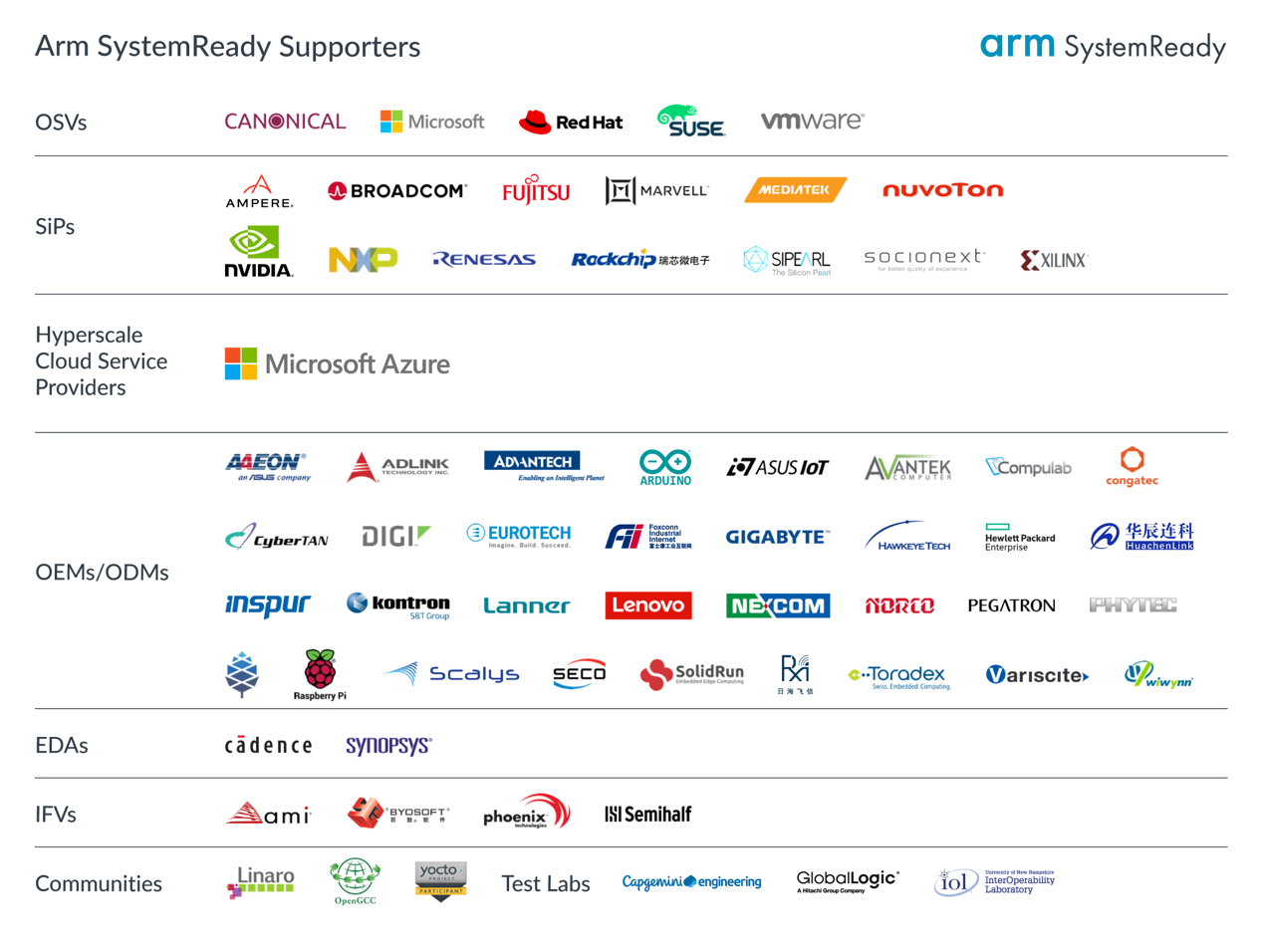

支持SystemReady的厂商 / ARM

Jon Masters认为标准化和防止碎片化应该作为第一要务,而不是局限于某个特定的工作组。他觉得即便是ARM在这方面也有不足之处,ARM应该更大力度地推行SystemReady认证计划,少一些未通过认证的流片,多一些软件正常工作的系统。当然了,这一计划ARM也是才启动不久,数日前通过认证的系统数才刚过50。

不过Jon Masters主要负责服务器级的ARM开发,所以还是站在ARM的角度来看问题。依笔者看来RISC-V可以吸收ARM的经验,但不一定非得和ARM走同一条路。没错,现在RISC-V在智能手机和PC全球占比最大的两大消费电子上确实无迹可寻,但谁又能说的准未来不会有这样一个时机给到RISC-V呢?

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

x86自主新架构呼之欲出!英特尔怕了吗?#英特尔 #芯片电子发烧友网官方 2022-01-25

-

#高通 #英特尔 #Elite 高通X Elite芯片或终结苹果、英特尔的芯片王朝深圳市浮思特科技有限公司 2023-10-27

-

ARM:低调的隐形超级芯片帝国,谁在革英特尔的命2011-12-24 0

-

英特尔转型移动领域难言乐观2012-11-07 0

-

基于英特尔X86平台主板硬件设计系列知识分享2015-10-25 0

-

产业风暴,英特尔能否扳倒ARM?2016-09-26 0

-

AMD扩展x86并行指令集2019-07-26 0

-

适用于x86架构的快速启动步骤是什么?2020-03-20 0

-

Powerpc架构与X86架构的区别2021-07-26 0

-

x86架构的最大特色在哪2021-07-27 0

-

大型机、小型机、x86服务器的区别 精选资料分享2021-07-28 0

-

如果arm CHIP內建x86 decoder會能跑x86吗2022-06-14 0

-

四大主流芯片架构(X86、ARM、RISC-V和MIPS)2023-02-27 0

-

RISC-V和X86、ARM的竞争如何?2021-01-15 3822

-

基于英特尔 x86 和 IOP 的系统互连软件 API2023-04-26 152

全部0条评论

快来发表一下你的评论吧 !