如何优化使用双核PSoC 6的多种功耗模式方面

描述

低功耗运行仍然是各行各业应用的关键驱动力。随着睡眠模式的加入,电源管理突然从单纯的硬件问题转变为软件开发人员必须考虑的问题。

电源模式最简单的应用是,当系统空闲时,您将其置于睡眠状态。然而,当今的 MCU 提供了多种低功耗模式,使低功耗设计更加复杂。现在,开发人员需要考虑多核、高频信号处理的复杂独立性,以及如何可靠地满足系统的所有实时期限。

我请 Cypress Semiconductor 的系统工程师 Greg Verge 分享了他在如何优化使用双核 PSoC 6 的多种功耗模式方面的经验。除了 Active(例如 LP 或 Low Power)和 Sleep(例如 ULP 或超低功耗)模式,这款 Cortex M0 + Cortex M4 SoC 支持深度睡眠和休眠模式。开发人员还可以选择降低核心电压以节省电力。

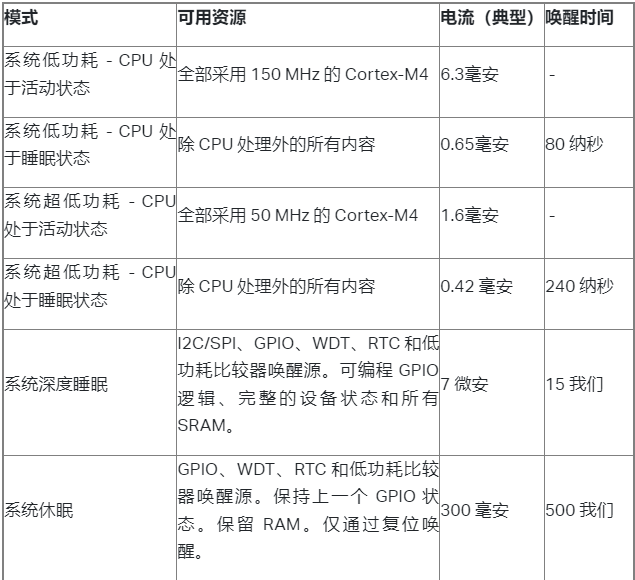

每种电源模式都会点亮 SoC 的不同部分(参见表 1)。Active 为整个芯片供电,而 Hibernate 仅驱动维持 RAM、实时时钟和 I/O 引脚配置所需的最低要求。模式节省的电量越多,SoC 可以做的越少,唤醒回活动模式所需的时间就越长。

睡眠模式仍然是您的空闲循环。CPU 时钟停止,但可以通过来自其他内核的中断或请求快速恢复到活动模式。外围设备可以保持活动状态,CPU“立即”从中断的地方执行代码。

深度睡眠很像睡眠,但更多的芯片被关闭并且唤醒时间更长。使用睡眠或深度睡眠的决定取决于系统需要唤醒多快以及系统关闭时哪些外设需要处于活动状态。高频时钟不通电,因此您会丢失一些通信链路 (UART),同时能够保留其他通信链路(SPI 和 I2C)。您还会丢失 ADC,因为它们需要 MHz 时钟。你的 PWM 也会消失,所以当 LED 熄灭时不要担心。

事情开始变得复杂的地方是多核。低功耗模式会影响 CPU 和系统。让一个 CPU 进入深度睡眠不会自动关闭系统资源,因为其他 CPU 可能正在使用它们。因此,只有两个 CPU 都处于深度睡眠状态时,您才能获得完全的低功耗优势。如果您的内核在尝试深度睡眠时不同步,这可能会严重影响您的整体电源效率。

休眠模式

休眠模式将系统置于其最低功耗状态。Hibernate 是一种承诺,因为您不能简单地恢复执行;系统需要重置。当您只需要一点智能来唤醒系统时,休眠在非常长的睡眠期间很有用。这对于实现电源关闭/开启功能或操作低频传感器很有用。

休眠模式还支持保留 RAM 以保存有限的状态信息。例如,您可以存储以前的传感器读数。当您重置系统时,它会检查传感器并将当前值与之前的值进行比较。如果它们在阈值范围内,则不会触发任何事件,系统将返回休眠模式。实现了最大功率效率。

仅仅因为你已经设法让 CPU 进入正确的低功耗模式并不意味着你正在高效运行。在深度睡眠和休眠中,I/O 引脚的泄漏会主导功耗。考虑一个用于偏置电阻的引脚。除了确保使用尽可能高的电阻外,引脚还需要适当地保持高或低,以最大限度地减少功耗(即泄漏)。

休眠模式维护 I/O 引脚的配置,以便您可以将所有引脚保持在最低功耗状态。例如,将电阻器直接连接到电源是一种常见的做法。如果您改为将电阻器连接到 GPIO,而不是电阻器不断消耗功率,您现在可以打开和关闭电阻器。如果您没有意识到这一点,您可能会假设系统在引脚实际绘制 1 ma 时以低 7 µA 的电流运行。从这个角度来看,效率降低了 143 倍,将 10 年的使用寿命缩短到 25 天。

影响低功耗运行的另外两个主要因素是降低核心电压和选择稳压器。例如,PSoC 6 可以为其内核提供 1.1 V 或 0.9 V 的电压。您无法以 0.9V 快速为内核提供时钟,但如果您只是检查温度传感器,那么 50 MHz 仍然要高得多处理超出您的需要。

稳压器的选择(集成 LDO 或高效开关模式降压转换器)允许您以功率效率换取成本。使用降压转换器可为您提供 90% 的效率,但代价是外部电感器。

随着芯片制造商不断改进低功耗运行,我们的嵌入式系统将能够事半功倍。请记住,随着更多选项的出现,更多的方法可以消除您优化系统的所有辛勤工作,只需简单地误解系统实际在做什么。

表 1:不同的功耗操作模式使开发人员能够优化运行时功耗,但您仍然需要小心。此处显示的是 Cypress Semiconductor 的双核 PSoC 6 的模式、电流和唤醒时间。

-

PSoC双核架构中双核都可以访问全部外设吗?2024-02-02 0

-

TMS320C6657的编程优化与双核加载2018-08-29 0

-

可以提供双核初始化和使用方面的资料吗2018-10-09 0

-

采访Michi Yoneda关于赛普拉斯的PSoC 62018-11-01 0

-

8位微控制器的多种低功耗模式2019-07-24 0

-

运算放大器的低功耗模式可以应用于psoc5lp吗?2019-09-04 0

-

如何最好地优化应用程序并利用PSoC的低功耗模式能力呢?2019-10-25 0

-

实现低功耗嵌入式设计的多种优化方式2020-01-17 0

-

赛普拉斯Arm Cortex 32位微控制器(MCU)PSoC®6介绍!2020-09-01 0

-

ARM是怎样使用多种低功耗模式来节省功耗的2022-02-11 0

-

PSOC6核心板的资料分享2022-08-15 0

-

基于PSoC3实现智能电风扇的设计2020-07-01 8332

-

STM32 低功耗睡眠模式(SLEEP)事件(EVENT)唤醒实现及优化2021-12-31 1406

全部0条评论

快来发表一下你的评论吧 !