减小嵌入式SoC尺寸的解决方案

描述

嵌入式微控制器和混合信号系统级芯片 (SoC) 市场在主流技术工艺节点上制造时显示出强劲增长。混合信号市场价值近 300 亿美元,约占 3000 亿美元半导体产业的 10%,随着新消费应用的出现,这种增长将继续。例如,触摸屏技术和手机独立存在多年。以智能手机形式出现的更好的人类用户界面已经建立了一个三年前不存在的市场。

混合信号电路使我们的模拟“真实”世界能够与其电子数字对应物进行交互。随着嵌入式应用程序继续达到更高的容量和更多的移动实施,设计人员正面临着降低成本和降低功耗的问题。

嵌入式和混合信号设计的一个挑战是大批量设计的成本敏感性。产品价格越低,可以采用该技术的潜在应用数量就越多。一种降低半导体成本的方法是在小工艺几何形状中制造。但在混合信号市场,开发者留在主流节点有几个原因:

在半导体工艺中,模拟组件的扩展性不如数字组件。因此,缩放带来的密度优势远低于数字组件所获得的优势。

大多数混合信号设备不具备数字设备的高速要求。许多混合信号设备的运行速度低于 100 MHz,因此无需快速转移到下一个领先的工艺节点。

较旧的工艺技术稳定,具有众所周知的模拟特性。低风险和低成本使旧技术节点的制造更具吸引力。

嵌入式 SoC 设计人员必须寻找创新的解决方案来减小芯片尺寸,同时保持主流工艺技术。

嵌入式设计人员面临的另一个挑战是降低功耗。在 250 纳米,代工厂没有投资于降低动态和泄漏功率所需的工艺创新。某些应用程序需要额外的电源优化以将电池寿命延长至 2-5 天,智能手机就是这种情况。一些医疗应用(例如起搏器)需要低功耗解决方案,以使电池能够使用 5-10 年或更长时间。使用纳米或皮安放大器可以最大限度地减少大范围的手术,从而提高患者的生活质量。

无论应用程序处于电池寿命的极端还是处于中间状态,一个不变的因素是用户在一次充电时需要更多的功能。嵌入式设计人员面临的挑战是在保持低风险的同时增加功能——在成熟的工艺节点上——并减少面积和功耗以增加功能和电池寿命差异化。

嵌入式处理器的功能创新

混合信号 SoC 要么包含一个低功耗微控制器,要么与一个独立的微控制器一起工作,以执行来自用户的命令并处理中断并提供传入数据的读数。ARM 提供一系列现代 32 位处理器,即 Cortex-M 系列,专为低功耗微控制器而设计。

为了满足对附加功能的需求,这些处理器通过性能效率在给定的占用空间内提供更高的性能——更快地完成任务并因此减少活动周期的能力。性能优势源于 Cortex-M 执行单周期 32 位算术和逻辑运算(包括单周期 32 位乘法)以及在单个指令中使用索引寻址执行 8、16 或 32 位数据传输。 这大大降低了所需的处理器时钟频率,并提高了单条指令的性能。此外,它减少了程序存储所需的内存和从内存中获取程序所需的功率。

降低的时钟频率意味着更低的噪声和更高精度的模拟,从而提高了器件的模拟传感器能力。射频应用也受益于电磁干扰的减少。这种效率提高了性能并提供了非常适合混合信号应用的低噪声、高精度模拟操作。

降低制造风险和硅面积

从高效的处理器设计中增加功能是一个很好的开始,但嵌入式设计人员还需要减少 SoC 面积并保留低成本、低风险的工艺节点。为了满足这一需求,越来越多的趋势是向主流的 180 纳米节点迁移。一些最激进的设计甚至以 110 纳米技术节点为目标,以缩小芯片尺寸。有几个因素促成了这一趋势:

已有 12 年历史的 180 纳米技术足够稳定,从 250 纳米技术迁移到 180 纳米技术几乎没有风险。

250 nm 节点不提供增值非易失性存储器组件,例如闪存和一次性可编程存储器。

新兴的利基工艺技术,如 180 超低泄漏 (ULL)、180 双极 CMOS DMOS (BCD) 和 110 ULL,凭借其低动态和泄漏功率曲线非常适合嵌入式市场。

优化物理 IP 以减少面积和功耗

面积减少直接导致芯片成本降低,再加上更低的功耗,可以实现更便宜的 SoC 封装并降低整体系统成本。此外,较低的动态和泄漏功率延长了电池寿命。ARM 可通过在 ULL 工艺上实施的物理 IP 平台降低芯片尺寸和功耗。

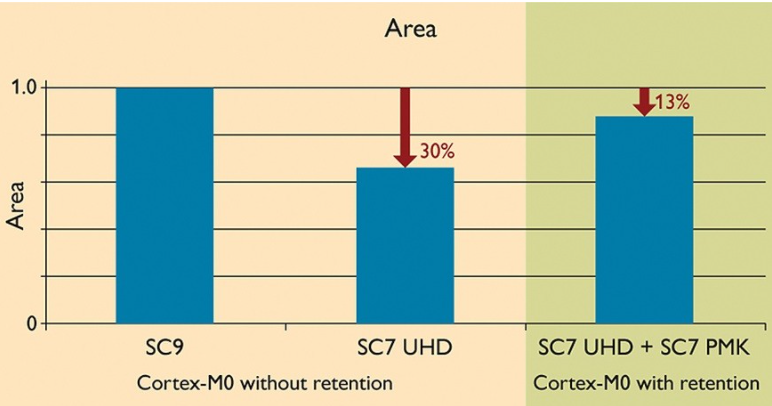

ULL 物理 IP 平台包含一系列逻辑产品:九轨 SC9 高密度 (HD) 标准单元库、无分接七轨 SC7 超高密度 (UHD) 标准单元库和七轨SC7 超高清电源管理套件 (PMK)。该平台包含全系列的存储器编译器,包括 HD SRAM、寄存器文件和 ROM。与 SC9 HD 磁带库相比,SC7 UHD 磁带库通常可节省高达 30% 的面积(参见图 1)。

图 1: SC7 超高密度库在 ARM Cortex-M0 上节省多达 30% 的面积。

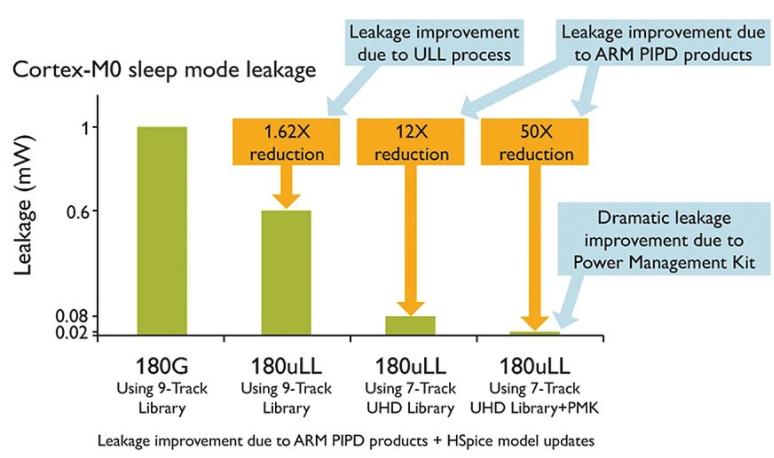

SC7 UHD 库可以与互补的 SC7 UHD PMK 配对,只需增加少量逻辑面积,就可以显着减少泄漏。例如,在实现 Cortex-M0 时,使用 SC7 的泄漏比使用 SC9 低 12 倍。当使用 SC7 UHD 库和 SC7 UHD PMK 实施时,Cortex-M0 的泄漏减少了高达 50 倍(参见图 2)。

图 2:使用 SC7 物理 IP 实现的 ARM Cortex-M 在睡眠模式泄漏方面最多可减少 50 倍。

嵌入式和混合信号设计的未来

随着创新的增加,嵌入式和混合信号市场将继续增长,以增加功能和差异化,同时降低成本。通过在未来的嵌入式设备解决方案中提供无与伦比的设计和效率,高效的嵌入式处理器和物理 IP 将有助于这些市场的增长。

ARM 32 位处理器带来更多功能和性能效率。在较小但风险仍然较低的工艺节点上实施的物理 IP 将保持较低的制造成本并减小裸片尺寸。ARM 的物理 IP 等优化解决方案可显着节省面积和漏电,从而降低总系统成本并延长电池寿命。

作者:Kimkinyona Fox,Raviraj Mahatme

审核编辑:郭婷

-

嵌入式学习快速提升之路--专业嵌入式解决方案提供2014-08-14 0

-

天嵌科技携多种专业解决方案参加第四届深圳嵌入式系统展2015-04-17 0

-

嵌入式内存测试方案2019-06-27 0

-

多核处理器SoC设计怎么才能满足嵌入式系统应用?2019-08-01 0

-

求AMD R系列与AMD SOC系列嵌入式高效能解决方案2021-05-10 0

-

怎样去设计汽车嵌入式SoC系统?2021-05-12 0

-

嵌入式系统设计2021-10-27 0

-

嵌入式系统是什么意思2021-10-28 0

-

SOC嵌入式相关资料推荐2021-11-01 0

-

大佬都在看的嵌入式系统解决方案2021-11-09 0

-

专门设计嵌入式主板有何应用2021-12-16 0

-

嵌入式设备的性能soc2021-12-20 0

-

什么是嵌入式系统?2021-12-22 0

-

嵌入式系统产品有多可靠?2022-11-16 0

-

基于Arm®技术的嵌入式控制解决方案分享2022-12-08 0

全部0条评论

快来发表一下你的评论吧 !