$unit声明空间

描述

| $unit是一个危险的共享名称空间,充满危险。它的使用会导致设计难以编译和维护。 |

| 下列unit代表$unit |

| 笔记 |

|---|

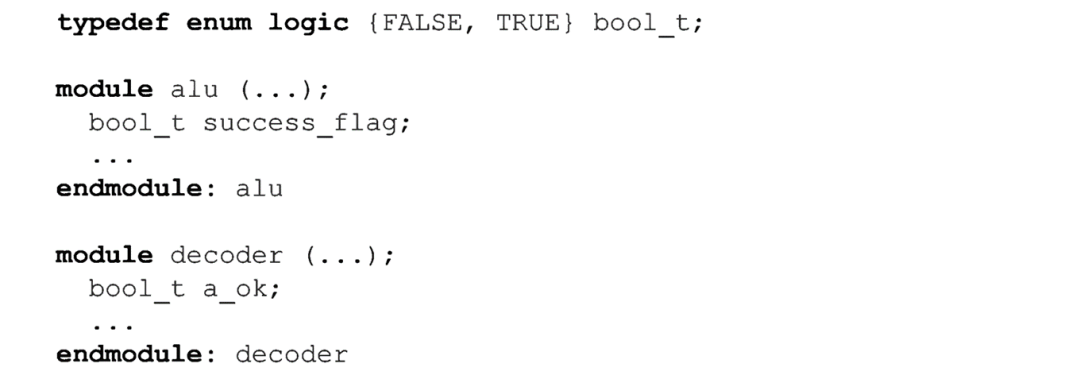

在将包添加到SystemVerilog标准之前,SV提供了一种不同的机制来创建多个模块共享的定义。这个机制是一个名为unit的伪全局名称空间,也称unit 编译单元或声明空间。声明空间之外的任何声明都在unit声明空间中。在下面的示例中,bool_t的定义在两个模块之外,因此在unit声明空间中。

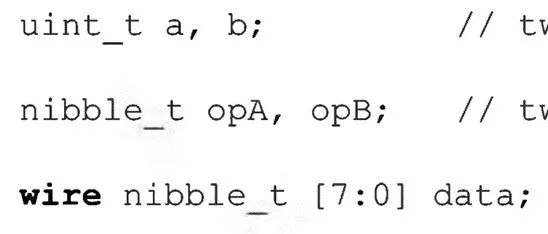

unit声明空间可以包含与包相同类型的用户定义,并且具有相同的综合限制。然而,与包不同的是,unit声明空间可能导致设计代码难以维护,EDA也难以编译。使用unit的一些危险包括

以unit声明空间的定义可能分散在许多文件中,使代码维护和代码重用成为一场噩梦,当引用包中用户自定义类型、任务、函数或其他标识符名称时,相对容易找到和维护标识符名称的定义。总是有一个显式的包引用或包导入语句来显示在哪里可以找到定义。当在unit声明空间中定义了用户自定义类型、任务、函数或其他标识符时,该定义可以位于构成设计和验证测试台源代码的任何文件、任何目录、任何服务器中。定位、维护和重新定义是困难的。

当unit声明空间中的定义位于多个文件中时,必须按照特定的顺序编译这些文件。

SystemVerilog要求在引用定义之前对其进行编译。当unit声明分散在许多文件中时,按照正确的顺序编译所有文件可能会很困难,甚至是不可能的。

更改unit定义需要重新编译所有源代码文件。

对unit声明空间中定义的任何更改都需要重新编译构成设计和验证测试台的所有源代码,因为任何地方的任何文件都可以无需导入地使用该定义。许多软件工具不会强制要求重新编译所有文件,但如果不重新编译,设计模块最终可能使用过时的定义。

对于仿真和综合,unit声明空间可以是相同,但通常是不同的。

编译器的每次调用都会启动一个新的unit声明空间,该空间不共享其他unit声明空间中的声明。许多SystemVerilog仿真器一起编译多个文件。这些工具将看到一个unit空间。一个文件中的unit定义对于单个编译中的任何后续文件都是可见的。大多数SystemVerilog综合编译器和一些仿真器都支持单独的文件编译,每个文件都可以独立编译。这些工具将看到几个断开连接的unit声明空间。一个文件中的unit定义对任何其他文件都不可见。

很容易出现定义不同的重复标识符名称。

在SystemVerilog中,在同一名称空间中多次定义同一名称是非法的。如果一个文件在unit声明空间中定义了bool_t用户自定义类型,而另一个文件在unit声明空间中也定义了bool_t用户自定义类型,那么这两个文件永远不能一起编译,因为这两个定义最终会在相同的unit空间中结束。为了避免这种冲突,工程师必须使用’define 和 ’ifdef添加条件编译指令,以便只编译编译器遇到的第一个定义。

包可以导入到unit中,但其危害与直接在unit中定义的危害相同。此外,必须注意不要将同一个包多次导入同一unit声明空间,这是非法的。

| 避免像Bubonic plague一样使用$unit!相反,使用包来共享定义。 |

| 包避免了$unit的所有危害,包提供了一个易于维护和重用的受控声明空间。 |

| 最佳实践指南4-2 |

|---|

审核编辑 :李倩

-

请问C2000共同体变量可以声明为外部变量吗?2018-06-14 0

-

DSP的存储空间分配说明2019-05-07 0

-

声明提前和函数的声明前置2019-07-08 0

-

请问485芯片的unit load是什么意思?2020-03-17 0

-

如何访问程序空间变量?2020-03-19 0

-

如何去使用AT声明2021-09-28 0

-

Pipeline and Control Unit Desi2009-07-27 689

-

HEV chargergenerator unit2009-11-28 457

-

什么是ACU (Automatic Calling Unit2010-02-22 654

-

什么是ADSL Termination Unit2010-02-22 628

-

Unit技术体系纲要2015-11-09 287

-

海明空间的二进制特征快速匹配算法2017-11-23 1088

-

unit_perf基于OpenWrt的性能检测工具2022-04-21 654

-

隐式函数声明会导致系统怎么样?2023-02-15 684

全部0条评论

快来发表一下你的评论吧 !