PCB layout中的走线设计

PCB设计

描述

PCB layout需要丰富的经验和扎实的理论基础支持,还要多踩几个坑,多做几个仿真加深对走线的理解,才能形成闭环的走线设计。

今天给大家介绍一个和GND走线相关的案例,在手机领域会影响相机画质、在医疗领域会影响生物电信号采集信噪比,如果不理解背后的原理,只会复制原理图或PCB的话,往往达不到电路的最佳性能。

地线在PCB走线中,通常有三种作用:

回流

控制阻抗

屏蔽

今天介绍的案例是和回流相关(本次讨论以低频为主),地线上的电压波动会影响到对噪声敏感的模拟电路。

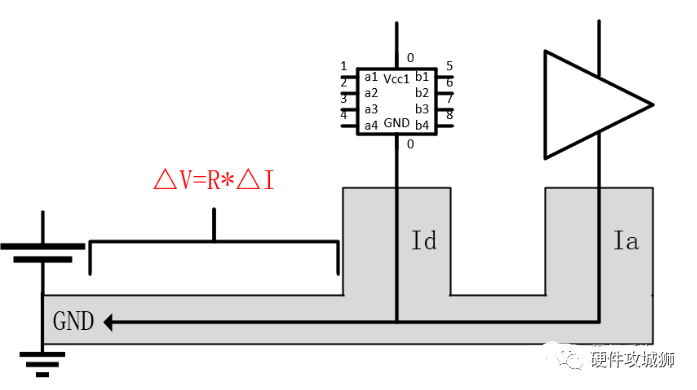

上图是一种地线走线示意图,数字电路和模拟电路的GND最终都要汇聚一起和电池的地连接。也就是说,数字电流Id和模拟电流Ia最终都要汇集在一起,那么这两路电流Id和Ia就用公用地线部分。

如上图括号内所示,一般而言,数字电流Id的波动是比较大的,而模拟电流Ia的波动略小。数字电Id的波动在共用地线部分会引起电压波动,这个波动就会被模拟电路感应到,进而引起信号质量下降,比如共用地部分的电阻是20 mΩ,而数字电流Id波动是1A,那么引起的电压波动△V就是0.02*1=0.02V,这个20mV被模拟电路的放大器感应到将会以噪声形式出现,这就是地线阻抗大的后果。

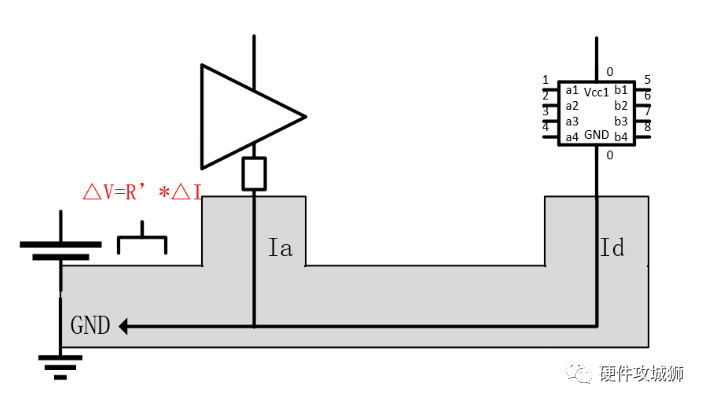

缓解的方法如下:减小地线的电阻,缩短模拟电路和数字电路共用地线,把模拟电路和数字电路通过磁珠隔离进一步压制干扰,假如数字电路电流波动不变,依然是1A,共用的地的电阻降低到2 mΩ,此时数字电路在共地部分引起的电压波动只有0.002*1=0.002V,比上面的20mV小了很多,同时,有磁珠的存在还会进一步压制这个噪声,提高模拟电路的信噪比或者是共模抑制比。

直观点说就是,不管你数字电路的地/电源怎么跳动,都影响不到我模拟电路的地/电源。

正是基于上面的介绍,所以一般电路板都会进行大面积的铺铜(大面积铺地平面,减小阻抗,增加回流能力),减少地的电阻。上面介绍的是地线的处理,对于模拟电路和数字电路共用电源的处理也是类似的方法(不过通常而言,不建议模拟电路和数字电路共用电源)。

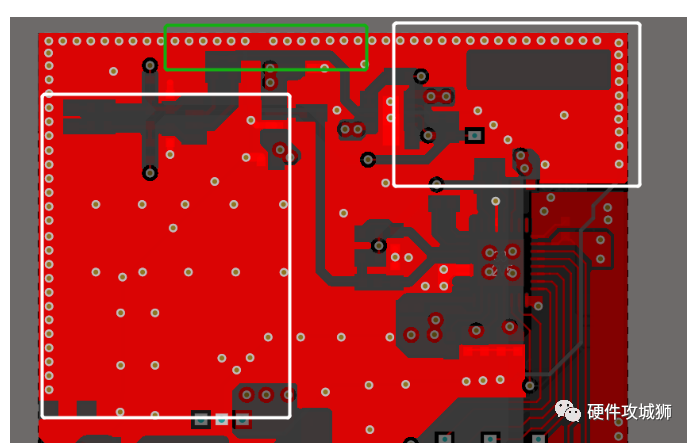

所以,有的人就不建议在地平面上打大量的其他电气属性的孔,或者是走线,这就是通常所说的支离破碎的地,这样容易增加地线的电阻(或阻抗),甚至是有隐藏的电阻瓶颈存在被工程师忽略而引起严重的问题。比如下图高亮的红色铜皮,两块白色方框内的铜皮看起来很大,其实他们的连接仅仅只有绿色部分窄窄的一条,这里就是阻抗瓶颈。

上面提到的仅仅只是直流电压波动,对于高频数字电路而言,电流的波动更复杂,含有非常丰富的电压或电流谐波,此时就要考虑频率这个参数了;围绕频率这个参数,就要考虑地线的寄生电容或寄生电感等参数。这在高端CPU中就格外重要,PCB走线要求更严格,这就是电源的PDN设计。

审核编辑:汤梓红

- 相关推荐

- 电路板

- 地线

- Pcb layout

-

[分享]PCB Layout中的走线策略2009-05-31 0

-

[原创]PCB Layout中的走线策略2009-08-20 0

-

PCB Layout中的走线策略2012-08-04 0

-

Pcb layout作品展2009-09-28 1086

-

PCB LAYOUT设计规范手册2010-11-01 2296

-

PCB和PCB LAYOUT相关词汇全解2011-11-09 3213

-

pcb layout基础学习2011-11-21 17044

-

PCB layout经验2016-05-03 830

-

PCB layout中的走線策略16页2016-12-16 796

-

PCB_layout教你如何使用ORCAD2017-09-18 1056

-

常用pcb layout软件有哪些2018-04-09 17131

-

PCB Layout设计规范你了解多少2019-08-19 11527

-

AD9148 PCB Layout Files2021-01-30 639

-

VersaClock 7 PCB Layout Guidelines 手册2023-01-10 236

-

为什么在PCB layout时不能走直角线2023-11-20 1232

全部0条评论

快来发表一下你的评论吧 !