PCB设计:传输线对整个电路设计的效应

PCB设计

描述

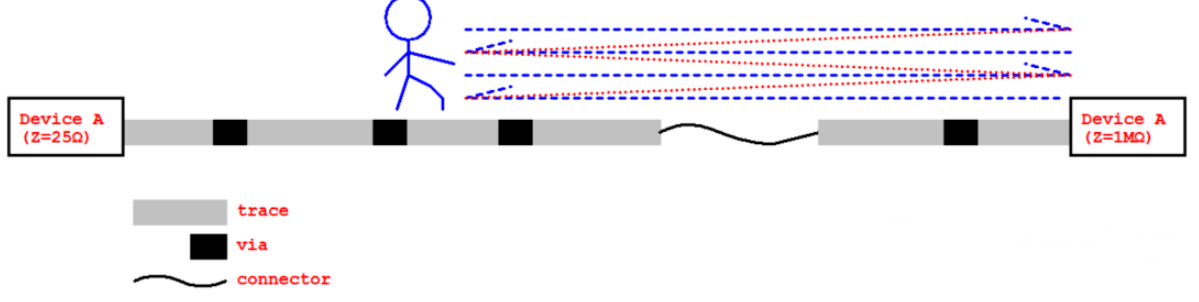

在高速线路中,由于传输线阻抗变化的问题,会有一部分的信号能量被反射,假设信号是一个跑步的人,人从A端想要跑到B端,在人经过线路每一块的导体时都会改变其电压值,一开始他在阻抗为50Ω的线路上跑,碰到过孔时阻抗的变化会产生让其速度变慢并产生一定的反弹,一直到终端为1MΩ时,此时几乎带着100%的能量被反弹回A端,反弹到A端时,由于A端为25Ω,会有一部分能量被留住,一部分能量被反弹,反弹的能量约为初始值的1/3。而这1/3的信号再次到达B端后,又会被反射,以此类推。在示波器上可以看到信号的上升沿和下降沿产生振荡直至能量减弱信号幅度随之减小。

基于上述模型,传输线会对整个电路设计带来一下效应:

反射信号、延时和时序错误、多次跨越逻辑电平门限错误、过冲与下冲、串扰、电磁辐射

信号轮廓失真

信号在接收端将被反射,信号轮廓将失真。失真变形的信号对噪声的敏感性、EMI若显著增加,这可能会造成整改系统的失效。

反射信号产生的主要原因:过长的布线、未进行阻抗匹配的接收端、未进行阻抗匹配的传输线(由于过量电容、电感的阻抗失配)

信号延时

信号在逻辑电平的高、低门限之间变化时,信号迟滞不跳变。过多的信号延时可能导致时序错误和元器件功能混乱,通常在多个接收端时会出现问题。

信号延时产生的主要原因:驱动过载、布线过长

信号电平错误

信号的振荡发生在逻辑电平门限附近,在跳变的过程中可能多次跨越逻辑电平门限,导致逻辑功能紊乱。

信号过冲与下冲

布线太长或信号变化太快都可以导致过冲与下冲发生,虽然大多数芯片器件接收端有输入保护二极管,但有时这些过冲电平会远远超过器件的电压范围,导致器件损坏。

信号串扰

在一根信号线上有信号通过时,与之相邻的信号线上会感应出相关信号,异步信号和时钟信号更容易产生串扰。

解决串扰的方法:移开发生串扰的信号或屏蔽被严重干扰的信号。信号距离地平面越近,或者加大线间距,都可以减少串扰的发生。

电磁辐射

电流流过导体会产生磁场。在电磁干扰(EMI)中,包括产生过量的电磁辐射和对电磁辐射的敏感性两个方面。数字系统处理快速的时钟和周期转换率,在系统运行时会向周围环境辐射电磁波,从而使周围环境中正常工作的电子设备收到干扰,而模拟电路,由于本身的高增益,会成为易受影响的电路。

EMI产生的主要原因是电路工作频率太高及布局、布线不合理。

编辑:黄飞

-

传输线效应2009-06-18 0

-

【快点PCB原创|大神带你学传输线理论】2016-09-09 0

-

避免传输线效应的方法有哪些?2017-06-08 0

-

基于高速PCB传输线建模的仿真2018-08-27 0

-

PCB传输线之SI反射问题的解决2018-09-21 0

-

高速电路传输线效应分析与处理2018-11-22 0

-

PCB传输线原理2018-11-23 0

-

一起讨论下传输线效应2018-12-24 0

-

毫米波的PCB平面传输线技术2019-06-24 0

-

如何应对高速PCB设计传输线效应?2021-03-02 0

-

什么是传输线?PCB的传输线结构是如何构成的?2021-06-29 0

-

PCB设计之实例解析传输线损耗2022-11-10 0

-

传输线效应详解2009-03-25 3449

-

如何减少传输线效应2009-04-07 1123

-

如何避免高速PCB设计中传输线效应2009-11-20 808

全部0条评论

快来发表一下你的评论吧 !