信号被上拉,但电平不是3.3V的原因

信号被上拉,但电平不是3.3V的原因

描述

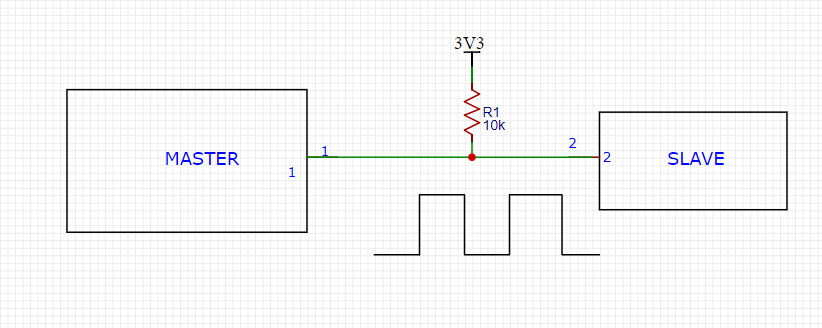

一般在芯片的GPIO口内部是开漏的状态下,外部需要连接上拉电阻,一般连接方式如下图,而且理想的高低电平应该是低电平电压值接近0V,高电平状态值在3.3V左右。

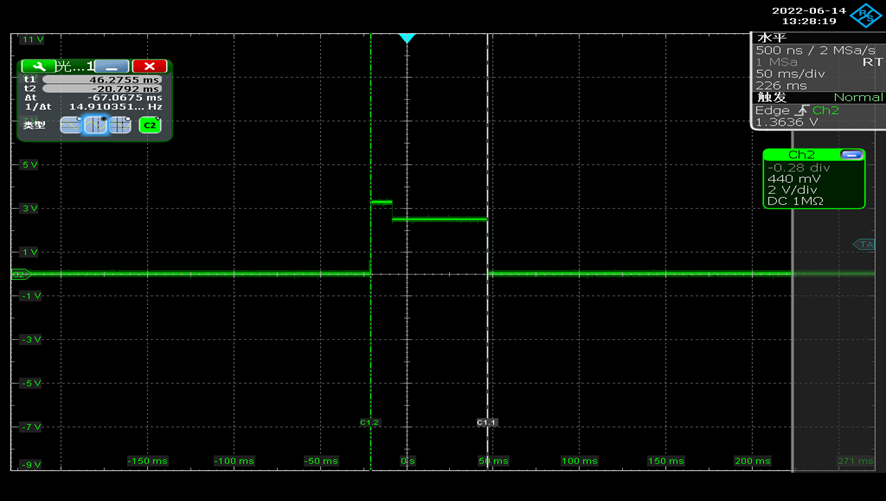

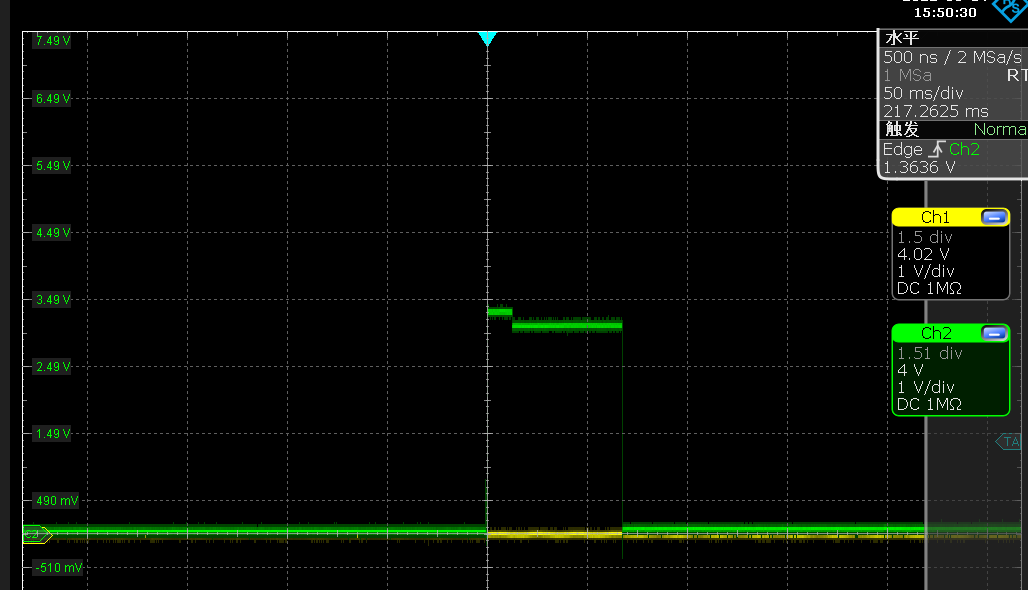

但是在这边实际测试的情况下却遇到一个问题:高电平状态电压先是3.3V,后面又被拉低到2.567V。

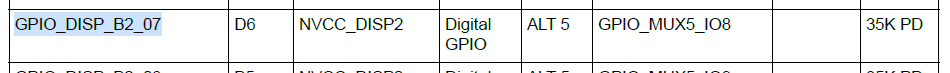

这个情况非常奇怪,开始被没有找到原因,直到翻看MASTER 芯片的规格书,发现它的这个GPIO口内部是有一个35K的下拉电阻的。

根据分压原理,35K的下拉电阻和10K的上拉电阻,中间的分压点电压计算就是3.3V*35/(35+10)=2.567V。理论分析对得上实际测试结果。

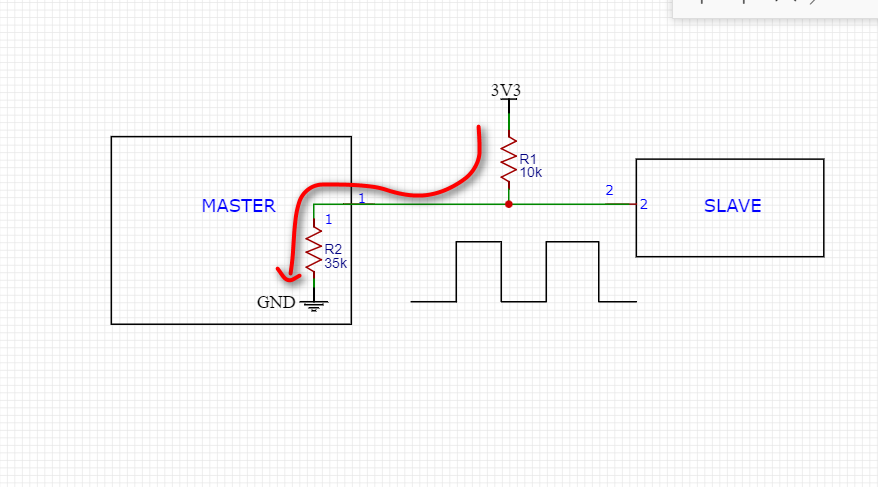

那么在这种情况下,预防高电平状态的电压阈值不够,就只能把上拉电阻值调小了,最后选择调整为2.2K。那么进行计算,分压点电压V=3.3V *35/(35+2.2) =3.1V。

那么3.1V的电压就没有什么风险了。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

GPIO在Open Drain Pull-up模式下不能输出高电平3.3V吗?2024-03-29 0

-

3.3V逻辑电平的LCD有哪些2013-12-30 0

-

请教控制电路信号12v,如何转为树莓派的信号3.3v2016-07-21 0

-

3.3V电平转5v电平失败2018-03-15 0

-

霍尔输出电压正常不是应为5V么,为什么会出现3.3V?2018-04-02 0

-

ADT7420的SCL电平被拉低2019-02-28 0

-

请问我给VDRV提供3.3的电压,是不是数字口就输出3.3v电压的数字电平?2019-06-14 0

-

3.3v转5v电平转换电路2020-09-02 0

-

ch552t 3.3v供电无法启动的原因是什么?如何处理?2022-06-02 0

-

怎样使用电平转换器将5V信号更改为3.3V信号呢2022-12-13 0

-

使用3.3v电源设置为高电平时GPIO(PB5) 输出为5V的原因?怎么解决?2022-12-26 0

-

3.3V电平和5V电平信号通讯必须要转换才能稳定吗?2023-10-18 0

-

3.3v的模块输出高电平,51识别不出来是高电平的原因?2023-10-24 0

-

AD5420与3.3V单片机连接进行SPI通讯时,为了进行3.3V电平通讯AD5420的DVCC脚是不是应该供电3.3V?2023-12-14 0

-

常见的电平转换方法2024-04-22 249

全部0条评论

快来发表一下你的评论吧 !