系统芯片设计之安全增强设计

电子说

描述

安全增强设计(Security Enhancement Design)是指采用特定的设计方法和技术来加强芯片的安全防护能力。安全防护涉及整个软硬件体系。与软件层面的安全技术不同,芯片的安全增强设计特指应用于密码芯片和片上安全系统的针对旁道攻击(又称侧信道或旁路攻击)的防御性设计。旁道攻击是指对密码算法的软硬件实现,以及其物理载体进行敏感信息获取的一系列攻击方法。

根据旁道信息源的不同,旁道攻击可以分为时间,功耗,电磁,声音,故障等攻击方法。这些攻击方法对芯片的安全功能构成了极大威胁。芯片是信息安全的基础设施,只有首先保障芯片自身的安全性才能真正为信息社会提供安全服务,实现身份认证,维护数据安全,构建可信,可靠的网络空间。

安全性增强设计依据三项基本原理对抗旁道攻击。1)随机化:通过一定措施将密码芯片的时间,功耗,电磁,声音等信息随机化,使得攻击者的数据统计与相关性分析过程发生巨大困难。2)盲化:通过数学和算法上的设计,使得攻击者缺少关键的额外信息,不能预知密码计算过程的敏感内容,从而无法进行相应的旁道信息分析。3)掩蔽:密码芯片通过产生随机数作为掩码,对密码运算的中间结果进行掩蔽,而运算的最终结果却可以正确恢复出来。掩码导致了中间结果具有很强的随机性,旁道信息的统计与分析难度因此急剧上升。

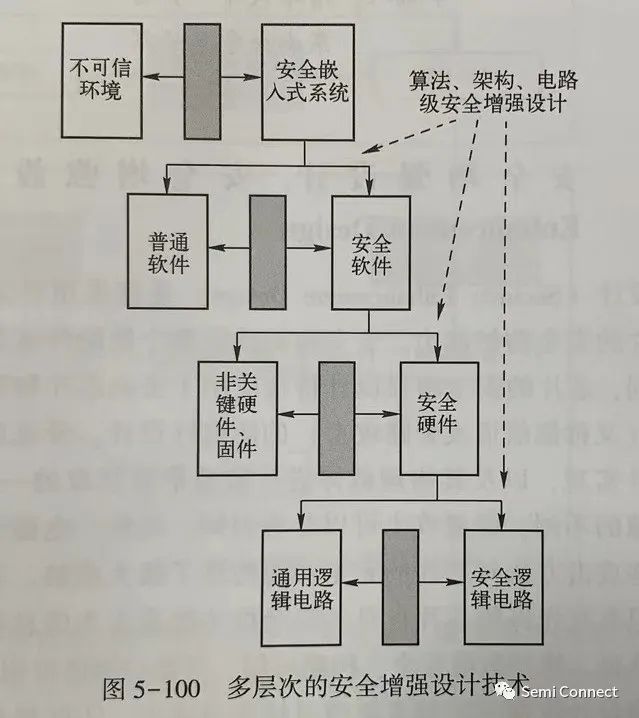

目前,算法级,架构级,电路级等多个层面的安全增强设计技术均得到了研究与发展。对于对称与非对称密码可以开发相应的抗攻击算法,从而在算法结构上对可能泄露的旁道信息进行消除与隐藏。抗攻击算法势必引入一定的冗余运算,这将导致密码芯片在性能与功耗上的额外负担。可以针对中央处理器与密码运算加速器的微架构进行安全增强设计,如通过修补微架构漏洞,添加安全指令与特殊硬件单元,能够对多种旁道攻击起到良好的抑制作用,另外,可以采用高安全性的新型逻辑电路,从根本上解决CMOS互补逻辑电路存在面积大,功耗高的问题,如何平衡攻击能力与实现代价也是重要的研究课题。如图5-100所示,实现芯片的安全增强需要系统性,跨层次的设计技术,从而在各个设计层次建立安全屏障,防止攻击者利用各个层次的漏洞和旁道信息威胁芯片核心部分的安全。

安全性增强设计的出现与旁道攻击技术的迅猛发展密切相关。20世纪90年代末,Paul Kocher 教授提出的差分功耗攻击方法在旁道攻击发展史上具有里程碑的意义。自此之后,学术界和工业界充分认识到密码芯片必须具备防御旁道攻击的措施和技术,从而催生了安全增强设计这一技术方向。英飞凌,恩智浦等公司在安全增强设计方面积累了雄厚的技术实力,已使其芯片产品具备抗攻击特性。近年来,中国在密码芯片的安全增强设计方面取得了很大进步,国内相关集成电路设计公司研制了具有一定防御攻击能力的智能卡芯片,在安全防护方面形成了相应的技术能力。随着互联网和物联网技术的蓬勃发展,网络空间安全问题日益凸显,芯片的安全增强设计的重要性也日渐突出。未来不仅集成电路设计单位,而且各类网络技术公司及互联网运营企业都将为提高芯片安全性这一重大课题贡献力量。

安全增强设计技术将继续向前发展,同时工业界将研制与完善面向芯片防护的全流程自动化检测设备与集成开发环境。全流程的安全增强设计将把各层次单点的关键技术集成为一个有机整体,实现效能最大化;同时注意硬件载体与软件环境的协同开发,提升自动化和智能化水平,保证良好的用户体验。

审核编辑 :李倩

-

安全芯片能否保证芯片安全?2009-10-10 0

-

面向食品安全的无线传感器网络系统设计2009-12-01 0

-

Bondout、增强型Hooks芯片和标准产品芯片2011-08-11 0

-

设计安全工业芯片系统的验证方法2013-11-20 0

-

高安全、高性能、高性价比 加密芯片 分享2015-11-30 0

-

法半导体和Fidesmo合作开发支付系统芯片整体方案,为可穿戴设备带来安全的非接触交易功能2018-10-23 0

-

WiFi Authentication WPA3 Encryption如何增强安全性2019-09-18 0

-

工业芯片系统的安全验证方法有哪些?2019-09-29 0

-

嵌入式系统有什么安全技巧?2019-10-18 0

-

如何采用FPGA芯片完成基于LMS算法的自适应谱线增强系统的设计?2021-04-29 0

-

有什么想法可以增强代码安全性吗?2023-04-18 0

-

借力传感器 主动安全系统增强预防性2010-02-10 442

-

借力传感器主动安全系统增强预防性2010-03-12 555

-

监控技术如何增强嵌入式系统的安全2023-09-15 334

全部0条评论

快来发表一下你的评论吧 !