芯片设计之Quarus 工具部分功能简介

电子说

描述

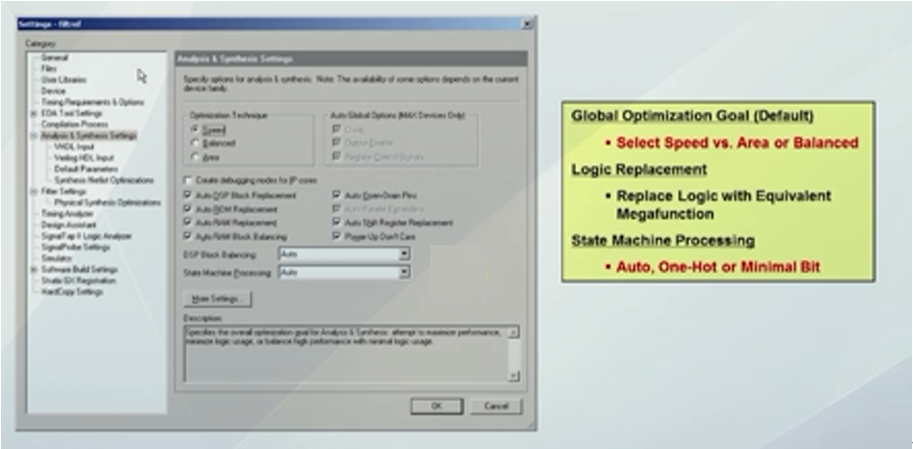

Quarus Ⅱ工具逻辑综合的选项设置窗口如图一所示,类似AISC逻辑综合过程中的约束步骤,设计人员可以通过Quarus Ⅱ工具采用适合的手段对PLD(可编程器件)进行约束和优化。

Quarus Ⅱ工具的约束包括三种:速度优先、面积优先、速度和面积平衡考虑。

Quarus Ⅱ工具可以使用宏单元进行逻辑优化,该宏单元是可编程器件生产商设计完成的固定模块如加法器、乘法器等。上述宏单元的效用优于设计人员自主编写的代码,Quarus Ⅱ工具会从设计人员自主编写的代码中自动提炼出与宏单元有相同功能的代码,并采用宏单元替换上述代码。

Quarus Ⅱ工具中,有限状态机(是一种用来进行对象行为建模的工具,作用是描述对象在其生命周期内所经历的状态序列,以及如何响应来自外界的各种事件)的状态编码(个人理解:对有限状态机的各种状态的编号)有三种方式:Auto(自动选择方式)、One-Hot(根据网络资料理解:一位有效方式,通过将编码中"1"左移编号,如010的下一个编号是100,而不是011)、Minimal Bit(个人理解:占用最小空间的方式)。

如果芯片设计代码的有限状态机未采用明确的状态编码方式,计算机会自动选择合适的状态机编码方式,提高编码效率。

图一,图片来源:学堂在线《IC设计与方法》

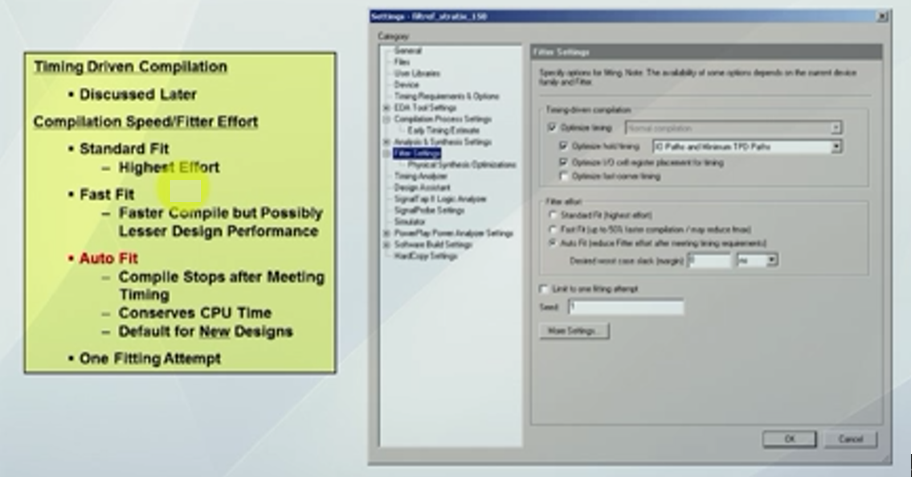

布局布线可以采取几种不同的方式。在初期设计过程中,需验证设计功能是否正确,不需过多考虑芯片的效率,可以选取快速布局的方式,1小时可以完成布局布线。当设计功能调整完成,需要采用紧凑的设计实现更优的性能,可以选取标准布线方式,使设计达到最好的布局布线效果。

图片来源:学堂在线《IC设计与方法》

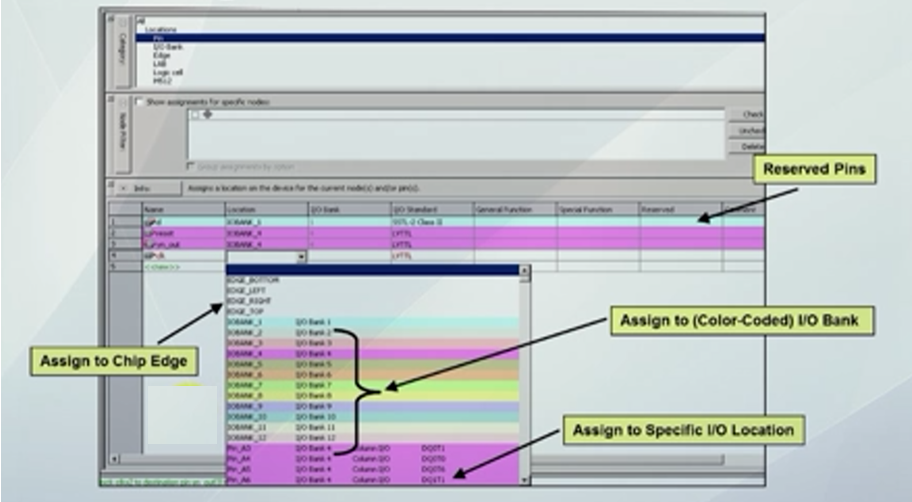

IO引脚指定需要注意:

(1)通常会将数据总线的八位或十六位分布在同一方向,以使引脚位置可以处于芯片同一侧,且不给某一引脚指定具体名字。这种方式可以增加布局布线的灵活性,使布局布线实现线长最短、性能最好。

(2)在复杂芯片中,IO引脚可能会有多个Bank(根据网络资料,个人理解为具有相同特征的一组输入输出信号)。每个Bank中的供电电压和驱动方式等相同,也可以增加布局布线的灵活性。

图片来源:学堂在线《IC设计与方法》

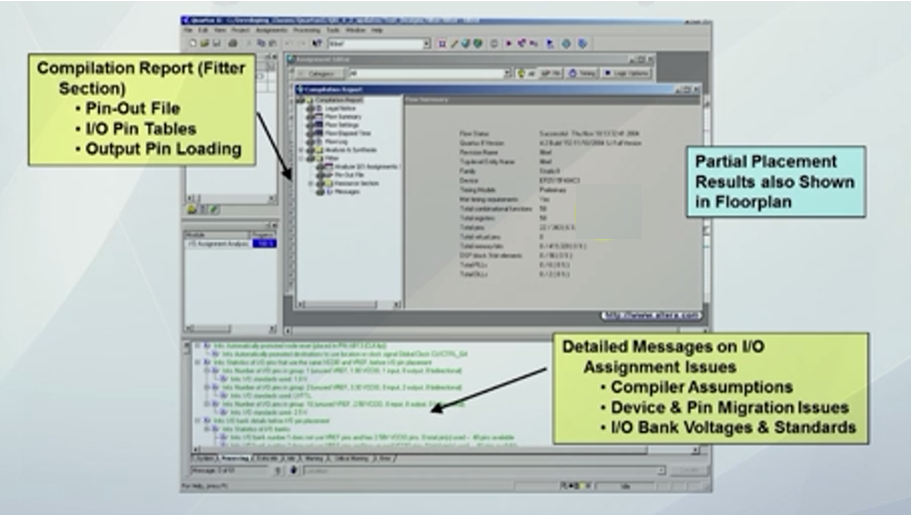

通常,IO引脚指定完成后,需进行IO引脚指定分析。需进行IO引脚指定分析的原因:可编程器件的一些IO引脚具有特殊功能,如时钟专用引脚、复位信号专用引脚、存储器相关引脚等,设计人员需要分析特殊引脚功能是否与所设计的IO引脚指定是否有冲突,并避免冲突。

图二展示了IO引脚指定分析结果,在分析结果中给出详细的IO分配表,IO分配表可用于后续PCB(印刷电路板,个人理解芯片实现具体功能所需的电路板)布线工具分析。除此之外,IO引脚的相关分析文件、相关输出引脚的负载等信息均可以在相关窗口中获取。

图二,图片来源:学堂在线《IC设计与方法》

审核编辑 :李倩

-

英飞凌强大的AURIX和工具链简介2018-12-14 0

-

Py之cython:python库之cython的简介、安装、使用方法之详细攻略2018-12-19 0

-

Py之neurolab:Python库之neurolab的简介、安装、使用方法之详细攻略2018-12-20 0

-

ETH之Solidity:Solidity的简介、安装、使用方法之详细攻略2018-12-21 0

-

常见的图片标注工具labelImg的简介、安装和使用方法2018-12-25 0

-

芯片设计流程及工具2020-02-12 0

-

LEDA工具简介2021-07-27 0

-

EXTI简介及功能框图2021-12-15 0

-

Labview2013各工具包的功能简介2015-11-20 1078

-

ZYNQ PS部分简介2021-12-22 183

-

JSON工具简介及安装使用方法说明2022-05-25 3287

-

电气过应力简介-第 3 部分2022-11-04 283

-

电气过应力简介-第2部分2022-11-04 243

-

电气过应力简介-第1部分2022-11-04 369

-

L298N芯片产品功能简介2023-10-18 231

全部0条评论

快来发表一下你的评论吧 !