DDS信号发生器的理解与实现

描述

基于Verilog的DDS波形发生器的分析与实现(三角波、正弦波)

最近学习了一下关于DDS的相关知识,本篇概要记录一下自己的理解与实现。

DDS信号发生器采用直接数字频率合成(Direct Digital Synthesis,简称DDS)技术,把信号发生器的频率稳定度、准确度提高到与基准频率相同的水平,并且可以在很宽的频率范围内进行精细的频率调节。采用这种方法设计的信号源可工作于调制状态,可对输出电平进行调节,也可输出各种波形。

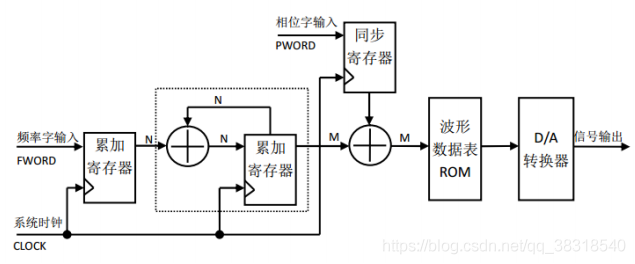

下图为DDS 的基本结构图

由上图 可以看出,DDS 主要由相位累加器、相位调制器、波形数据表以及 D/A 转换器构成。

相位累加部分控制输出波形频率,相位字输入部分来改变相位,ROM表中存储一个周期波形的幅度值。

其中相位累加器由 N 位加法器与 N 位寄存器构成。每来一个时钟,加法器就将频率控制字与累加寄存器输出的相位数据相加,相加的结果又反馈至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。即在每一个时钟脉冲输入时,相位累加器便把频率控制字累加一次。相位累加器输出的数据就是合成信号的相位。相位累加器的溢出频率,就是 DDS 输出的信号频率。(解释:定义一个N位寄存器,一般为32位,如果来一个时钟计一次,那就要计2^32次才满,这样太慢,因此引入频率控制字设为A,以前以1为单位,现在以A为单位计数累加,可以控制计数更新的速度)

用相位累加器输出的数据,作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换。波形存储器的输出送到 D/A 转换器,由 D/A 转换器将数字信号转换成模拟信号输出。

一般32位累加器不会全用来输出作为ROM地址,会根据ROM深度来适当截取高位作为地址,其余位可以作为控制频率。例如现在ROM中存储波形一个周期数据每个数据位宽8位,则数据范围为0-2^8(256),但是要产生一个周期波形需要512个,因为0-256一般是上升期,256-0处于下降期,那么现在ROM深度为512,则地址位宽应为9位,2的9次方=512,则32位累加器只需高9位即可[31:23]寻址,其余位用来控制地址改变的频率。假如现在每来一个时钟地址变一次,那么其余位(即频率控制字A)应设置为32‘h800000即32’b0000_0000_10000000_0000_0000_0000_0000,最高位1其实就是地址的最低位,累加器初始为0,来个时钟沿加一次A,高9位地址变化一次。要想两个时钟变化一次,那么A就是32‘b0000_00000100_0000_0000_0000_0000_0000,两个时钟之后地址的最低位才会变化。这样通过对频率控制字A的设置就可以达到改变地址的变化频率,其实就是输出的频率。不知道这样说看者能否理解。

这里相位累加器位数为 N 位(N 的取值范围实际应用中一般为 24~32),相当于把正弦信号在相位上的精度定义为 N 位,所以其分辨率为1 /2。 若 DDS 的时钟频率为

-

基于DDS的信号发生器设计2016-01-11 835

-

DDS信号发生器2014-04-15 0

-

DDS信号发生器资料集汇2015-06-23 0

-

基于ALTERA实现的DDS信号发生器设计2017-05-12 0

-

基于FPGA的DDS信号发生器2019-03-18 0

-

基于 DDS 原理,应用 FPGA 开发 信号发生器2020-10-13 0

-

如何利用FPGA设计DDS信号发生器?2021-04-09 0

-

如何利用FPGA和DDS技术实现正弦信号发生器的设计2021-04-28 0

-

怎么利用FPGA设计基于DDS的信号发生器?2021-05-06 0

-

怎么实现基于FPGA+DDS的正弦信号发生器的设计?2021-05-11 0

-

DDS直接数字频率合成器、信号发生器、函数发生器2022-03-24 0

-

基于DDS技术的信号发生器研究与实现策略2010-04-23 2265

-

信号发生器原理_DDS芯片及应用_DDS信号发生器设计2015-06-23 7108

-

DDS多波信号发生器的实现2016-11-22 853

-

基于FPGA 的DDS正弦信号发生器的设计和实现2024-03-24 67

全部0条评论

快来发表一下你的评论吧 !