PCI总线信号及功能说明

接口/总线/驱动

描述

PCIe总线是继承了PCI总线而设计而来的,理解PCIe总线先从学习PCI的知识切入。PCI(Peripheral ComponentInterconnect)总线的诞生与 PC(Personal Computer)的蓬勃发展密切相关。在处理器体系结构中,PCI总线属于局部总线(Local Bus)。局部总线作为系统总线的延伸,主要功能是为了连接外部设备。

PCIe不同于以前的IO总线,采用的是串行,点到点的互连方式来实现两个设备之间的通信是和传统的PCI及PCI-X有相似的地方。PCIe保持了与传统PCI相同的存储器,IO和配置地址空间模型,在软件上向后兼容传统的PCI系统。

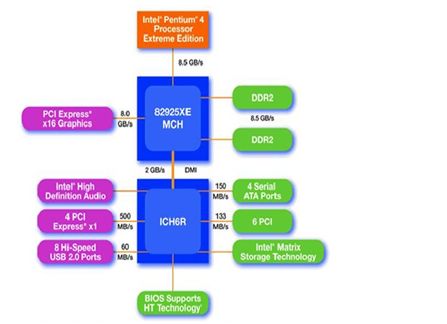

下图展示在PC中各PCIe互联:

1、PCI架构综述

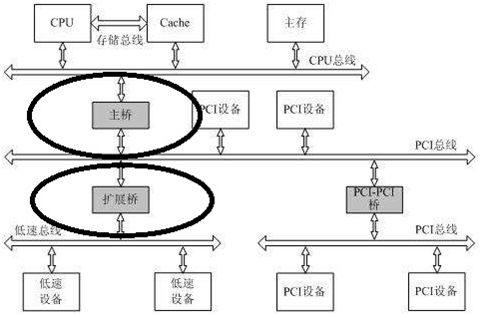

基于PCI总线的平台如图所示:

该平台主要由FSB,PCI和ISA组成,其中FSB是处理器子系统总线,PCI总线,ISA是各种IO扩展总线。其中图片中圈1是主桥,也就是北桥;圈2是扩展总线桥,也就是南桥。

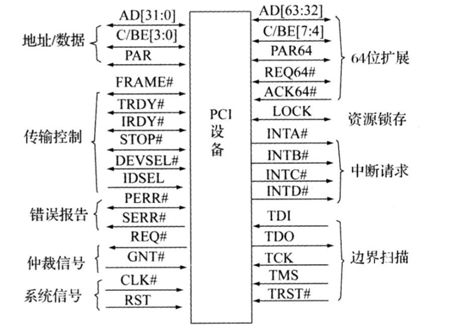

2、PCI总线信号及功能

PCI的总线信号如图所示:

信号功能如下:

地址/数据

AD[31:0]:地址,数据复用引脚,一般是先发送地址,后发送数据。可以表示32为的物理地址,也可以表示32为的有效数据。

C/BE[3:0]:总线命令和字节使能复用引脚,其中在地址期间,表示事务总线的类型;在数据期间,表示表示字节的使能。

PAR:是AD[31:0]和C/BE[3:0]#的偶校验位。

传输控制信号

主要表示PCI总线上设备的工作状态,根据英文含义可以知道对应的功能,其中IDSEL是PCI设备的配置空间片选信号,在CPU访问PCI设备时候进行配置。

仲裁信号

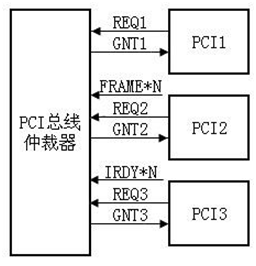

REQ#:是主设备对PCI设备的仲裁信号;

GNT#:是从设备对主设备信号的响应信号。

报错信号

PERR:特殊的场景外的所有PCI事务的数据奇偶检验报告;

SERR:一般有三种错误,包括地址奇偶检验错误,数据奇偶检验错误和其他严重的错我。

系统信号:

包括时钟信号和复位信号

中断信号:

64位总线扩展信号

总线将之前的32位宽扩展为64位,为配合这一扩展而加入的一组新的信号。

3、PCI总线的事务类型

根据信号C/BE[3:0]的编码,PCI可以实现的事务类型的命令如下图所示:

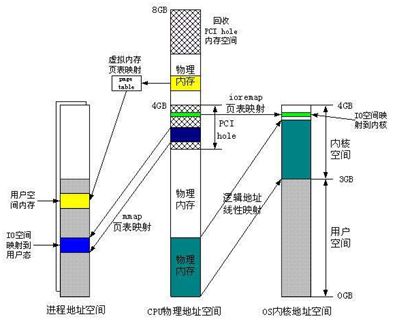

4、PCI地址空间映射

5、PCI典型的读写事务

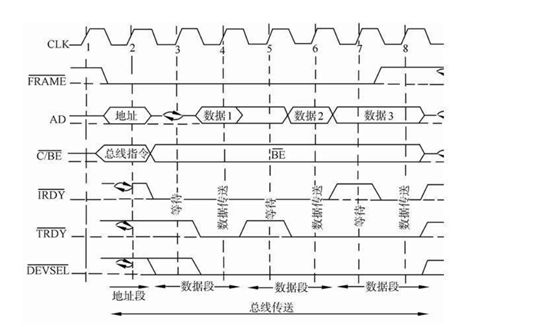

下图展示一个典型的PCI读写事务,以一个地址相开始,由一个地址相和多个数据相组合形成。

主设备在最后一个数据相,且IRDY为肯定时,向目标表明这是本事务的最后一个数据相。最后一个数据的传输取决于TRDY信号。

6、PCI总线的仲裁

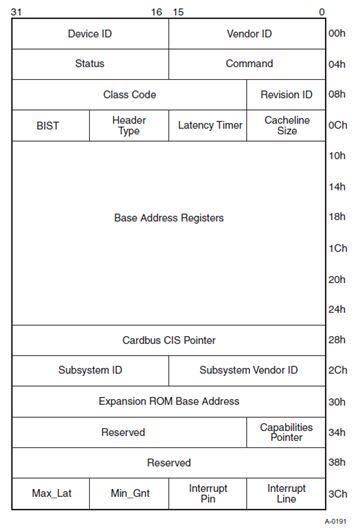

7、PCI的头标0/1配置寄存器

配置寄存器是PCI设备的硬件与PCI设备的初始化软件及错误处理软件的信息的交接区,实时的反映PCI设备的状态和要求。

因为寄存器地址位宽并不是32bit,所以在这里引入registernumber的概念。

8、IC验证工程师需要验证的点

根据不同版本的PCIe验证不同的建链速率,PCIe的建链速率向下兼容(比如3.0支持8G建链,向下兼容支持2.5G和5G).

PCIe的寄存器访问,在不同的投标区域;

PCIe的复位验证,分别是冷复位,热复位,暖复位。

PCIe的配置验证,包括IO,CFG,MEM,MSG验证;

PCIe三种包格式的确定;

PCIe的电源管理模块验证,包括各状态的验证及状态机跳转;

PCIe畸形包的注入是否和预期的一致;

PCIe的PHY(PCS and PMA)和DMA功能验证;

对于部分功能需要通过VIP中的callback进行验证。

-

PCI总线特性及信号说明2012-04-06 0

-

基于DSP和PCI总线的通用数字信号处理系统2018-12-17 0

-

基于PCI总线的CPLD实现2019-05-29 0

-

PCI总线的信号是如何去定义的2022-02-16 0

-

PCI总线接口芯片PCI9054及其应用2008-10-09 7698

-

iPVD的功能说明及介绍2008-10-27 1849

-

基于PCI总线数字信号处理机的硬件设计2009-03-30 578

-

基于FPGA的PCI总线接口设计2009-06-20 964

-

74HC573功能说明2016-03-23 1292

-

基于PCI总线的信号定义2021-07-18 2033

-

简述PCI总线的中断机制2021-07-18 2501

-

六码流水遥控器功能说明2022-03-07 372

-

ZSC31050功能说明2023-02-02 174

全部0条评论

快来发表一下你的评论吧 !