详解ZYNQ启动的过程

描述

ZYNQ启动是由ARM引导FPGA,以及用户程序的加载。

预配置阶段

Pre-configuration stage

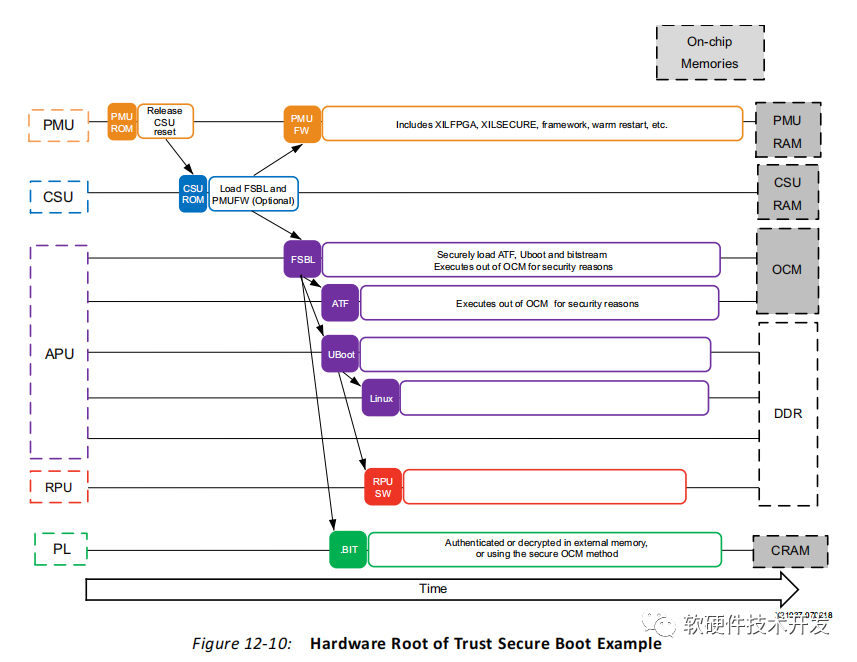

1. 通过上电复位(POR),将PMU(平台管理单元/Platform Management Unit)从复位状态唤醒,提供如下操作:

复位低压域LPD寄存器

复位全电源域FPD寄存器

复位PMU的RAM

复位PMU处理器的TLB内存

检查LPD、AUX、专用IO等区域电压

复位CSU、LPD、FPD的内存区

2.执行PMU ROM中的预启动代码,以执行复位操作(包括配置安全单元CSU)复位),该阶段结束的标志是CSU复位的释放。 预启动代码进行的初始化操作:

初始化PS Sysmon单元和启动所需要的PLL

清除PMU RAM 和 CSU RAM区域

验证PLL锁

利用PS Sysmon验证LPD、AUX、I/O的范围

清除低压域(LPD)和全电源域(FPD)

配置阶段

Configuration stage

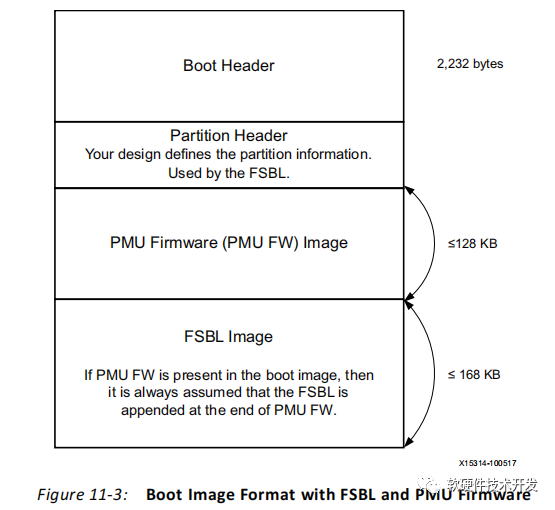

CSU复位后,初始化OC-RAM,将FBSL加载到OC-RAM(on-chip RAM),CSU加载PMU用户固件(PMU FW:firmware)到PMU RAM,若没有则不加载。

在ZYNQ上运行程序的时候,Boot Rom直接固化在硬件中,开发者无法修改。FSBL(first stage boot loader)是第一阶段的加载程序,经过这个阶段,后面系统才能够运行裸奔程序或者是引导操作系统的u-boot。用户可以选择用cortex-a53制作启动的FSBL文件,也可以选择用cortex-r5来制作启动的FSBL文件。

处理器开始执行FSBL代码。FSBL(first-stage boot loader)的作用如下:

1.初始化PS端配置,如:MIO、PLL、DDR、QSPI、SD等。

2.加载PL端程序,即:加载bitstream

3.搬运用户程序到DDR,并跳转执行。

PCAP(处理器配置访问端口processor configuration access port)用于从PS配置PL。PCAP是在正常操作条件下用于配置PL的唯一接口。在调试过程中,可以使用JTAG接口来配置PL。PS通过secure-stream switch连接到PCAP。可以使用CSU DMA或AES路径将比特流数据发送到PL。

FSBL使用PCAP接口为PL配置比特流,步骤如下:

1.初始化PCAP接口。

2.通过PCAP写入比特流(Bitstream)。

3.等待PL完成状态。

后配置阶段

Post-configuration stage

FBSL执行后,CSU ROM代码进入Post-configuration阶段,负责起系统干预响应,提供硬件支持。PMU仍然需要运行,用于后续改变系统的电源状态(上电、睡眠、唤醒等等)。这个阶段会启动SSBL,就是Linux的bootloader,开始引导启动Linux系统。

审核编辑:刘清

-

Zynq在非JTAG模式下的启动配置流程2021-01-08 0

-

Zynq的启动与配置过程详解2021-01-26 1372

-

s3c2440启动过程详解2012-08-20 0

-

玩转Zynq连载1——Zynq的linux启动过程2019-04-16 0

-

STM32F429启动过程详解2021-08-03 0

-

STM32H7启动过程详解2021-08-03 0

-

Linux启动过程详解2021-11-02 0

-

Linux基础命令之Linux启动过程详解2017-10-18 912

-

详解zynq的启动步骤2019-10-27 7079

-

浅谈zynq启动,BootROM和FSBL等的执行过程2020-11-23 8556

-

ZYNQ开发双核运行原理及过程2020-12-05 5530

-

ZYNQ 的启动流程介绍2022-07-22 5730

-

详解Zynq的两种启动模式2023-08-02 847

-

RL78启动过程详解2023-09-28 908

-

stm32启动过程详解2023-12-08 792

全部0条评论

快来发表一下你的评论吧 !