快速原型设计帮助实现ISR任务的最佳DSP系统

描述

面对快速发展的威胁,国防部可以寻求基于 COTS 的快速原型设计,实现经济高效的高性能数字信号处理系统,以满足情报、监视和侦察 (ISR) 操作的严格尺寸、重量和功率 (SWaP) 限制和任务目标。

现代战争迫使美国军方迅速适应快速演变的不对称威胁,以保持美国军方的战术态势感知能力。然而,传统上对由专用集成电路 (ASIC) 和专用标准产品 (ASSP) 组成的定制烟囱式数字信号处理 (DSP) 系统实现的依赖限制了美国军事情报、监视和侦察 (ISR) 操作的敏捷性。

为了应对这些限制和不稳定的威胁,美国国防部正在越来越多地资助ISR快速反应能力(QRC)。然而,这种新的采购模式要求战术ISR系统开发人员快速制作具有成本效益的高性能DSP系统原型,同时满足严格的尺寸、重量和功率(SWaP)计划要求。为了满足这些需求,一种新颖的快速原型设计方法利用COTS硬件/软件信号处理技术和成本建模来缩小数据收集/分析差距,挫败传统ISR设计方法的局限性,减少开发时间和费用,同时满足具有挑战性的ISR任务要求。

缩小ISR任务情景中的收集-分析差距

在过去几年中,对ISR能力的需求增加导致数据收集能力呈指数级增长,并将在可预见的将来继续这样做。然而,ISR 数据处理、利用和传播 (PED) 流程在同一时期仅线性改进,在收集和分析能力之间留下了关键的差距。为了缩小收集与分析的差距,国防部需要基于DSP的高性能ISR系统,该系统能够自动、实时地处理大量数据,并将可操作的情报直接传播给战场上的作战人员。

实时、自动化 PED 等高端 ISR 应用突破了最先进的 COTS DSP 技术的极限。吞吐量要求可能超过数十 tera 操作/秒。新的众核图形处理单元(GPU)和通用处理器(GPP)架构在理论上似乎能够满足这种高端性能要求。然而,开发并行软件算法以充分利用多核架构峰值性能的一小部分是一项极其艰巨的任务。

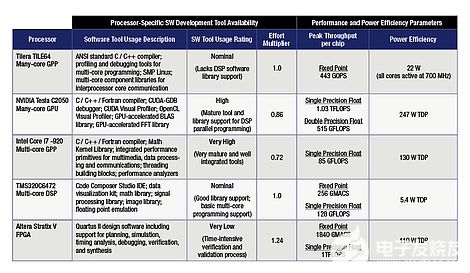

在严格的SWaP约束下满足如此极端性能要求的具有成本效益的系统实现的快速原型设计是一项艰巨的任务。在前端设计过程中进行详细的权衡分析和广泛的架构探索对于实现这一目标至关重要。表 1 显示了众核 GPU、多核/众核 GPP、多核 DSP 和现场可编程门阵列 (FPGA) 技术在处理器专用软件工具可用性、处理器峰值吞吐量和能效方面的比较。特定于处理器的软件开发工具的成熟度对系统开发工作、成本和进度有重大影响。系统开发人员必须在软件工具支持的成熟度与硬件性能和能效之间做出最佳权衡,以满足高端 ISR 应用要求。

表 1:系统开发人员必须在软件工具支持的成熟度与硬件性能和能效之间做出最佳权衡,以满足高端 ISR 应用要求。

传统 ISR 设计方法的局限性

当今的大多数ISR系统都遵循“瀑布式”开发方法,该方法规定了顺序过程。目前高性能ISR系统的瀑布式设计流程施加了许多限制,包括:

有限的建筑探索

漫长的原型制作时间

设计成本高

缺乏系统的硬件/软件重用

循环硬件制造和测试

大多数设计自动化活动都专注于利用工具支持进行详细的系统行为设计,而不是早期架构设计,其中大部分系统成本都已投入。目前的工业实践主要依靠设计人员的经验来选择系统架构和分配算法功能。此外,对于完全定制的ISR系统,硬件和软件子系统直到硬件制造后才会集成,这使得设计错误的成本非常高昂。

接地气的创新:基于 COTS 的快速原型设计

ISR 系统开发成本超支和进度延迟频率的增加迫使国防部采购社区推出许多计划,鼓励承包商社区更好地利用 COTS DSP 硬件板和系统组件。

然而,在基于COTS硬件的系统中,软件开发的时间和成本可以主导进度和预算。基于历史项目数据的参数化研究表明,如果处理器和内存资源的松弛幅度限制太大,设计和测试嵌入式软件尤其困难。严重的资源限制可能会阻止嵌入式软件开发人员利用高级编程工具,从而需要与硬件和/或操作系统直接交互以优化代码以满足系统要求。

一个在业界引起关注的创新解决方案是快速原型设计方法,该方法利用 COTS 硬件/软件信号处理技术和成本建模的使用,显著降低 ISR 系统的总成本和开发时间。这种方法利用了基于 COTS 库的优化框架,该框架包括吞吐量、硬件/软件开发成本以及进度、采购成本和 SWaP 之间的权衡。这种快速原型设计方法可在前端设计过程中最大限度地探索系统架构。由此产生的解决方案是经济高效的DSP嵌入式系统,利用众核GPU、多/众核GPP、多核DSP和/或FPGA技术的灵活性,同时满足任务目标规定的严格SWaP约束。

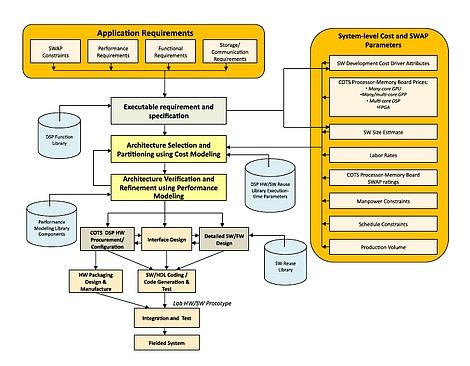

图1所示为基于COTSP的快速DSP系统原型设计方法。该过程首先使用信号处理库和集成的图形用户界面(GUI)工具包(如MATLAB中提供的工具包)将书面系统需求转换为可执行的需求和规范。可执行的要求和规范为客户提供了一个早期的原型,以验证原始要求并消除歧义。这种反馈允许尽早收到任何需求变更,这对于最大限度地降低需求蔓延的高成本至关重要,这是软件项目中最常见的风险之一。

图 1:基于COTS的快速原型设计方法优先考虑应用需求和成本建模,这对于最大限度地降低需求蔓延的高成本至关重要。

在验证系统要求、系统级成本参数、应用要求和性能统计信息后,这些组件为架构选择和分区优化过程提供依据。系统开发人员可以使用参数化成本模型(如 COCOMO II)来驱动架构权衡分析,从而生成硬件/软件架构候选方案,从而最大限度地降低总系统成本和开发时间。成本参数包括:软件成本驱动因素属性(大小、产品、平台、人员和项目)、COTS 硬件采购成本、产品部署期限、进度约束以及人工成本和约束。应用程序要求包括 SWaP、环境、优先级和实时约束,以及功能、内存和通信要求。性能统计数据包括在重用库中包含的 DSP 处理器板(例如,众核 GPU、多核/众核 GPP、多核 DSP、FPGA)上执行的 DSP 基元(例如,快速傅里叶变换)的基准时间测量值。

然后,系统开发人员可以使用动态性能建模工具(如 Simulink)模拟生成的架构候选项,以验证架构是否满足系统级要求。在性能建模之后,系统架构师将通信开销参数(如通信排队延迟和瓶颈)反馈到体系结构选择阶段进行优化。该方法使用更新的模型参数生成新的架构候选项,并重复该过程,直到架构满足性能要求,并且在连续迭代之间不再发生变化。

经过优化的硬件/软件架构候选者将进入详细的架构设计阶段,以进行详细的软件和/或固件设计,硬件/软件接口设计和COTS采购。根据所选的 COTS DSP 硬件平台和架构,DSP 软件和/或固件设计过程在很大程度上利用了以前项目中开发的可重用库。评估、选择、同化和修改可重用组件的成本也必须降至最低,以显著降低软件开发费用和时间。系统设计人员可以改进候选架构的性能模型和可执行信号处理算法规范,以允许自动将代码生成为C编程语言或硬件描述语言。为了能够使用自动代码生成工具,目标DSP板架构必须有足够的硬件资源松弛裕量和高级软件工具支持。

系统的高级虚拟原型使系统设计人员能够在设计过程的早期发现硬件/软件集成错误。这种方法允许在昂贵的硬件封装组装和现场测试之前识别和纠正低级性能限制。

快速原型设计帮助 ISR 系统跟上步伐

ISR系统的传统DSP实现已无法再跟上现代战争的步伐。系统开发人员需要一种快速原型设计方法,利用 COTS 硬件/软件信号处理技术和成本建模的使用,从而显著降低 ISR 系统的总成本和开发时间。艾维希斯科技的实时智能分析方法充分利用了这种基于 COTS 的快速原型设计方法。前端设计过程通过结合软件成本和开发时间模型实现自动化。设计优化过程将开发时间和成本减少了四倍。基于IvySys COTS的快速原型设计方法使国防部和情报界能够快速适应快速发展的不对称威胁,从而保持美国的战术态势感知能力。

审核编辑:郭婷

-

ARM快速嵌入式系统原型设计下载地址2018-07-04 0

-

用户界面原型设计2019-04-29 0

-

VxWorks多DSP系统多任务程序设计方案2019-06-27 0

-

采用VxWorks实现多DSP系统多任务程序设计2019-07-10 0

-

请问怎么使用静态类型内部的ISR实现呼叫之间的固定状态?2019-09-11 0

-

如何帮助创建USBUART ISR?2019-11-04 0

-

在FPGA上建立MATLAB和Simulink算法原型的四种最佳方法2020-05-04 0

-

如何透过DSP系统模型建立和设定实现最佳模拟?2021-04-23 0

-

如何在嵌入式系统或快速原型构建板上实现即交即用式部署?2021-11-22 0

-

如何使用CubeMX快速生成FreeRTOS系统并实现多任务处理?2021-12-20 0

-

NoMan-Grid计算原型系统2009-04-17 1046

-

基于ARM的快速原型化平台的实现2009-08-29 425

-

快速小波变换的定点DSP实现2009-05-28 1321

-

DSP实时多任务操作系统设计与实现2016-05-09 697

-

为无人机快速部署可扩展、密集的ISR有效负载2022-10-27 823

全部0条评论

快来发表一下你的评论吧 !