异或门(XOR Gate)的基础知识

描述

异或门,英文名Exclusive OR Gate,简称为XOR Gate,它是一种重要的数字逻辑门,可以实现异或逻辑,即当且仅当其中一个输入为高时,输出为高。如果两个输入均为低或高,则输出为低。

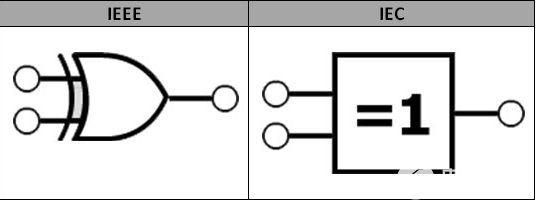

符号

众所周知,定义电子元件有多种标准。通常情况下,一般会遵循 IEEE(电气和电子工程师协会)和 IEC(国际电工委员会)标准。在IEEE和IEC标准中,异或门逻辑符号如下所示:

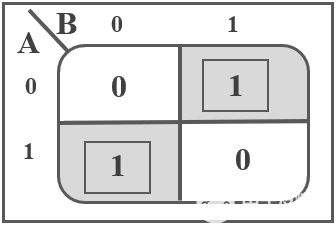

异或门的布尔表达式不能像AND、OR门一样直接确定。由于异或门是一个混合门,因此异或门的输出的布尔表达式由输入的乘法、加法和反相的组合给出。因此,必须使用卡诺图(K-Maps)以及真值表来推导XOR门的布尔表达式。

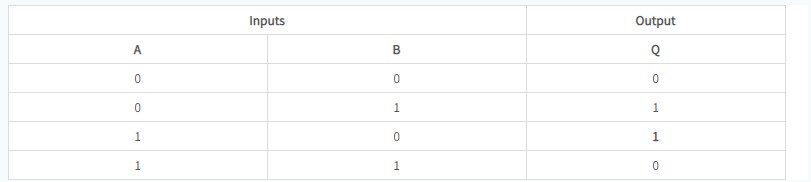

真值表

异或门的真值表如下表格所示。由此可以清楚地看出,当两个输入相同时,异或门会在其输出端产生逻辑低电平(即逻辑“0”)(两者都可能为低电平或两者都可能为高电平)。

低逻辑,在其输出端即逻辑“0”。当两个输入不同时,在其输出端产生逻辑高值,即逻辑“1”。

上述异或门真值表的K-map表示如下图所示:

布尔表达式

使用上面的真值表和对应的K-Map,现在可以推导出XOR Gate的布尔表达式。如果A和B是XOR门的输入,则其输出为:A▔B + AB▔。

XOR输出表示为:A⊕B ,也可以写成:(A + B) ( A▔+ B▔ ) 。

通过应用德摩根定律,上述布尔表达式也可以写成: (A + B) (A▔B▔) 。

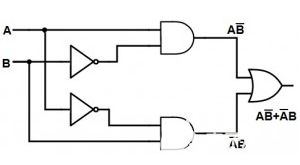

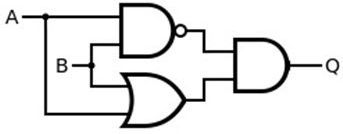

等效电路

异或门定义为具有2个输入以执行异或运算的混合逻辑门。从以上计算公式可知,异或门的主要布尔表达式为:A▔B + AB▔。

因此,具有2个输入的XOR电路是使用AND、OR和NOT门门设计的,如下图所示:

2输入异或门的输出只有当其输入之一为高时才为高电平。如果两个输入相同,则输出为低电平。

使用基本逻辑门的异或门

如果一个特定的门不能直接使用,那么可以使用多个门来设计XOR Gate。异或门可以通过使用NAND门和NOR门等基本逻辑门来设计,因为它们是通用门。

1、或非门

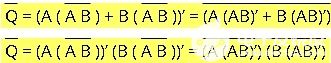

现在来看看如何使用或非门实现XOR Gate。为此,必须重写上面的XOR布尔方程。

Q=A▔B + AB▔

Q = A▔B + AB▔ + AA▔ + BB▔

Q = ( A▔ + B▔ ) (A + B)

Q = ( A▔ + B▔ ) (A + B) = (A' + B') (A + B)

两边取补,得到:

使用德摩根定律,可以得到:

再次对两边取补,最终得到:

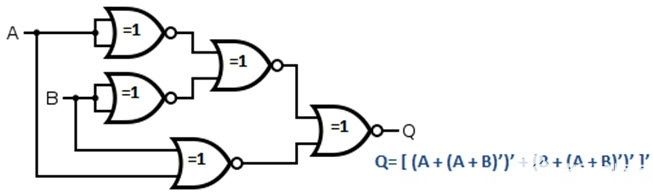

这个等式看起来可以使用或非门来实现。总共需要五个或非门(两个用于反相A和B,一个用于A和B的NOR,一个用于A'和B' 的NOR,最后一个用于获得上述等式)。下图显示了使用或非门实现的XOR Gate。

2、与非门

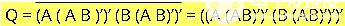

接下来看看如何使用与非门实现XOR Gate。为此,继续重写上面的XOR布尔方程。

Q = A▔B + AB▔

Q = A▔B + AB▔ + AA▔ + BB▔

Q = (A + B) ( A▔ + B▔ )

Q = (A + B) ( A▔ + B▔ ) = (A + B) (A' + B')

将德摩根定律应用于上述等式的第二项,可以得到:

Q = (A + B) ( A▔B▔ )

现在需要使用与非门来实现这个电路,即有:

Q = A ( A▔B▔ ) + B ( A▔B▔ ) = A (AB)' + B (AB)'

两边取补,得到:

最后,再次在两边应用补码,得到:

这个等式现在就可以使用与非门来实现,这里主要使用与非门就可以了。下图显示了使用与非门实现的XOR Gate:

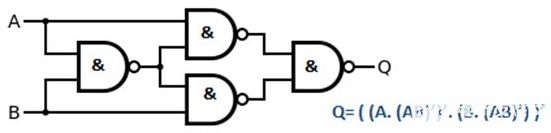

3、使用与门、或门和与非门

现在来看看如何使用NAND、AND和OR门来实现XOR门。为此,仍然需要重写上面的XOR布尔方程。

Q = A▔B + AB▔

Q = A▔B + AB▔ + AA▔+ BB▔

Q = (A + B) ( A▔ + B▔ )

Q = (A + B) ( A▔ + B▔ ) = (A + B) (A' + B')

将德摩根定律应用于上述等式的第二项,可以得到:

Q = (A + B) ( A▔B▔ )

上述等式中的第一项需要一个或门,第二项需要一个与非门,最终等式可以使用与门获得,如下图所示:

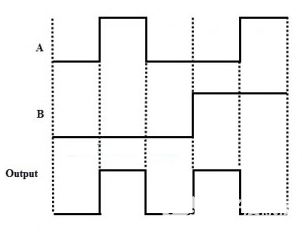

脉冲操作

2输入异或门的脉冲操作如下图所示:

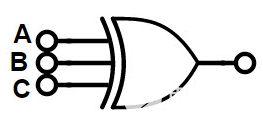

3输入异或门

在某些情况下,需要有超过2个输入的异或门。超过2个输入XOR函数称为“奇数函数”或者“模2和数(Modulo-2 sum)”。3输入XOR门的布尔函数为:Q = A ⊕ B ⊕ C = A▔B▔C + A▔BC▔+ AB▔C▔+ ABC。

下面给出了三输入异或门逻辑符号:

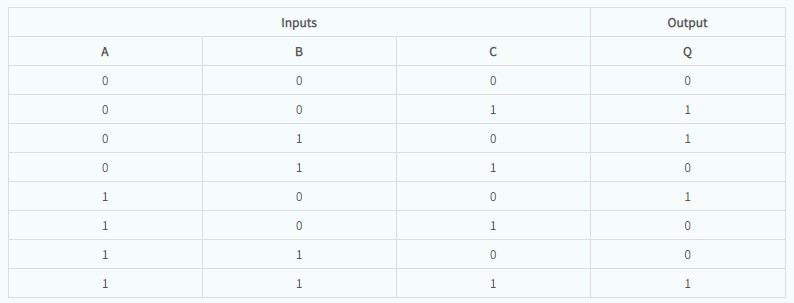

3输入异或门真值表

对于3输入XOR门,当奇数输入处于高电平时,则具有高输入。因此,3输入异或门被称为“奇数功能或门”。

常用的TTL和CMOS逻辑异或门IC

以下是一些常用的XOR IC 的列表,仅供参考:

其中,最流行的基于TTL逻辑的异或门IC是74LS86,它是一款四路2输入异或IC。而对于基于CMOS逻辑的异或门IC,CD4030四路2输入异或门IC是一种主流的选择。

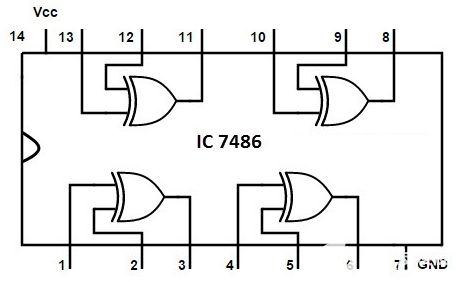

7486四路2输入异或门IC

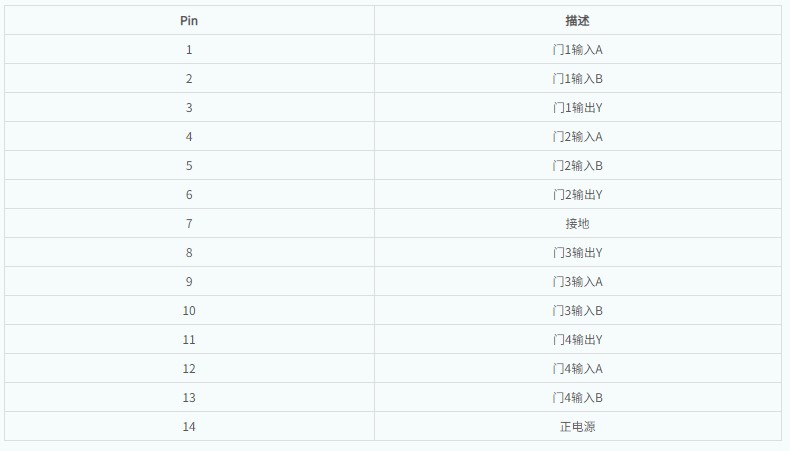

IC 7486是一个四路2输入异或门,即它在一个封装中包含四个2输入异或门,其管脚图和管脚描述如下所示:

主要应用

1、用于加法器

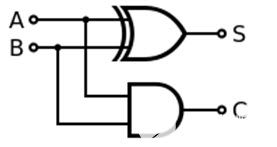

可以设计一位加法器(也称为半加法器),它将添加两位并产生一位输出。使用异或门设计的单位加法器如下图所示:

如果在二进制加法中将“1”和“1”两个位相加,得到答案“10”,在十进制加法中得到 2。半加法器的主要原理是通过“异或”门的输出实现尾随和,并通过“与”门计算进位。

其实,可以级联多个单位加法器电路以形成n位加法电路,从而计算较长二进制数的和。

2、伪随机数生成

线性移位寄存器也称为伪随机数发生器 (PNR)。为了产生随机数,可以通过形成一个线性反馈移位寄存器以特定顺序排列XOR逻辑门。

3、相关和序列检测

当所有输入为高或低时,异或门能够产生低电平输入,即0。当在长数据序列中搜索特定位序列时,可以使用XOR门来找到所需的数据位序列。

在目标序列中找到所需的数据位串的准确性是通过计算获得的0的数量来确定的。在许多通信设备(如解码器和CDMA接收机)中,一般使用相关器,用于提取一组PRN序列中特定伪随机数序列的奇偶校验。

总结

以上就是异或门(XOR Gate)的相关基础内容,主要包括XOR Gate的符号、真值表和布尔表达式。与此同时,还介绍了使用NOR和NAND门实现XOR Gate,以及一些常见主流的XOR IC,希望上述内容能够对大家有所帮助。

-

labview基础知识2018-03-08 0

-

【数字电路】关于逻辑异或门基础知识点总结教程2021-01-23 0

-

通信基础知识教程2010-03-04 773

-

什么是XOR2009-01-19 3985

-

电池基础知识(集全版)2009-11-10 2177

-

异或门,异或门是什么意思2010-03-08 15053

-

电源管理基础知识电源管理基础知识电源管理基础知识2017-09-15 1373

-

异或门的逻辑功能解析2017-11-19 65728

-

三输入异或门逻辑图及表达式解析2017-11-20 85134

-

异或门的电路符号表达_XOR的电路实现2017-11-28 66100

-

异或门基础知识(逻辑表达式_真值表_符号_应用)2020-11-19 96570

-

CMOS异或门仿真设计2023-07-06 2041

-

XOR自门控与时钟门控的不同之处2024-01-02 526

-

异或门的逻辑符号和逻辑电路组成2024-02-04 2419

全部0条评论

快来发表一下你的评论吧 !