西门子EDA通过创新推进硅光子物理验证

EDA/IC设计

描述

集成电路 (IC) 设计流程(特别是较旧的节点)曾经认为所绘即是交付物(设计到掩膜再到硅片)。而且在过去,只需电子设计自动化 (EDA) 行业提供些许帮助,晶圆代工厂就已经能够兑现这一假设。设计公司使用设计规则检查 (DRC) 和版图与电路图对比 (LVS)验证来确保物理版图正确实现预期电路,并符合晶圆代工厂对工艺节点的物理制造要求。然而,即使版图符合所有设计规则,制造过程中仍有可能出现性能和良率问题,这主要归因于各种工艺期间轻微且不可避免的工艺变化。为了缓解这些制造工艺对最终硅片的影响,大多数设计公司都会应用一组额外的可制造性设计 (DFM) 检查,帮助预测给定设计如何针对制造工艺做出应对。例如,工程师使用光刻友好设计(LFD) 仿真来发现版图中任何可能在光刻工艺期间导致分辨率问题的区域。然后,他们可以采用光学邻近效应修正 (OPC) 之类的技术在制造前修改版图,以确保印刷 IC 能够准确表示预期版图。

当然,尝试手动进行上述所有验证是不可能的。确保电子 IC (EIC) 市场取得成功的一项主要开发成果是,出现了一个稳定可靠的自动化验证平台。在EDA 工具中实施的验证策略有助于保证 IC 的可制造性以及整个行业的 IC 设计标准化和优化,这也造就了电子 IC 市场如今蓬勃发展的态势。EDA 工具和技术与晶圆代工厂工艺设计套件 (PDK) 相结合,体现了给定工艺节点的制造规则和要求,是 “无晶圆厂”设计公司起源的核心组成部分。独立晶圆代工厂的出现则是促使 EDA 行业崛起的根本因素;EDA 反过来促成了 CMOS 市场的快速发展,并成为该市场取得成功的关键因素。在此过程中,设计工具也在不断发展,通过不同的抽象级别加速这一过程,同时协助确保正确的设计和版图实现。布局布线 (P&R)等设计工具和方法以及各种设计组件(例如用于定制设计的 pcell),现在被广泛用于推动设计流程不断提升实现效率和成功率。

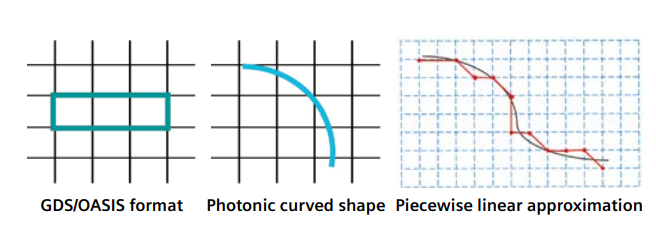

硅光子作为一种新兴技术,有望克服通信和数据传输领域目前在速度、功耗和精度方面存在的一些限制。要兑现这一承诺并使光子 IC (PIC) 成为现有 EIC 技术的有力竞争者,唯有尝试通过复用 CMOS 平台,尤其是验证 EDA 工具集,尝试复制 EIC 领域的成功经验。然而,光子器件的性质造成了一些限制,导致无法直接使用过去用于 EIC 的相同 EDA 工具集。这些限制正在促使 EDA 公司开发创新的变通方案,使设计公司能够以新的方式使用其现有工具的功能来成功验证PIC,而不是花费时间、精力和金钱来创建一套全新的独立工具集。

虽然对 EIC 行业而言,PDK 及使用 PDK 的自动化设计和验证流程已经非常完善,但在 PIC 行业,它们仍处于开发阶段。晶圆代工厂、EDA 供应商和设计公司都在共同努力,为硅光子设计创建成功的自动化设计和验证环境。

▲电子 IC 版图与光子 IC 版图对比验证

-

西门子—SINAMICS G1502009-09-04 1383

-

看EDA领域市场格局,西门子收购Mentor剑指何方2016-11-24 1463

-

西门子收购Mentor会对EDA工具用户带来哪些改变?2016-12-08 1228

-

西门子收购Solido强势进军EDA领域2018-01-03 1604

-

博世和西门子哪个好_博世和西门子的关系2018-04-04 151931

-

西门子中国数字化创新峰会正式开幕2020-09-15 1704

-

系统级芯片设计趋势之下,西门子EDA的前瞻部署2022-07-29 3688

-

西门子Calibre平台扩展EDA早期设计验证解决方案2022-08-01 2160

-

西门子EDA Calibre 平台获台积电先进N3E和N2工艺认证2023-05-11 1927

-

加速创“芯” 西门子EDA技术峰会在沪举办2023-08-27 252

-

助推半导体创新需求,西门子EDA峰会揭秘AI工具链和创新平台2023-09-04 1661

-

西门子完成对EDA软件公司Insight EDA的收购2023-11-17 410

-

EDA助力良率提升:紫光展锐与西门子的成功合作2024-01-26 215

-

nepes采用西门子EDA先进设计流程,扩展3D封装能力2024-03-11 1753

全部0条评论

快来发表一下你的评论吧 !