可用的SRIO RapidIO (SRIO)验证平台

电子说

描述

一、SRIO协议与PCIe的区别

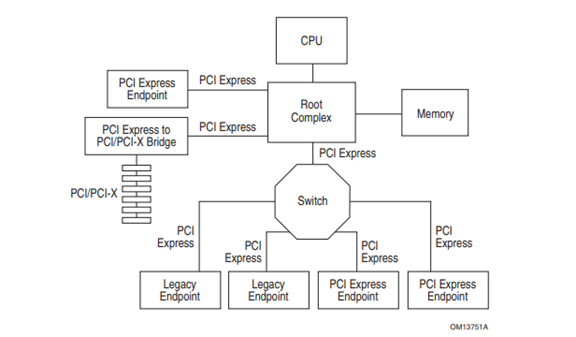

典型的PCIe结构定义了一个以单个中央处理器为核心的计算机系统,如常见的工控机、PXIe机箱控制器、服务器内的IO设备。从系统架构来看,这个结构的优势在于可有统一的软件驱动,软件模型,设备间具备优异的兼容性。兼容性才是王道,厂商就可以用一个标准包打天下。

图1 PCIe 互联架构

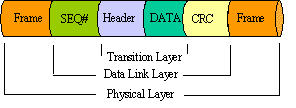

PCIe 的帧格式如下图所示。

帧由 1 字节的帧起始、2 字节的序列号、16 或 20 字节的报头、0 到 4096 字节的数据字段、0 到 4 字节的 ECRC 字段、4 字节的 LCRC、和 1 字节的帧结束。

数据字段中传输的位数越少,开销就越大。零字节数据字段会导致 100% 的开销,因为没有传输数据。

图 2 PCIe 的帧格式

二、RapidIO

RapidIO定义了一种高性能、分组交换互连技术,用于在微处理器、DSP、通信和网络处理器、系统内存和外围设备之间传递数据和控制信息。

RapidIO 适用于点对点的设备间通讯,不需要经过一个中央处理器进行调度,就可以完成设备间的通讯,并且包长度简单,效率相对于PCIe要更高,有效数据传输速度更快。

但是RapidIO没有定义标准的软件模型,这就导致厂家之间的设备大概率无法兼容,从而只能在某些领域进行部署,不易推广。 RapidIO 由于比PCIe更简单、更高效、延迟更低等特点,已经在嵌入式领域、图像处理、通讯系统、军工航天有了大量的应用。

在实际的应用场景中,例如医学影像等图像处理领域,经常需要扩展单块DSP、FPGA的计算能力,这时候需要将多个DSP或者FPGA通过高速串口进行互联,此时RapidIO就是当前互换性最好的一个最佳选择,因为PCIe太过复杂,Xilinx的Auraro效率也不满足要求,并且互换性不好。

三、可用的SRIO验证硬件

目前具备SRIO接口的硬件不多,

推荐广州星嵌电子科技有限公司开发的DSP+FPGA+RAM开发板

也可用于评估EMIF等接口。

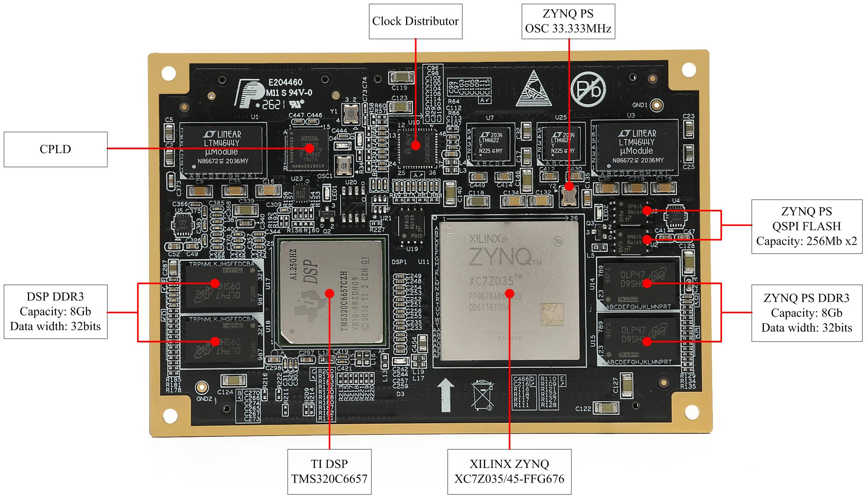

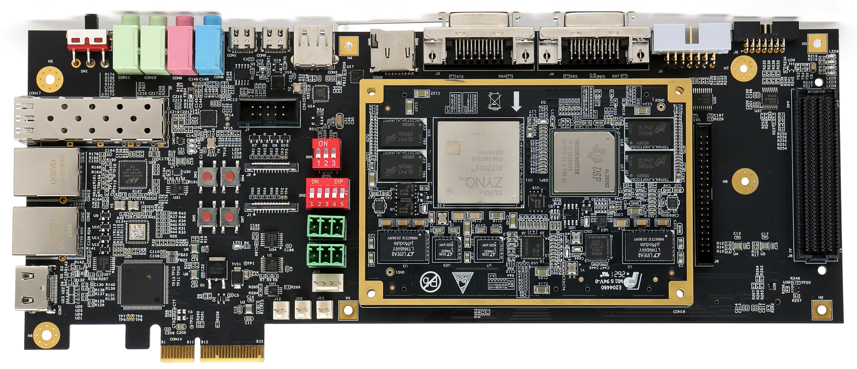

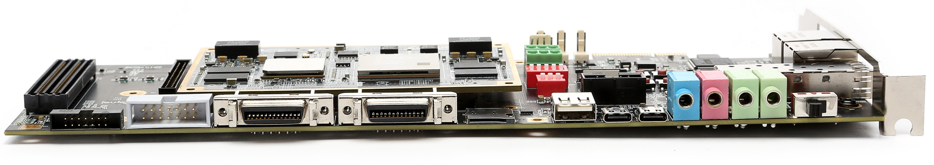

XQ6657Z35/45-EVM评估板,由广州星嵌电子科技有限公司采用核心板+底板架构设计。

DSP选用TI TMS320C6657 双核C66x 定点/浮点,主频 1.25GHz/核;

FPGA选用Xilinx Zynq SoC处理器采用的XC7Z035-2FFG676I 或 XC7Z045-2FFG676I。

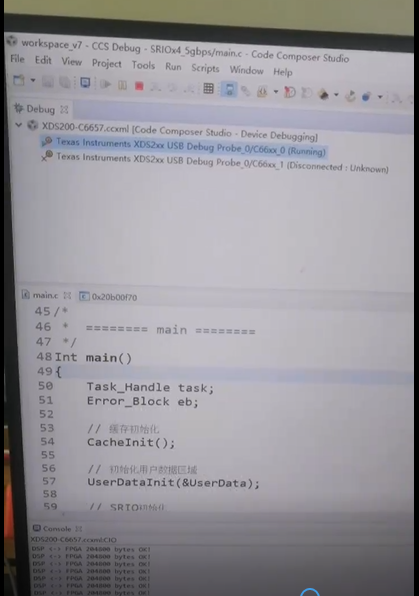

SRIO测试截图

多核DSP C6657+ZYNQ7035工业核心板

多核DSP C6657+ZYNQ7035评估板正面俯视图

多核DSP C6657+ZYNQ7035评估板侧面图1

多核DSP C6657+ZYNQ7035评估板侧面图2

审核编辑 黄昊宇

-

如何学习SRIO2018-06-21 0

-

请问用c6678 srio收发地址位数,DSP端keystone_srio的程序要做什么改进?2018-12-28 0

-

如何利用串行RapidIO去实现FPGA协处理?2021-04-29 0

-

sRIO 2.0中虚拟通道的优势和加速其采用的技术2010-01-12 1578

-

RapidIO应用系统及其验证模型的设计与测试2011-12-23 476

-

基于SRIO协议的板级芯片互联技术2012-01-10 3599

-

TMS320C6474 DSP srio用户指南2018-04-16 827

-

如何了解SRIO IP核三层协议的作用?2020-06-17 2586

-

RapidIO核的仿真以及包时序的分析2022-12-19 1321

-

基于FPGA的SRIO协议设计2023-09-04 742

-

FPGA优质开源模块-SRIO IP核的使用2023-12-12 1010

-

srio交换芯片是什么?srio交换芯片的原理和作用2024-03-16 1870

-

srio交换芯片的原理和用途2024-03-21 296

-

srio交换芯片属于什么种类2024-03-21 254

-

srio交换芯片有啥用2024-03-26 202

全部0条评论

快来发表一下你的评论吧 !