提高系统抗干扰的措施

电子说

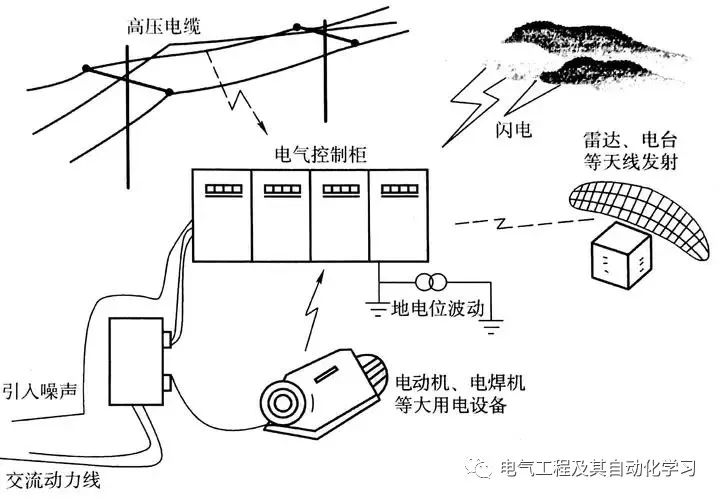

描述

从整体和逻辑线路设计上提高机电一体化产品的抗干扰能力是整体设计的指导思想,对提高系统的可靠性和抗干扰性能关系极大。对于一个新设计的系统,如果把抗干扰性能作为一个重要的问题来考虑,则系统投入运行后,抗干扰能力就强。反之,如等到设备到现场发现问题才来修修补补,往往就会事倍功半。因此,在总体设计阶段,有几个方面必须引起特别重视。

一、逻辑设计力求简单可靠

对于一个具体的机电一体化产品,在满足生产工艺控制要求的前提下,逻辑设计应尽量简单,以便节省元件,方便操作。因为在元器件质量已定的前提下,整体中所用到的元器件数量愈少,系统在工作过程中出现故障的概率就愈小,亦即系统的稳定性愈高。但值得注意的是,对于一个具体的线路,必须扩大线路的稳定储备量,留有一定的负载容度。因为线路的工作状态是随电源电压、温度、负载等因素的大小而变的。当这些因素由额定情况向恶化线路性能方向变化,最后导致线路不能正常工作时,这个范围称为稳定储备量。此外,工作在边缘状态的线路或元件,最容易接受外界干扰而导致故障。因此,为了提高线路的带负载能力,应考虑留有负载容度。比如一个TTL集成门电路的负载能力是可以带8个左右同类型的逻辑门,但在设计时,一般最多只考虑带5—6个门,以便留有一定裕度。

二、硬件自检测和软件自恢复的设计

由于干扰引起的误动作多是偶发性的,因此应采取某种措施,使这种偶发的误动作不致直接影响系统的运行。因此,在总体设计上必须设法使干扰造成的这种故障能够尽快地恢复正常。通常的方式是,在硬件上设置某些自动监测电路。这主要是为了对一些薄弱环节加强监控,以便缩小故障范围,增强整体的可靠性。在硬件上常用的监控和误动作检出方法通常有数据传输的奇偶检验(如输入电路有关代码的输入奇偶校验),存储器的奇偶校验以及运算电路、译码电路和时序电路的有关校验等。

从软件的运行来看,瞬时电磁干扰会影响:堆栈指针SP、数据区或程序计数器的内容,使CPU偏离预定的程序指针,进入未使用的RAM区和ROM区,引起一些如死机、死循环和程序“飞掉”等现象,因此,要合理设置软件“陷阱”和“看门狗”并在检测环节进行数字滤波(如粗大误差处理)等。

审核编辑 黄昊宇

- 相关推荐

- 抗干扰

-

计算机抗干扰能力的措施2011-12-15 0

-

提高敏感器件的抗干扰性能 的常用措施2015-05-07 0

-

位移传感器的抗干扰措施2019-12-12 0

-

形成干扰的基本要素,提高敏感器件抗干扰性能的常用措施有哪些?2021-03-17 0

-

提高系统的抗干扰能力2021-11-11 0

-

微机测量系统中的抗干扰措施2009-03-15 467

-

机电一体化系统的抗干扰措施2010-06-08 755

-

PLC系统的抗干扰措施2009-06-16 1421

-

单片机系统应用中的抗干扰措施2009-10-16 894

-

电路设计中的抗干扰措施2010-12-16 4035

-

常见的PLC控制系统抗干扰措施2014-10-09 28905

-

提高敏感器件抗干扰性能的六点常用措施详细概述2018-06-18 3306

-

在电路设计中抗干扰的措施有哪些2019-08-08 12631

-

如何提高PLC系统的抗干扰能力?2021-05-06 4192

-

单片机抗干扰措施有哪些?2024-03-15 331

全部0条评论

快来发表一下你的评论吧 !