PCB信号走线超出我们想象的热

PCB设计

描述

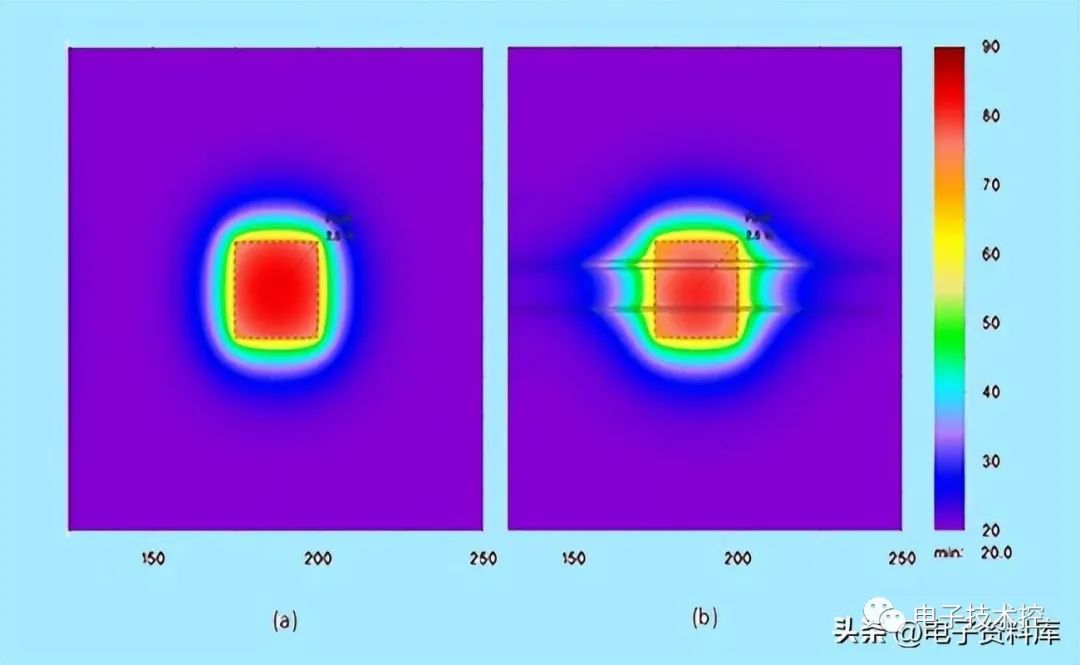

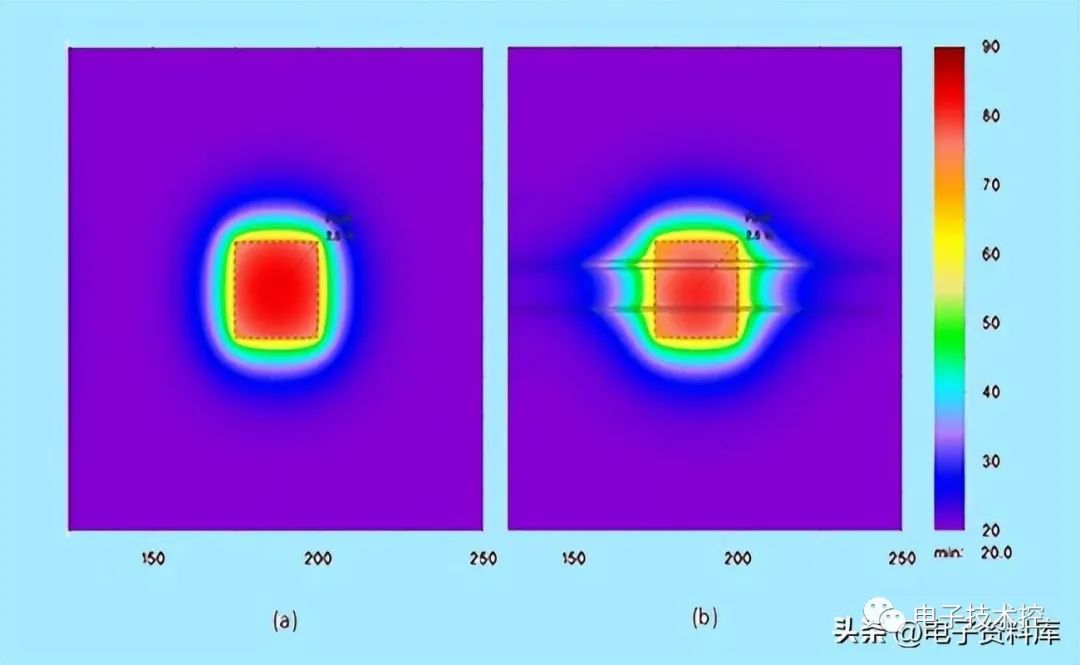

图 1(a) 摘自我们最近的书 [1],显示了从走线穿过电路板到另一侧的垂直热流模拟。模拟是针对 100 mil 宽、1.0 oz 的。在 63 mil 厚的 FR4 板的顶层上,厚迹线加热到几乎 58 oC。这个数字看起来令人印象深刻,但它在一种非常重要的意义上具有误导性。水平和垂直尺度是非常不同的。该图像表示只有 63 密耳(1.6 毫米)厚但 2.0 英寸(50 毫米)宽的横截面区域。

图 1. 通过 PCB 的垂直热流。 图 1(b) 是大致按比例显示的相同热图像。从这种角度来看,很明显,由于电路板的几何形状和热度都很薄,因此水平热量从走线流出的机会非常小。这意味着电路板的底层将具有(大约)与顶层相同的热分布。这意味着中间的所有层也将具有相同的热分布——通过迹线的电流不仅会加热迹线,还会加热其下方的所有东西。

加热垫

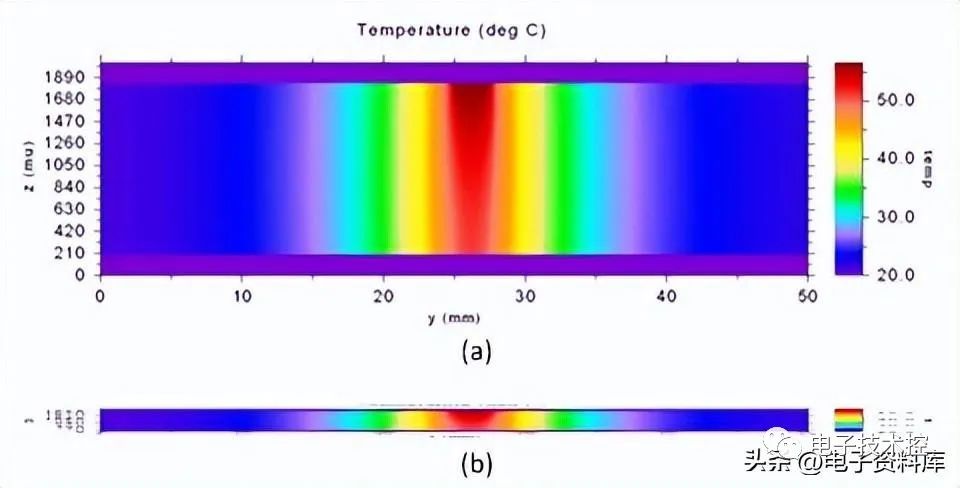

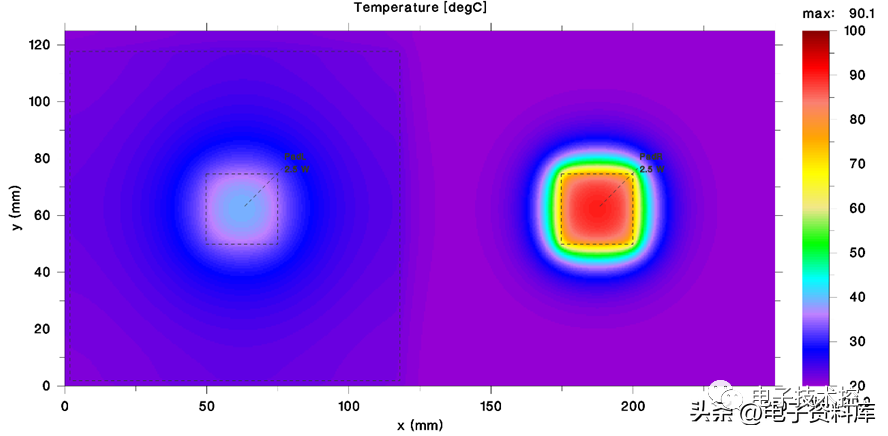

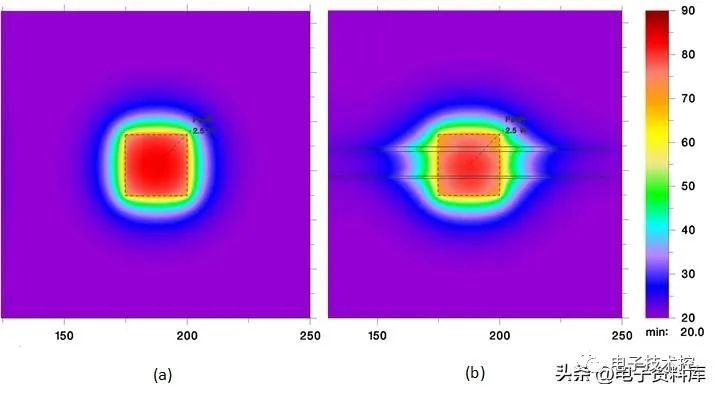

最近,我们进行了一组有趣的模拟(参见 [2] 和 [3]),进一步探索了这种关系。图 2 代表了该模拟的一部分。我们从 250 x 125 毫米 FR4 板开始,1.6 毫米厚。顶层有两个 25 x 25 mm 的铜焊盘。铜垫通过施加 2.5 瓦的功率对其进行加热。125 x 125 mm 的铜平面仅放置在电路板左侧的底层。

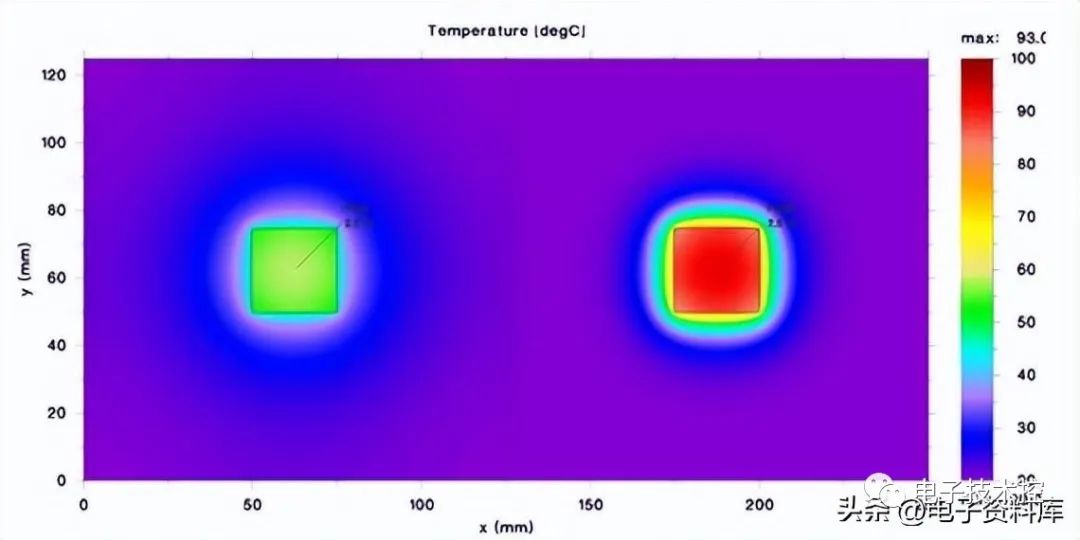

图 2. 用 2.5 瓦加热的两个焊盘。左垫下面有一个大平面。 施加的电源将右侧的焊盘(无底层)加热到 93 oC,高于环境温度 73 oC。在焊盘下方放置一个平面(图像左侧),将焊盘温度降低到 59 oC。但真正有趣的是底层发生了什么,如图 3 所示。

图 3. 图 2 所示电路板的底层。 底层的热分布(图 3)看起来与顶层的热分布(图 2)非常相似。温度也几乎相同。右侧加热垫的顶层温度为 93 oC。底层相同区域的温度约为 89 oC,仅比顶层低 4 度。左侧焊盘下方区域的温度约为 50 oC,比顶部焊盘低 9 度。 那么,如果我们把飞机放在电路板的内层呢?图 4 显示了当平面放置在左侧焊盘下方 0.5 mm 的内层上时底层的热分布。加热垫下方的右侧区域仍然仅比顶层垫低 4 度。较近的平面将顶层左侧焊盘的温度降低到约 45 oC。底层的相应温度约为39 oC,比顶层温度低6度。

图 4. 如果内部平面放置在顶层下方 0.5 mm 处,则底层的热分布。 有趣的是,铜平面的存在往往会降低整体温度,因为水平热流更好,但它对整体热模式的影响要小得多。即使在底层有一个铜平面(图 2),平面上的热分布也与其上方的热分布相似。铜表面和平面上可能存在(并且确实存在)显着的热梯度,这一点在我们的书中 [1] 的许多地方都得到了强调。 这些结果说明了一个重要事实:电路板底层的热分布类似于顶层的热分布。顶层和底层之间的点温差通常小于 10 oC,通常在 5 oC 甚至更低的范围内。

加热痕迹

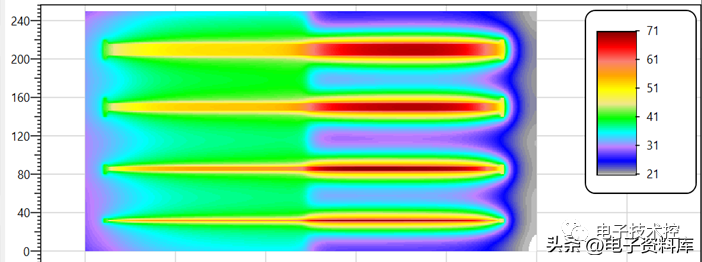

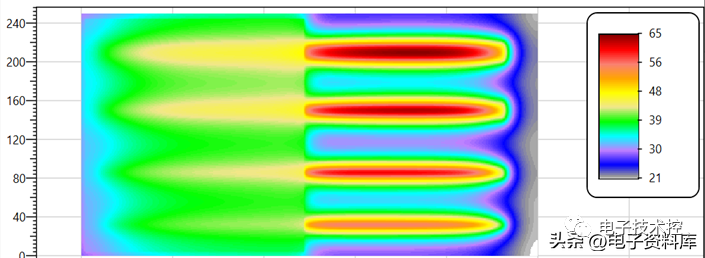

现在这些焊盘都比较大。如果我们查看正常大小(加热)的迹线会怎样?我们用 1、2、4 和 6 毫米宽(分别约为 40、80、160 和 240 密耳)的 4 条迹线替换了模拟中的焊盘。每条迹线承载足够的电流以将其温度(没有底层平面)提高到大约 70 oC。模拟平面放置在板的左半部分的底层。图 5 显示了仿真顶层和底层的热分布。

图 5. 模拟加热迹线的顶层和底层的热分布。在此模拟中,板左侧的底层有一个平面。顶层

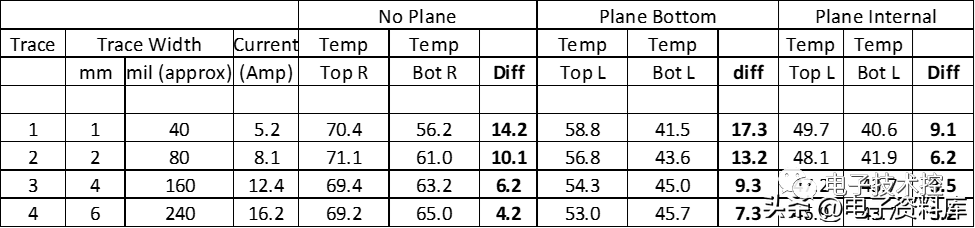

图 5. 模拟加热迹线的顶层和底层的热分布。在此模拟中,板左侧的底层有一个平面。底层 我们还在电路板左侧下方的迹线下方 0.5 毫米处模拟了该电路板(未显示)。结果列于表 1。重要结果在每个平面配置(无、底层、内层)的差异“差异”列中。

表 1. 跟踪级模拟的结果(以 oC 为单位的温度)。

对于最宽的走线,温差往往最小,并且随着焊盘/走线宽度的变窄而增加。尽管如此,即使是最窄的迹线下的局部温度仍然很重要。此处未讨论(再次参见 [3]),温差是电路板厚度的函数。随着电路板厚度的增加,温差也会增加。 结果倾向于证实上述一般性陈述:电路板底层的热分布类似于顶层的热分布。顶层和底层之间的点温差通常小于 10 oC,通常在 5 oC 甚至更低的范围内。 相关资源Anritsu 向 VNA 系列添加工具以提高信号完整性测试能力每通道 224 Gb/s:选项和挑战

影响

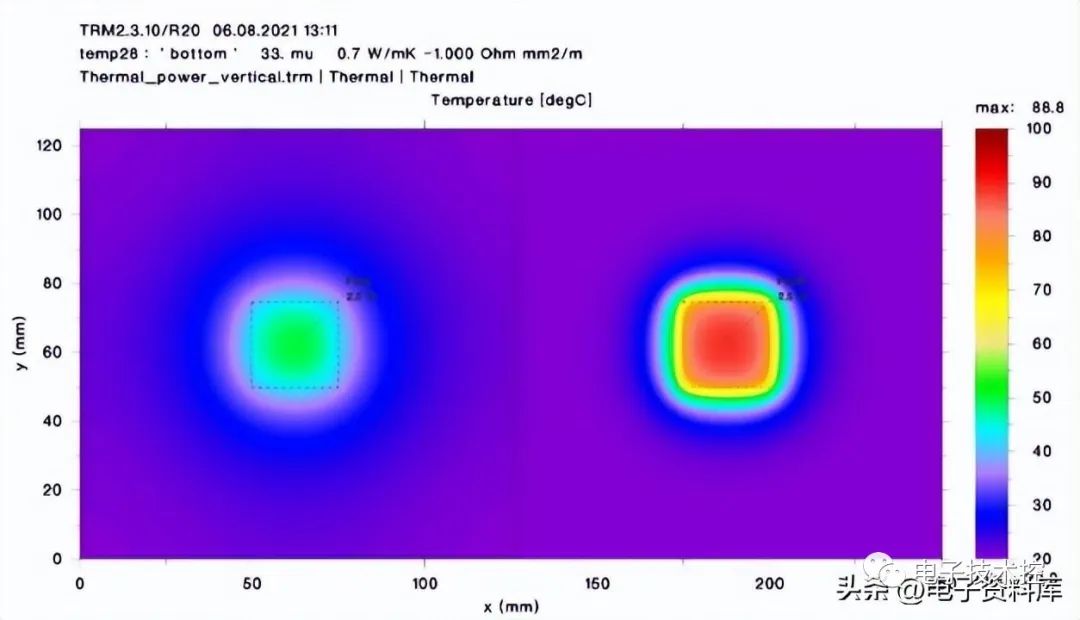

以上有几个可能的含义。首先,这些结果解释了为什么热通孔效率如此之低,它们几乎是无效的。根据定义,热通孔必须去某个地方。通常,它们终止于电路板另一侧的铜表面(平面)。等式 1 显示了它们背后的理论。热传导公式为: 等式 1. Q/t = kA(ΔT)/d 在哪里: Q/t = 传热率(瓦特或焦耳/秒) k = 导热系数(W/m·K) ΔT = 温度变化 (oC = oK) A = 重叠区域 d = 焊盘和平面之间的距离 在上面的示例中(图 2 和图 3),加热垫(没有底层平面)比环境温度高 73 oC(ΔT=73)。但在这种情况下,没有地方可以终止热通孔。当我们在底层添加一个平面时,我们可以终止热通孔,ΔT(焊盘和平面之间)降低到 9 oC。(内部平面外壳将 ΔT 降低到 6 oC。)几乎所有的好处都来自于铜平面本身的添加。额外的热通孔的边际贡献几乎可以忽略不计。 第二个含义是,内层上较小的信号走线将具有与其上方和下方的顶层和底层几乎相同的热分布。图 6(b) 说明了一个内部走线层,位于顶层下方约 6 密耳处,穿过我们的一个加热垫下方(下方没有平面)。有两条迹线,分别为 1.0 mm 和 2.0 mm(40 和 80 mil)宽,通过焊盘下方。图 6(a) 是相同的焊盘,没有任何痕迹。

图 6. 比较无内部走线 (a) 和焊盘下方 6 mil 的内部走线 (b) 的加热焊盘下方的热模式。 热模式说明走线对冷却的影响很小(走线越小影响越小),但总的来说,信号走线与加热垫的热分布几乎相同。由于电阻率是温度的函数,这意味着信号走线的电阻在通过焊盘下方时沿走线从点到点发生变化 [4]。可以推测,这意味着差分对每一侧的电阻,或信号总线中不同差分对的电阻,如果它们通过不同的热环境,它们可能会有所不同。这可能会或可能不会对信号电平和时序产生影响,具体取决于具体情况。

实验证据

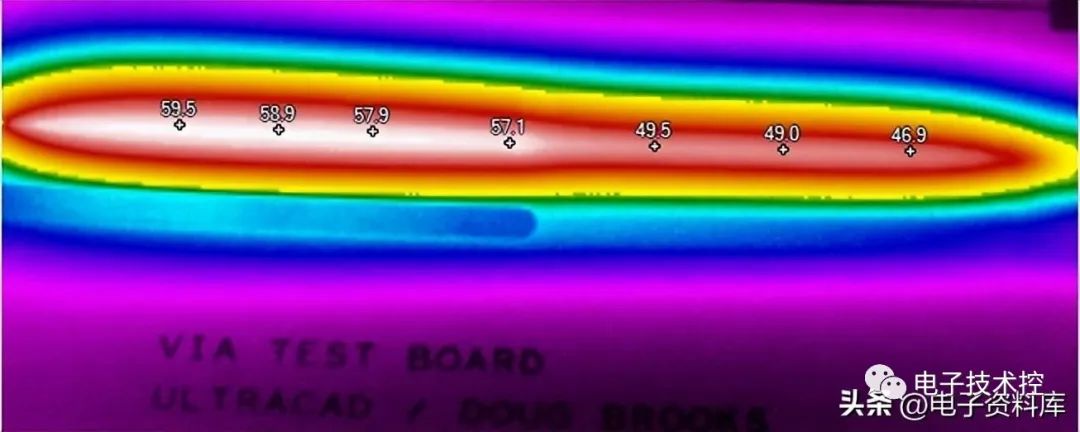

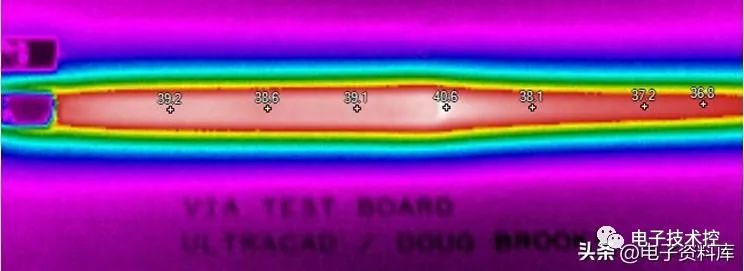

一个适当的问题是:我们是否有任何实验证据来支持我们在此讨论的热剖面类型?答案是肯定的。例如,在最近的一篇文章 [5] 中,我们(实验)表明,如果焊盘温度发生变化,则在焊盘下方布线的走线会改变电阻。然后我们询问这是否有任何信号完整性影响。 在我们的书 [1] 中,我们将第 8 章专门用于通过加热。在那一章中,我们有两个表格来确认我们的仿真模型与我们的实验测试板相匹配 [6]。图 7 和图 8 改编自该章中的图 8.8 和 8.9。这些热像图来自实验性的 6 英寸长的走线,中间有一个通孔,从顶层到底层。每条迹线的左侧部分位于顶层。左侧的温度指示用于该顶层上的迹线/通孔。每个图像的右侧部分是顶层的温度,由底层的实际轨迹加热。 在图 7 中,右侧顶层比对面层的同等位置低约 10 度。但在图 8 中,差异仅比对面层低约一到两度。这与我们上面的模拟一致。随着加热宽度的增加,温差减小。

图 7. 承载 6.65 安培的 27 mil 宽走线(改编自 [1],图 8.8。)

图 8. 承载 8.55 安培的 200 密耳宽走线(改编自参考文献 1,图 8.9)

底线

加热走线和焊盘的热影响不仅限于它们所在的电路板层。它们或多或少地反映在它们上方和下方的每一层上。

审核编辑:汤梓红

-

PCB走线2012-11-13 0

-

pcb走线2014-03-14 0

-

PCB Layout中的专业走线策略2014-08-13 0

-

信号在PCB走线中传输时延(下)2014-10-21 0

-

信号在PCB走线中传输时延 (上)2014-10-21 0

-

PCB直角走线的影响与计算方式。详解2014-10-28 0

-

详解PCB直角走线的影响与计算方式。2014-11-07 0

-

PCB中直角走线的对信号的影响有哪些?2014-11-18 0

-

PCB Layout走线秘籍2017-07-07 0

-

三种特殊的PCB走线技巧2019-03-18 0

-

pcb蛇形走线2019-05-22 0

-

PCB布线这几种走线方式,你会吗?2019-08-20 0

-

PCB布局之蛇形走线2022-12-27 0

-

PCB走线跟哪些因素有关?如何计算PCB走线的线宽?2023-04-12 0

-

PCB走线的设计细节详解2023-04-13 0

全部0条评论

快来发表一下你的评论吧 !