使用延迟时钟的时序关键复杂设计中的设置冲突修复

描述

现在,这些芯片的性能和时钟频率越来越高,以满足互联网上的高速数据流量或密集型CPU任务本身。

集成电路是任何电子设备的核心。现在,这些芯片的性能和时钟频率越来越高,以满足互联网上的高速数据流量或密集型CPU任务本身。时序/速度是这些设备最重要的方面,公司正在推动自己在更短的时间内实现这一高性能目标。因此,时序/签核是解决ASIC芯片设计高吞吐量要求以决定整体上市时间的一个非常关键的阶段。

有多种 EDA 工具可用于通过数据路径优化进行时序分析和时序修复。但是,本文的主要重点是提供使用延迟时钟技术的剩余设置时序修复的见解/算法,而不会影响其他时序分析矩阵。

修复安装程序冲突的基本方法

当数据路径与捕获翻牌时捕获的时钟相比缓慢时,会发生安装冲突。考虑到这一点,有各种方法可以修复设置。

数据路径优化

有很多方法可以修复优化的数据路径,如 Upsize、vtswap 和在数据路径中插入缓冲区中继器等。这可以使用签核工具的生态生成功能来实现。运行一轮计时修复后,签核计时工具已应用所有可能的数据路径优化技术。它无法通过进一步优化数据路径来修复剩余的违规,要么可能导致其他路径的质量下降,要么没有进一步的优化数据路径的范围。

使用有用的倾斜

为了修复剩余的设置冲突,我们别无选择,只能在签核工具中修复路径。

触摸时钟路径是这里的解决方案之一。

如果数据路径已基本优化,则修复设置冲突的最后一个选项仍然是使用“有用的倾斜”概念。有用的偏斜涉及两种方法:早时钟和晚时钟。减少启动时钟延迟或增加捕获时钟延迟。但是,要更改时钟,必须确保上游(对于早时钟)和下游(对于晚时钟)的路径不违规。

早期发射时钟

较早的时钟需要在PnR实现工具中检查物理网络/小区位置,然后确定早期时钟的适当候选者。同样为了在签核工具中实现早期时钟生态,提取的r / c对于新网络将有更大的差异。因此,早期时钟在实现和签核工具之间的RC中产生最大的影响。为了实现早期时钟,除了物理更改外,还使用了断开连接/连接等逻辑更改,因此请始终运行形式。

延迟捕获时钟

对于较晚的时钟,新添加的时钟单元将被放置在附近以捕获翻牌,并且新创建的网络的净长度将非常小。因此,R/C提取数据仍然有效,因为RC值变化的影响很小。最好使用“延迟时钟”方法创建生态。

为什么我们专注于晚时钟而不是早时钟

如前所述,延迟时钟对eco实现工具和签核定时工具之间的RC相关性的影响最小。如果有多个路径汇聚在同一终结点上,则很容易根据终结点分离路径并在终结点上应用安装程序修复,可以修复大多数设置路径。

多场景分析功能可以轻松检查同一会话中的设置/保持违规。

?实现

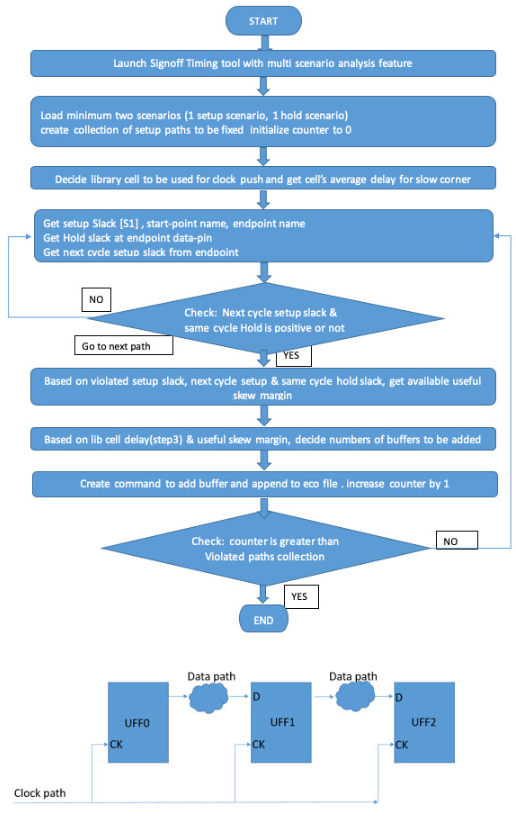

我们遵循以下算法,使用延迟时钟创建设置生态。

将上述流程图步骤合并到脚本中需要一次性工作。生成脚本后,它会减少分析所有路径和生成时序生态的总时间。

我们能够部署上述算法中的所有步骤,并在采用深亚微米技术的设计上运行它。脚本可以分析所有设置路径并创建两个输出文件。1. 总结.csv 和 2.late_clock_eco.tcl

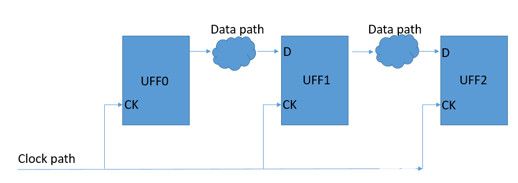

考虑从 UFF0/CK 到 FFF1/D 违反设置的映像 2 场景。 [示例输出如下所示]。

summary.csv

startpoint,endpoint,slack,setup_from_ep,hold_on_ep,late_clock_count

UFF0/CK,UFF1/D,-0.040,-0.051,0.080,0

late_clock_eco.tcl

add_buffer_on_flop_clock_pin UFF1

add_buffer_on_flop_clock_pin UFF1

add_buffer_on_flop_clock_pin UFF1

对于具有设置/保持的设计,跨多个场景违规。感兴趣的设置/保持场景可以加载到签核工具中,脚本可以在不干扰未违反的设置/保持路径的情况下生成 eco。

如果违反下一个周期设置,脚本将不会在 UFF1/CK 上添加任何缓冲区。同样,如果在 UFF1/D 上违反了保留,脚本将不会在 UFF1/CK 上添加任何缓冲区。

在增加下一个周期路径 [UFF1/CK 到 UFF2/D] 的设置裕量后,增加同一周期的保持裕量 [UFF1/D] 和运行脚本将增加缓冲区。

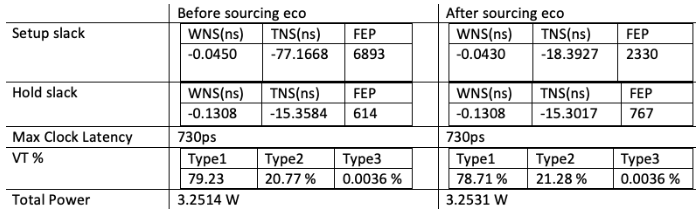

个案研究

上述流/脚本在一个块上使用,以修复设置冲突。在使用此脚本之前,进行了以下假设:

参考块在 PnR 中具有中度拥塞。对于高度拥挤的设计,紧凑的布线资源或高利用率的设计将没有足够的空间来实现生态。

实施/PNR 工具和签核计时工具之间的关联是正确的。

STA工程师了解后端实现工具,如果遇到任何问题来实现eco,能够进行调试。

以下是设计复杂性:

技术:深亚微米

放置的细胞数(大约) : 1100 K

利用率(标准单元格行/总计):40%/50%

添加的迟到时钟单元总数:7250

QOR比较

在上述算法中进一步添加

对于复杂的高速设计,目标插入延迟/最大延迟至关重要。限制是在修复时序冲突时不超过最大延迟。这种特殊情况也可以添加到上面的算法中。

STA 分析变得越来越重要,并且是满足高性能计算、高级图形和网络 SOC的高吞吐量要求的关键领域,以决定当今具有挑战性的低节点技术时代的总体上市时间。创建新的算法和脚本来修复建立/保持时序问题。这将有助于减少时序签核关闭,从而缩短上市时间。即使在数据路径完全优化之后,使用延迟时钟进行有用的偏斜确实有助于更快、更准确地收敛时序,而无需任何手动操作。

审核编辑:郭婷

-

FPGA开发过程中配置全局时钟需要注意哪些问题2024-04-28 0

-

如何有效的管理FPGA设计中的时序问题2009-04-14 0

-

布线后修复时序违规的方法研究2010-05-28 0

-

FPGA设计中的安徽时序问题大时代如何有效地管理2017-09-01 0

-

如何在AISGEN中设置EMIFA的时钟以及时序?2019-09-25 0

-

如何使用TX_ClK_o作为参考时钟来设置输出延迟?2020-05-01 0

-

在FPGA设计中时序就是全部2021-05-18 0

-

时序路径和关键路径的介绍2021-07-26 0

-

FPGA时序约束--基础理论篇2023-11-15 0

-

时钟树优化与有用时钟延迟2011-10-26 4186

-

华为静态时序分析与逻辑设计的详细课程2021-01-14 923

-

使用延迟时钟修复时序关键复杂设计中的设置违规2022-06-02 963

-

时序约束的相关知识(二)2023-03-31 1261

-

RQS_CLOCK-12时钟设置建议2023-07-26 471

-

FPGA工程的时序约束实践案例2024-04-29 122

全部0条评论

快来发表一下你的评论吧 !