引言

目前,用FPGA(现场可编程门阵列)实现FIR(有限冲击响应)滤波器的方法大多利用FPGA中LUT(查找表)的特点采用DA(分布式算法)或CSD码等方法,将乘加运算操作转化为位与、加减和移位操作。这些结构需要占用器件较多的LE(逻辑元件)资源,设计周期长,工作频率低,实时性差。本文提出一种基于Stratix系列FPGA器件的新的实时高速脉动FIR滤波器的快速实现方法。利 用FGPA集成的DSP(数字信号处理器)乘加模块定制卷积运算单元,利用VHDL(甚高速集成电路硬件描述语言)元件例化语句快速生成脉动阵列结构的FIR滤波器,设计周期短、可移植性强,设计采用全流水结构,能高速、无滞后地实现实时信号处理。

1 设计指标及参数量化

1.1 滤波器技术指标

本文依据以下技术指标设计一个64阶等波纹滤波器:Fs=4.092 MHz;Fpass=1.4 MHz,fstop=1.6 MHz;Wpass<1 dB,Wstop<-50 dB。使用MATLAB中FDA-Tool工具获得滤波器系数。

1.2 参数量化

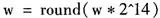

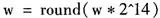

从FDATool中得到的滤波器系数值是一组浮点小数,必须量化为定点数才能在FPGA器件中实现。本文采用移位舍入的量化方法对滤波器系数进行量化,MATLAB描述为:

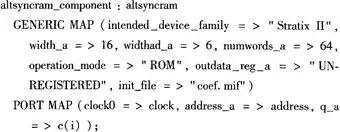

得到64阶系数。滤波器系数预先存入器件内部ROM中,通过修改coet.mif文件中的参数可以改变滤波器的类型或参数。使用altera_mf库中altsyncram元件可以直接调用ROM中保存的数据。其调用语句描述如下:

2 FIR设计

2.1 器件简介

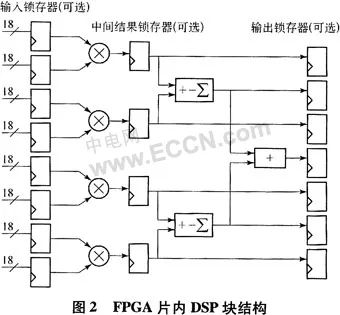

Stratix系列FPGA内部提供了丰富的硬功能模块,如片内RAM、PLL(锁相环)、DSP模块等,充分理解这些模块的结构特点和工作原理,掌握其使用方法,可以充分利用器件资源,最大程度地发挥器件在整个系统设计中的作用,使系统设计最优化。提供的DSP模块集成了乘、加/减/累加、求和这几种算术操作,支持符号数、无符号数和混合运算,并且在这些计算路径中集成了可选的寄存器级和全局/局部时钟控制。一个DSP块最多可以配置成8个9×9、4个18×18或者1个36×36的乘法器,可工作在简单乘法器模式、乘累加模式、2乘加模式和4乘加模式,应用这4种模式,可以实现高性能的DSP算法。本文选用StratixⅡ器件,在QuartusⅡ开发环境下应用4乘加模式生成脉动阵列PE(处理单元),用VHDL描述实现FIR滤波器设计。

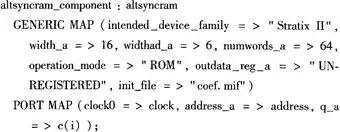

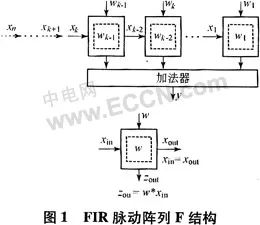

2.2 脉动阵列结构没计

本文参考文献[6]中阵列F结构--扇入结果,输入流动,权值存入PE,设计一种可实时更替权值的FIR脉动结构,如图1所示。权值w从上流入各个PE中,输入x门左向右流入PE。在这个阵列中,x值在每个单步时刻内向右边的PE移动一次。在每次计算中,各个PE同时进行乘法,算出同一个y值的各乘积项,然后将乘积结果扇入至加法器中相加,得到该y值的结果,实现FIR算法。

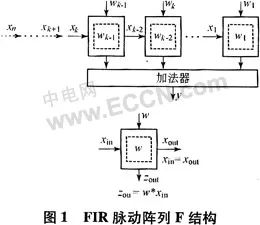

2.3 PE设计

DSP模块集成的算术操作中,4乘加模式就是4个乘法器将乘积送出相加,输出一个加/减的结果。利用模块内部可选的寄存器,可使输入数据在模块内部流动,实现移位寄存器功能,如图2所示FPGA片内DSP块的结构。若两路输入分别为输入信号和滤波器系数,则图2所示的结构恰好构成一个4阶FIR滤波器。

本文选用DSP模块构成脉动阵列结构FIR滤波器的PE卷积单元。具体方法是,采用基于Altera_mf库的乘累加运算元件“ALTMULT_ADD”可以快速完成PE设计。通过Altera的IP工具MegaWizard管理器(MegaWizard Plug-In Manager),定制算术单元(Arith-metic)中乘累加底层基本宏功能模块的参数,设置需要的乘法器个数、输入输出数据格式、流水线控制时钟等参数,即可完成4阶卷积PE元件的设计。

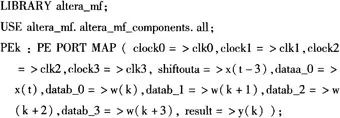

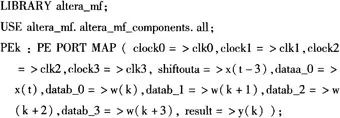

通过调用宏功能模块生成元件的封装文什,然后在设计代码中调用该封装文件。本文选择16位符号数输入、34位符号数输出,设置分级流水线控制输入、输出、乘积结果和加法结果,选择一路输入内部移位。第k个PE元件例化VHDL描述如下:

元件中clk0~clk1分别指向PE中各级寄存器建立时钟。例如t-1时刻,x(t-I)~x(t-4)参与PEk中计算;t时刻,数据x(t)流入PE时,PE 中 4个乘法单元中寄存的数据往前流动,x(t-4)从shiftouta端门流向下级PE。

3 FIR优化设计

将前述的例化的PE单元按图1所示的脉动结构连接起来,就完成了一个基本的脉动FIR滤波器设计,为提高系统性能,需要进一步对设计进行优化。

3.1 时序优化设计

对设计而言,提高工作频率至关重要,更高的工作频率意味着更强的处理能力。合理设计系统的时序对提高整个设计的工作频率有着至关重要的作用。而整个系统中最核心和复杂的时序关系为PE内部乘加时序。以下时序优化以PE单元为例。

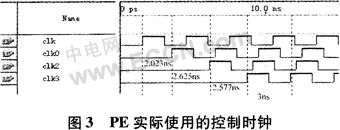

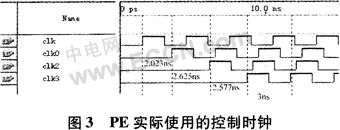

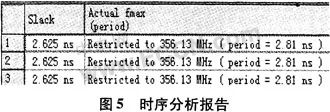

本设计期望系统工作在200 MHz以上。因此,对设计的tco(时钟到输出延时)、tsu(输入建立时间)、tpd(引脚到引脚延时)分别约束为3 ns、2 ns、5 ns。编译后从时序分析报告(Timing Analyzer Report)可得到PE处理单元的基本时序关系。若使用单周期设计,从输入数据到参与乘法、加法计算再到结果输出,至少需要2.023+1.829+2.625+2.577=9.84 ns才能完成一次运算,达不到期望时钟频率。若应用DSP模块的流水线工作,合理设置PE单元各级触发时钟,则可使系统工作频率昆著提高,系统最高可工作在356.13 MHz(相同速度等级的芯片,Altera公司提供的9位16阶FIR IP核,参考工作频率为217.15 MHz)。考虑系统完成后全天候工作,为保证系统长期稳定,本设计最终选用208.33 MHz系统工作频率,设计实际使用的控制时钟如图3所示。

3.2 加法优化设计

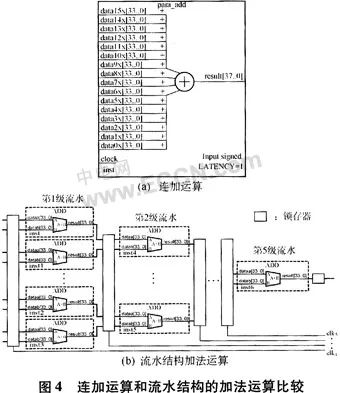

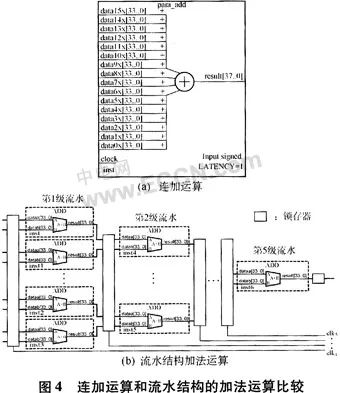

设计一个64阶的滤波器,需要使用16个PE,即需要对16个乘加结果进行加操作,如果采用图1所示的加法运算,如图4(a)所示,计算一次y值需要15个时钟周期才能完成,而且在15个周期内各个加法输入不能变化,若设计中PE能达到300 MHz的工作频牢,加法也只能工作在20 MHz,必然阻碍设计的高速实现,成为制约系统性能的瓶颈。

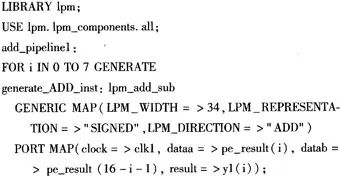

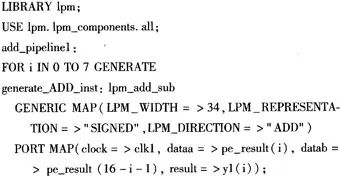

采用流水线的加法运算是解决这个瓶颈的最好方法。如图4(b)所示。clk1~clk5与PE计算时钟同步,无需延长加法计算时钟,第5级流水的加法器使能后就能实时得到y结果。通过LPM(参数化模块库),直接在代码中实例化LPM加法运算,就能快速生成全流水结构的加法模块。其中第1级16个加法描述如下:

END GENERATE;

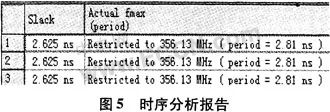

4 FIR实现

上述的描述在QuartusⅡ开发工具中进行编译和布局布线,采用的目标器件为EP2S601024C4芯片,系统内部最高运算时钟为356.13 MHz,如图5所示。

设计的其他性能参数如下:总逻辑单元1 037个;总寄存器单元1 070个;总存储器容量2 048B;使用的9位DSP模块128个;最差输入引脚到寄存器延时1.750 ns;最差寄存器到输出引脚延时2.615 ns。

本设计经过MATLAB与Modelsim联合功能仿真,MATLAB与Quartus联合时序仿真,两种仿真结果与FPGA处理后的数据一致。

5 结束语

本文结合FPGA器件的结构和特点,利用DSP模块及其内部寄存器实现FIR脉动滤波器,不仅性能高,同时节约了LE资源和布线资源。通过MegaWizard宏模块编辑器,可以快速定制核心的处理单元实现脉动结构,对不同结构的滤波器只需修改定制处理单元参数和ROM中系数,就可以迅速设计出新的滤波器。采用全流水加法结构,使用最少的逻辑单元,达到最高的工作频率,完成对信号的实时、高速处理。

至芯科技12年不忘初心、再度起航11月12日北京中心FPGA工程师就业班开课、线上线下多维教学、欢迎咨询!

FPGA开发中时序不满足(建立时间)的典型案例及解决方法

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!