信号完整性仿真:DDR3/4/5系列地址信号端接优化对比

存储技术

598人已加入

描述

导读:

DDR5协议发布已经有一段时间了,其中的变化还是比较大的,地址信号采取了ODT的端接形式,本篇文章为大家仿真一下DDR5地址信号。同时,我也推荐大家关注我在仿真秀原创的精品课《DDR3/4/5系列信号完整性仿真24讲》,让你清楚掌握DDR协议和仿真关键技术要点。以下是正文:

一、DDR5地址信号仿真

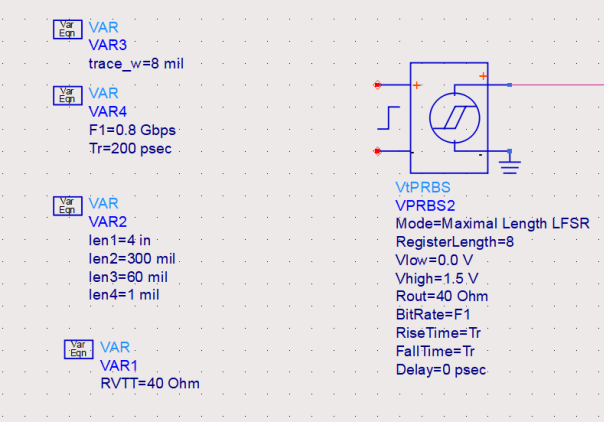

为了直观观察DDR5速率和端接变化的影响,我们对比统一链路在运行DDR3、DDR4、DDR5时的波形质量;我们直接看DDR3-1600速率,flyby结构中1驱8,基本仿真设置如下:

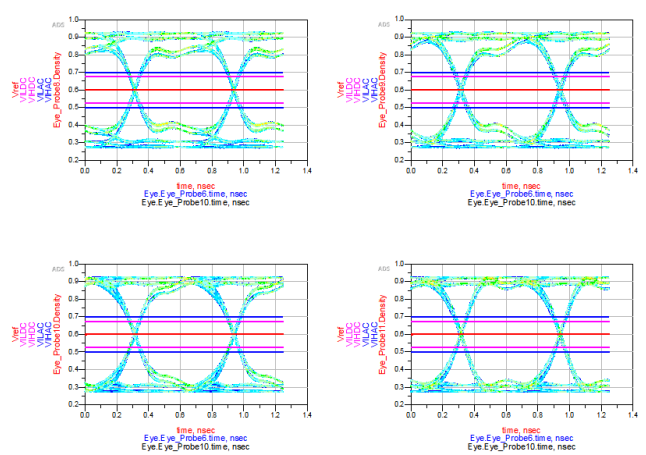

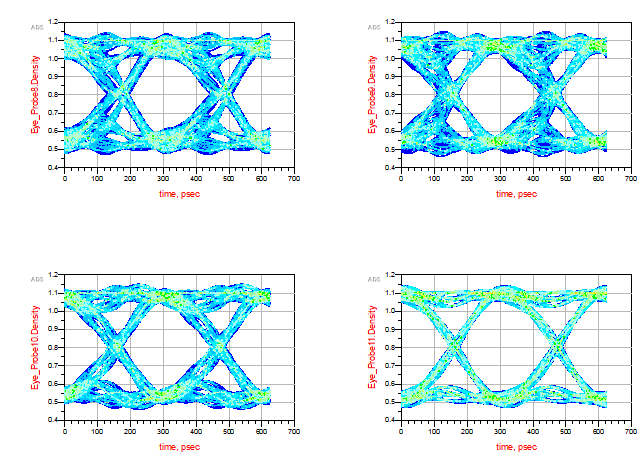

眼图如下:

此时,信号在末端通过RVTT(40ohm)端接到VTT,波形还是不错的,下面来看DDR4-3200的信号:

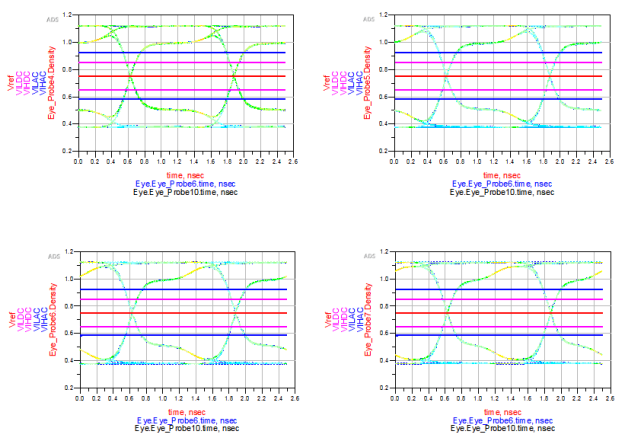

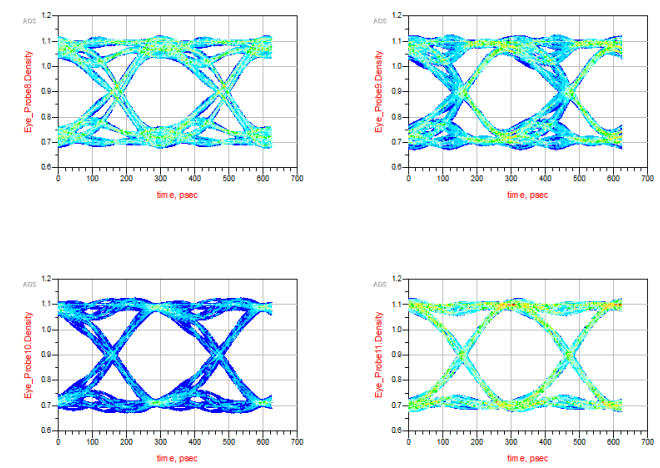

DDR4时,信号在末端通过RVTT(40ohm)端接到VTT(0.6V),波形还可以接受,下面来看DDR5-6400的信号:

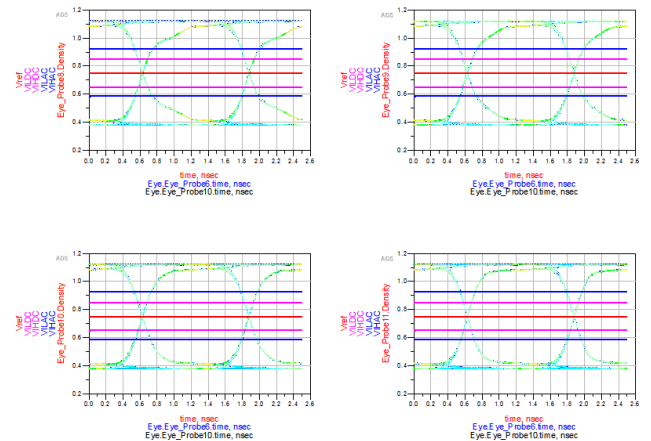

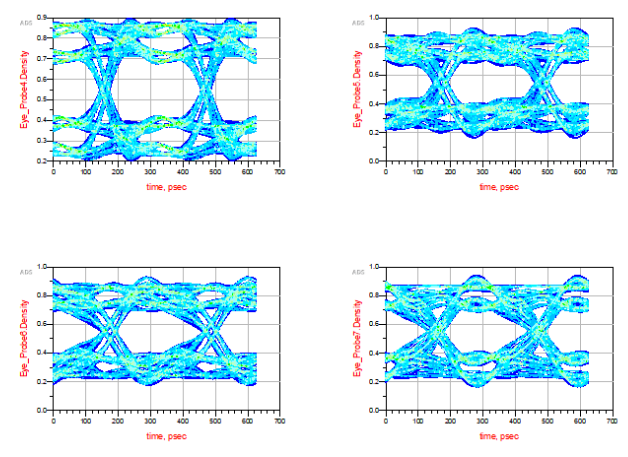

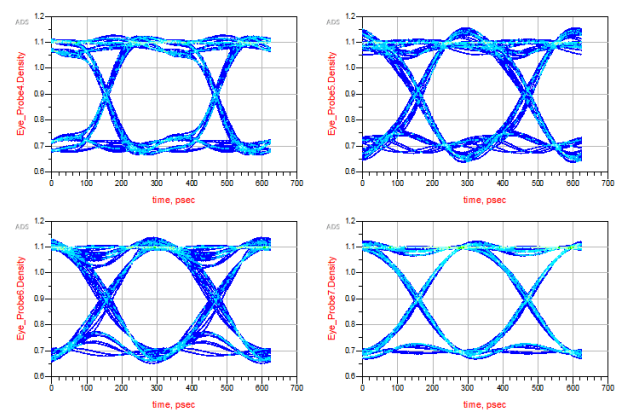

此时,如果还是通过外部端接到VTT的话,波形已经不是很好了,下面对比一下在最后一颗芯片内部端接,波形如下:

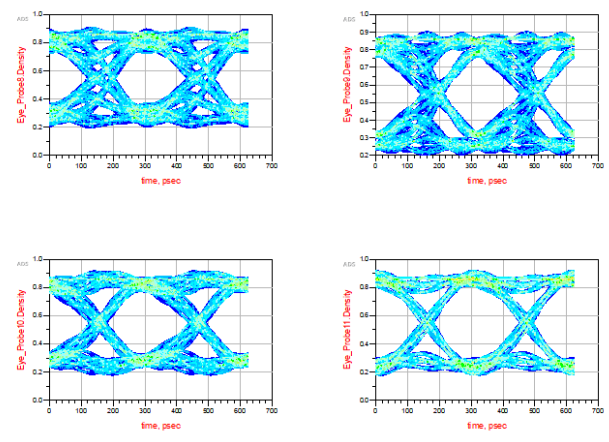

可以看到通过内部端接,波形有所好转,但是仍然不是很好,下面将第一片芯片也做内部端接,波形如下:

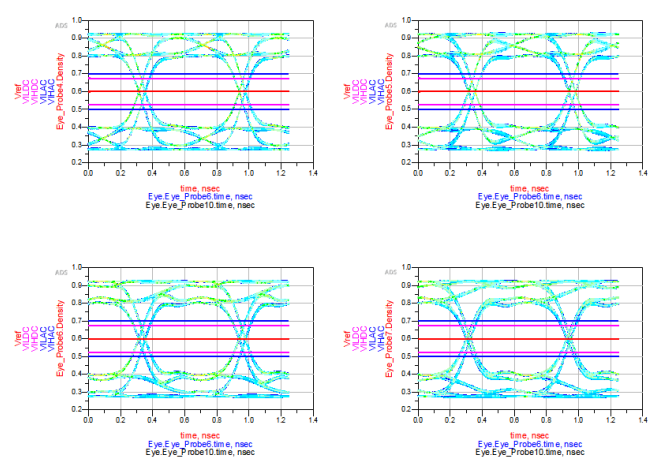

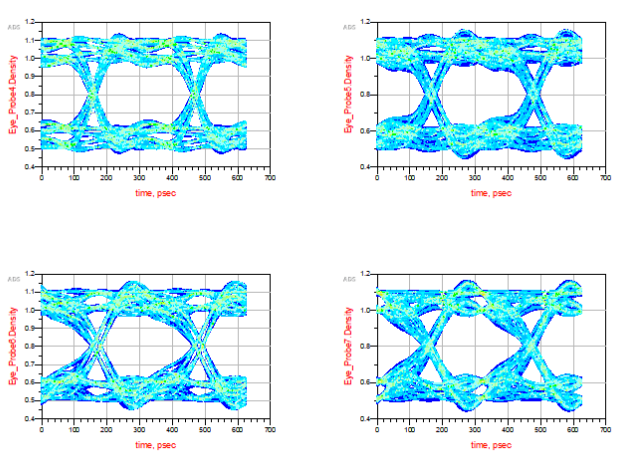

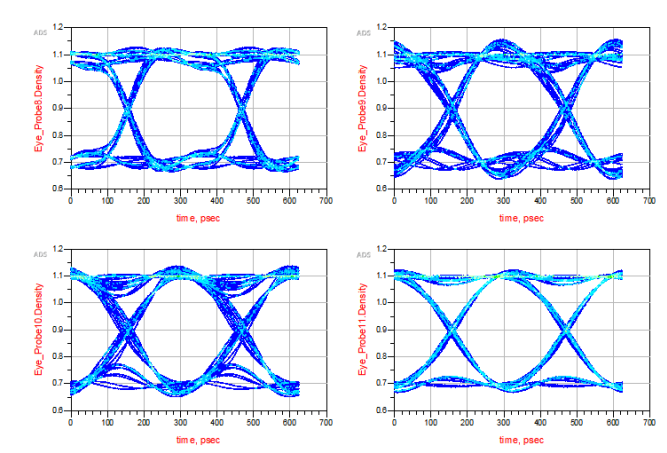

可以看到,此时波形还是比较好的,下面我们把1驱8的flyby结构改为,flyby+T型拓扑,也就是芯片对贴,来对比波形:

可以看到,此时信号质量已经大幅度提高;通过对比我们发现,在DDR的速率越来越高的同时,信号质量受到极大挑战,当然地址信号的内部端接也对信号质量的优化起到了很重要的作用。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高速电路信号完整性分析与设计—信号完整性仿真2009-09-12 0

-

信号完整性仿真应用2009-11-25 0

-

针对DDR2-800和DDR3的PCB信号完整性设计2012-12-29 0

-

DDR3内存的PCB仿真与设计2014-12-15 0

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 0

-

信号完整性小结2015-12-12 0

-

hyperlynx Sigrity信号完整性仿真Allegro平板电脑DDR3 PCB设计视频教程2018-08-25 0

-

【微信精选】针对DDR2-800和DDR3的PCB信号完整性设计(上)2019-07-30 0

-

怎么进行兼顾电源影响的DDR4信号完整性仿真2021-01-08 0

-

DDR2-800和DDR3的PCB信号完整性设计2011-07-12 1969

-

DDR2和DDR3在印制线路板(PCB)时信号完整性和电源完整性方案2018-02-06 2705

-

针对DDR2和DDR3的PCB信号完整性设计介绍2021-03-25 3984

-

信号完整性与电源完整性的仿真2021-09-29 1169

全部0条评论

快来发表一下你的评论吧 !