什么是门控时钟?如何生成门控时钟?

可编程逻辑

描述

什么是门控时钟?

Clockgating:在数据无效时,将寄存器时钟关闭的技术,能够有效降低功耗, 是低功耗设计的重要方法之一。门控时钟其实就是一个逻辑模块,在寄存器的输入数据无效时,将寄存器的输入时钟置为0,而此时寄存器值保持不变,此时没有时钟翻转,避免了动态功耗。

如何生存门控时钟?

在IC设计中,编写RTL代码的时候,只要采用合理规范的编码风格,即可以通过EDA工具自行产生门控时钟模块。

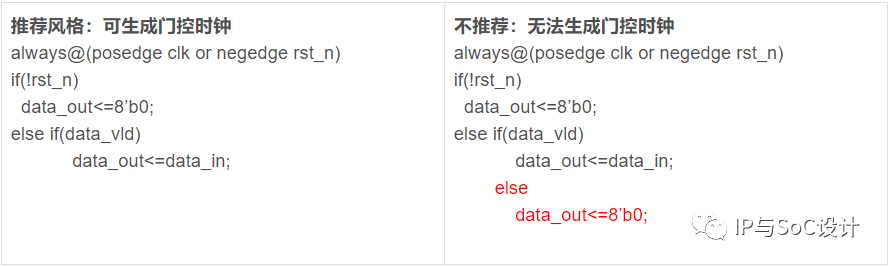

举例如下:

推荐的风格代码在else分支忽略,此时意味着在data_vld无效时data_out保持不变,此时状态与clock保持为0一致,因此具备生成门控时钟的条件,而不推荐风格代码,在data_vld无效时data_out为0,不符合门控时钟的状态,因此无法生成门控时钟。

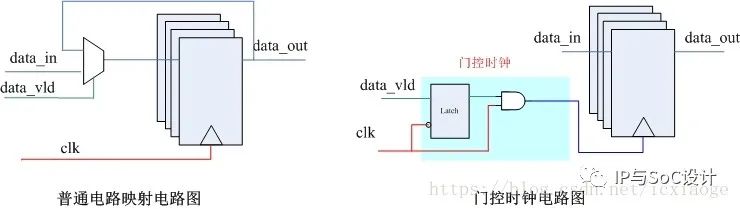

上图两个电路图均为推荐风格代码的映射电路图,右侧为采用门控时钟设计的电路图。采用推荐风格代码的代码即可以通过EDA工具自行插入门控时钟。

由于门控时钟逻辑具有一定的开销,因此数据宽度过小不适合做clockgating。一般情况下,数据宽度大于8比特时建议采用门控时钟。

实际芯片使用的门控时钟模块是后端厂家专门设计的模块单元,而不仅仅是图上的简单设计。

门控时钟设计:门控时钟模块

Gvi在IC设计中,经常会用掉门控时钟单元,在不使用某些模块的时候使用门控时钟单元锁定时钟,使得时钟不跳变,从而降低功耗。

1、门控时钟单元代码verilog

模块输入信号分别为输入时钟,clk_in,输出时钟clk_out,使能信号en。

当使能信号en==1时,表示时钟不锁定,输入信号直接输出,模块功能类似:assign clk_in = clk_out。

当使能信号en==0时,表示时钟锁定,输出时钟不跳变。

xxxxx_phy_lib_name是后端厂商提供的定制时钟门控单元

2、门控时钟单元使用注意事项:

1)使能信号en可配置,复位默认值必须为1,

2)驱动en的时钟不能是被锁定后的时钟,即驱动信号的时钟要求永远是存在的

module clk_gate

(

input clk_in ,

input clk_en,

output clk_out

);

`ifdef ASIC_DESIGN

wire clk_out ;

xxxxx_phy_lib_name xxxxx_phy_lib_name_u0

(

.O (clk_out ),

.phi (clk_in ),

.io (1'b0 ),

.i1 (clk_en )

);

else

`ifdef FPGA_DESIGN

assign clk_out = clk_in ;

else

reg clk_en_d1 ;

wire clk_out ;

always@(*) begin

if(!clk_in)

clk_en_d1=clk_en ;

end

assign clk_out= clk_en_d1&clkin;

`endif

`endif

endmodule

编辑:黄飞

-

fpga门控时钟问题2012-10-28 0

-

什么是门控时钟?2021-11-05 0

-

什么是时钟门控?如何去实线时钟门控的设计呢2022-12-19 0

-

基于门控时钟的CMOS电路低功耗设计2009-11-19 638

-

门控时钟与时钟偏移研究2011-09-07 947

-

门控时钟2016-05-10 659

-

通常有两种不同的时钟门控实现技术2021-06-13 2329

-

什么是门控时钟 门控时钟降低功耗的原理2021-09-23 12389

-

门控时钟实现低功耗的原理2022-07-03 1704

-

一文详解门控时钟2023-03-29 6132

-

FPGA原型平台门控时钟自动转换2023-05-23 1077

-

门控时钟检查(clock gating check)的理解和设计应用2023-06-19 1693

-

什么是时钟门控技术?为什么需要控制时钟的通断呢?2023-06-29 1375

-

为什么需要时钟门控?时钟门控终极指南2023-06-29 1115

-

XOR自门控与时钟门控的不同之处2024-01-02 524

全部0条评论

快来发表一下你的评论吧 !