应用笔记|半桥中点负压及应对策略

描述

本文主要阐述了在驱动芯片应用中,半桥中点出现的负压,分析其原因并且通过实验如何正确处理。

驱动芯片与VS负压的产品

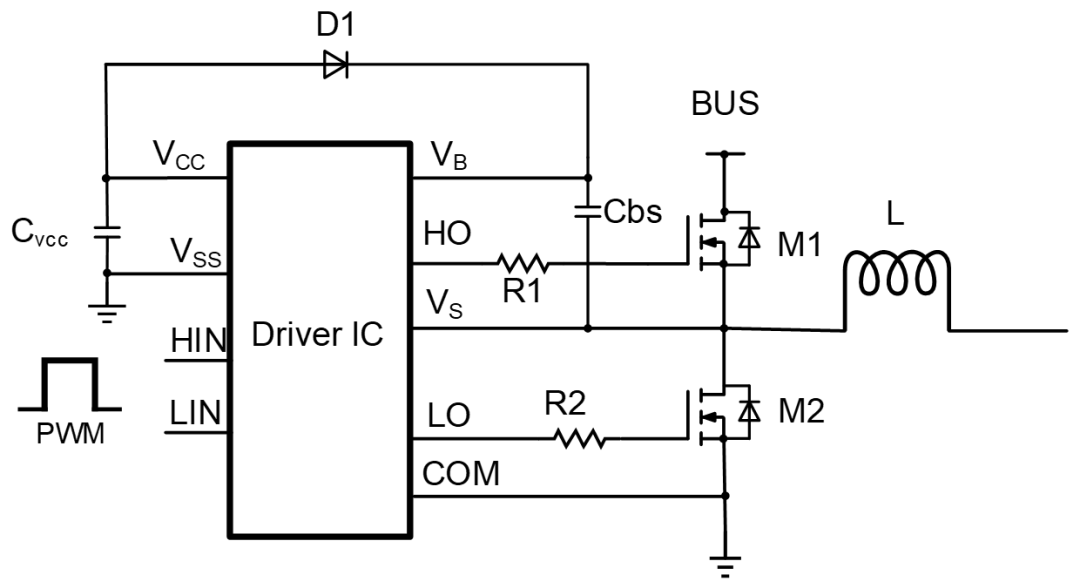

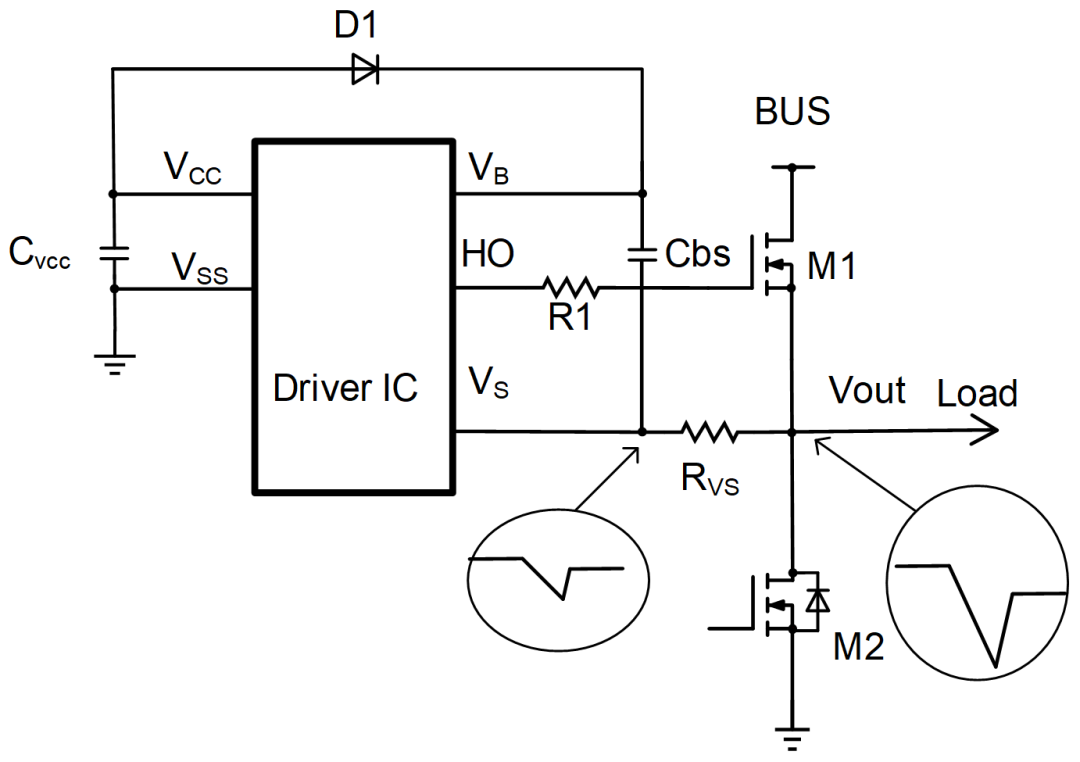

电力电子电路中,桥式电路应用非常广泛。图1显示了一个半桥驱动芯片驱动半桥电路的典型电路示意图。

图 1. 理想典型驱动芯片与半桥电路示意图

基本工作原理如下:当HIN为高时,输出HO为高,上管M1打开,电流从BUS通过M1流到负载端。当LIN为高时,输出LO为高,下管M2打开,电流通过M2续流。

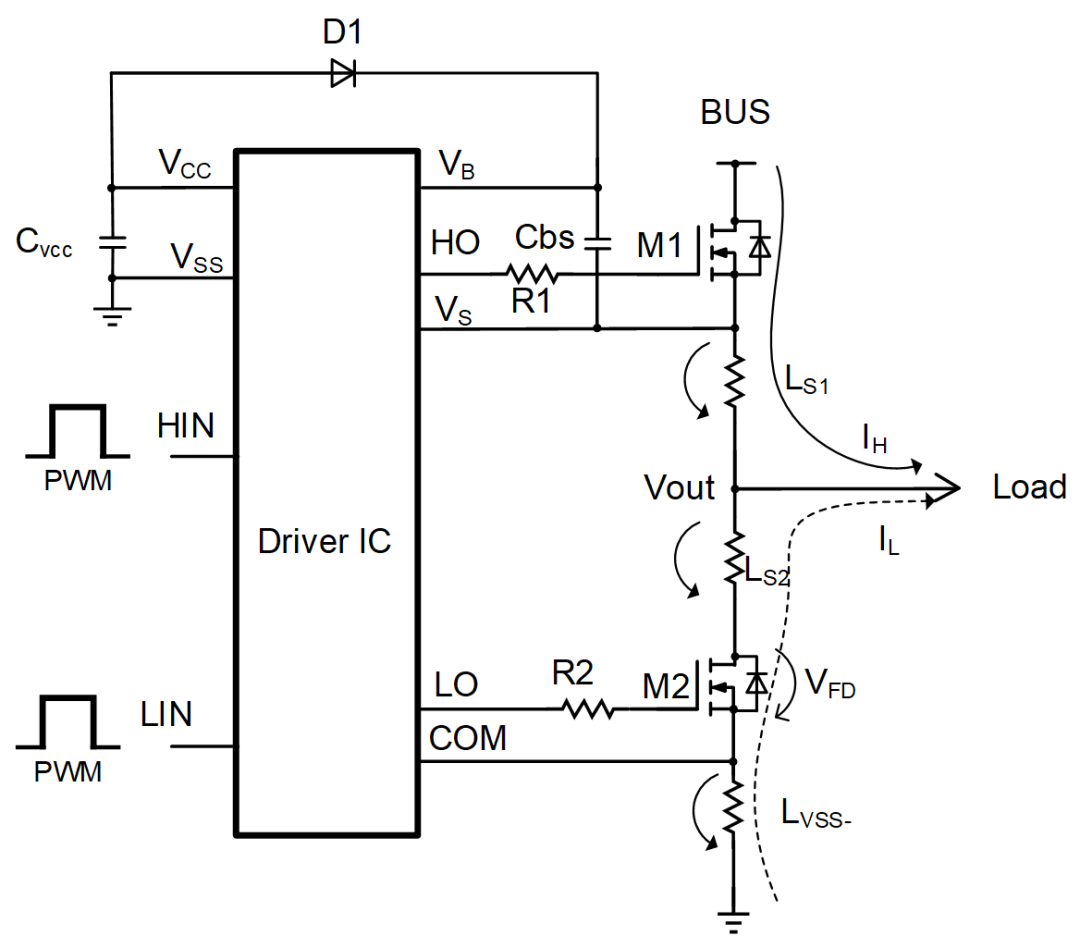

图 2. 带寄生电感导致VS电压低于VSS

由于线路上有寄生电感,在上管关断,下管开通的瞬态切换过程中,在寄生电感中将产生压降,导致VS端将产生负压,如图 2所示。VS负压端的大小,可由下述公式表示:

VS-VSS=-VFD-(LVSS-+LS2)×DIL/Dt-LS1×dIH/dt

由上述公式可知,VS的负压大小主要取决于如下参数:电流变化的斜率,寄生电感的大小。电流变化的斜率越大,尤其是在输出短路的情况下,VS负压也越大。寄生电感越大,VS负压也越大。

- 半桥中点负压及应对策略 -

VS负压的影响

一般在驱动芯片规格书中规定了最大的VS与VSS(COM)之间的负压和推荐的工作条件。

由于芯片内部含有寄生的二极管及latch up机制,当VS负压过大时,会导致芯片损坏或逻辑异常。

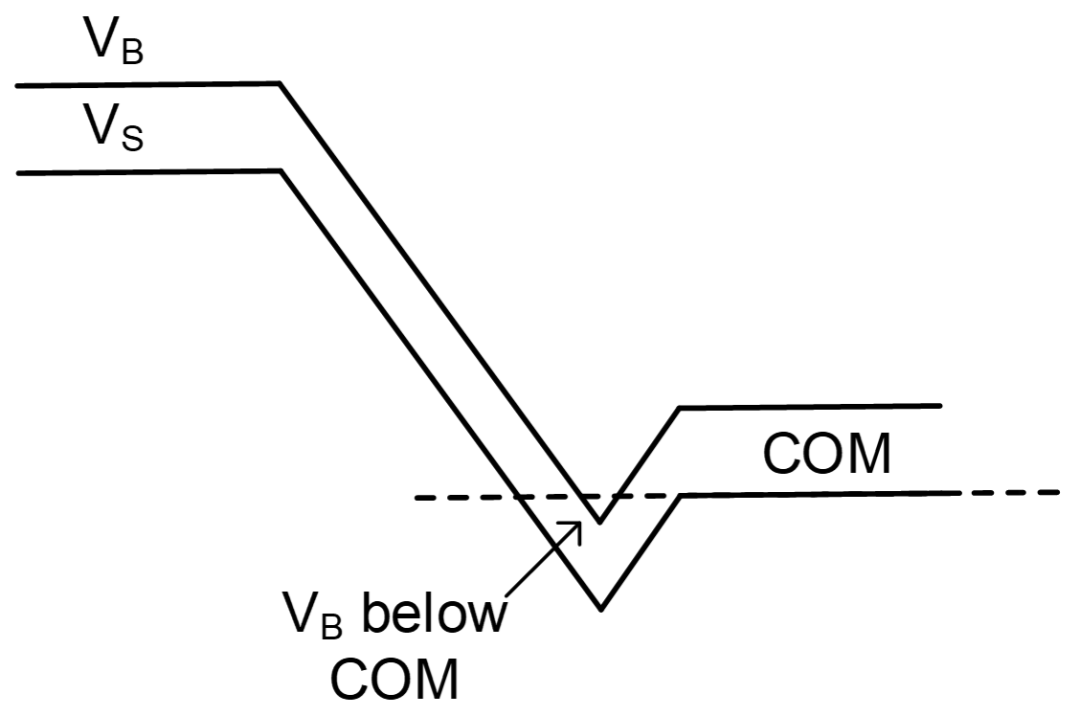

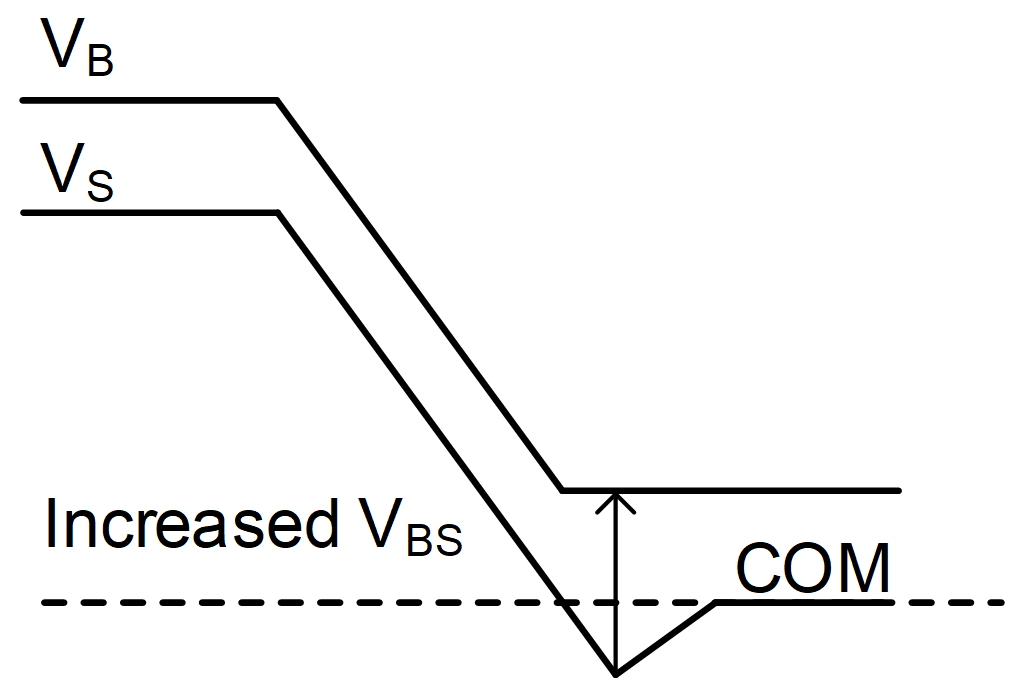

图 3. 高边的浮动电源与瞬态负压值VB,VS波形

如图3所示,当采用隔离的高边电源,当VS电压低于隔离电源Vbs电压时,导致VB电压低于COM端时,芯片内部二极管D3存在导通风险。

图 4. Bootstrap电路与瞬态负压值VB,VS波形

如图4所示,当高边电源采用bootstrap方式时,由于VS瞬间出现负压,将导致VB到VS的电压升高,当VBS电压大于芯片使用的最高值时,芯片也将损坏。VBS为浮动电源,考虑极端情况,上管导通时发生短路,一旦上管关断,短路大电流将通过下管体二极管。若此时的di/dt将使得VS非常小,VB与VS间电压超过芯片的使用范围。

VS负压幅值过大,有大电流从VS脚流出,会干扰芯片内部衬底,从而干扰内部电路对输入信号电平的正确判断,导致输出信号不受输入信号控制。

- 半桥中点负压及应对策略 -

VS负压对应策略

为了降低VS负压,优化PCB布局降低寄生电感是最有效的。PCB布局可以采用如下一些手段:如上下功率管的摆放尽量靠近;驱动芯片靠近被驱动的功率管以减少驱动芯片地到功率器件地。

另外一个途径是降低di/dt值。比较简单的办法是增大关断电阻R1,但以此同时,需要考虑可能会带来效率低下的问题。

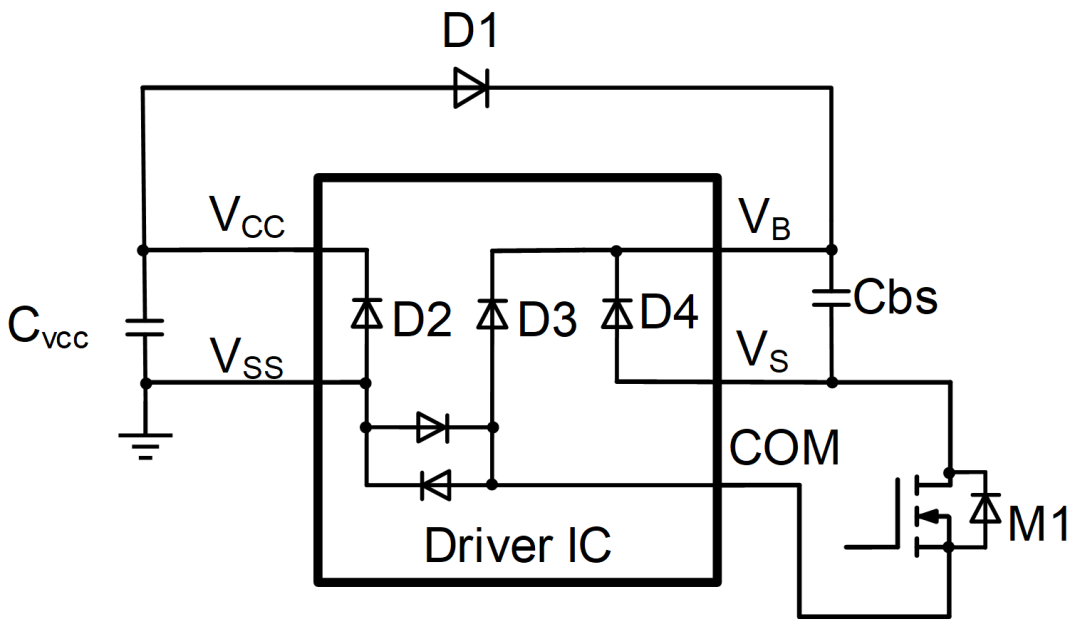

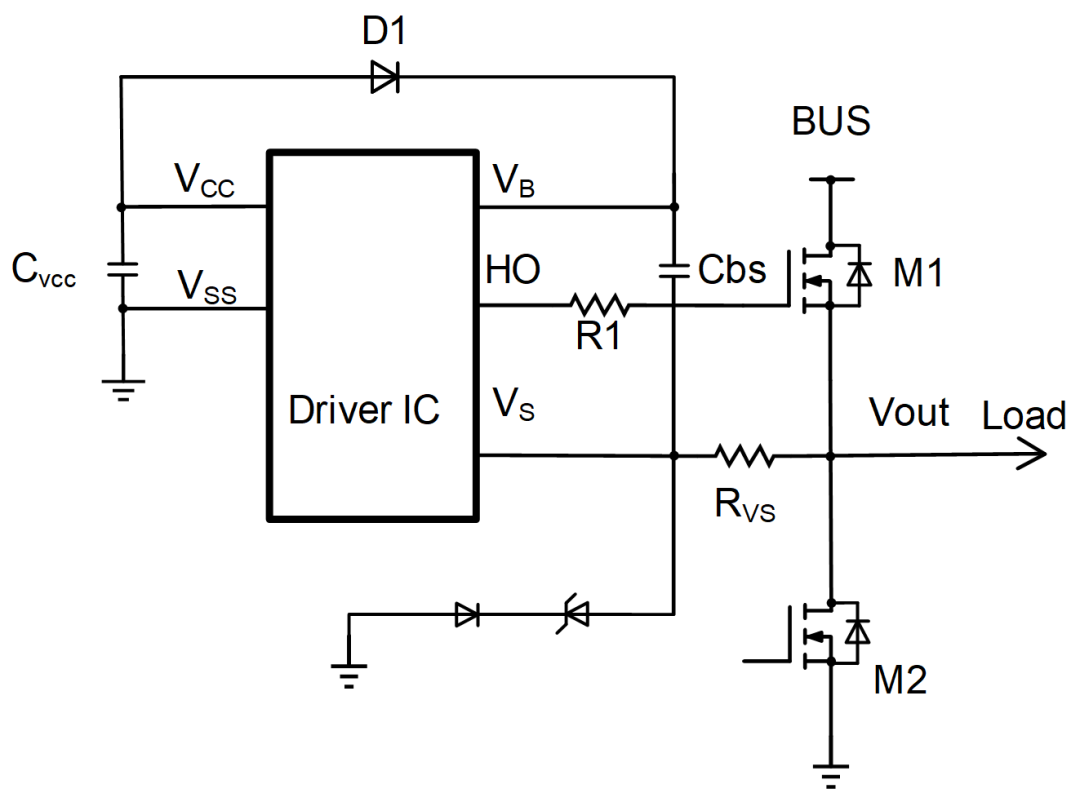

图 5. Rvs连接电路

图 6. VS端增加反向二极管和稳压管

为了使得VB与VS间的电压差小于VBS_ABSMAX,推荐在VS与VSS间加入一个稳压管与高压二极管串联。VB-VS≤VBS_ABSMAX,则稳压管耐压值选择需考虑:VZ≤VBS_ABSMAX-VCC。

- 半桥中点负压及应对策略 -

SLM2304S实验测试

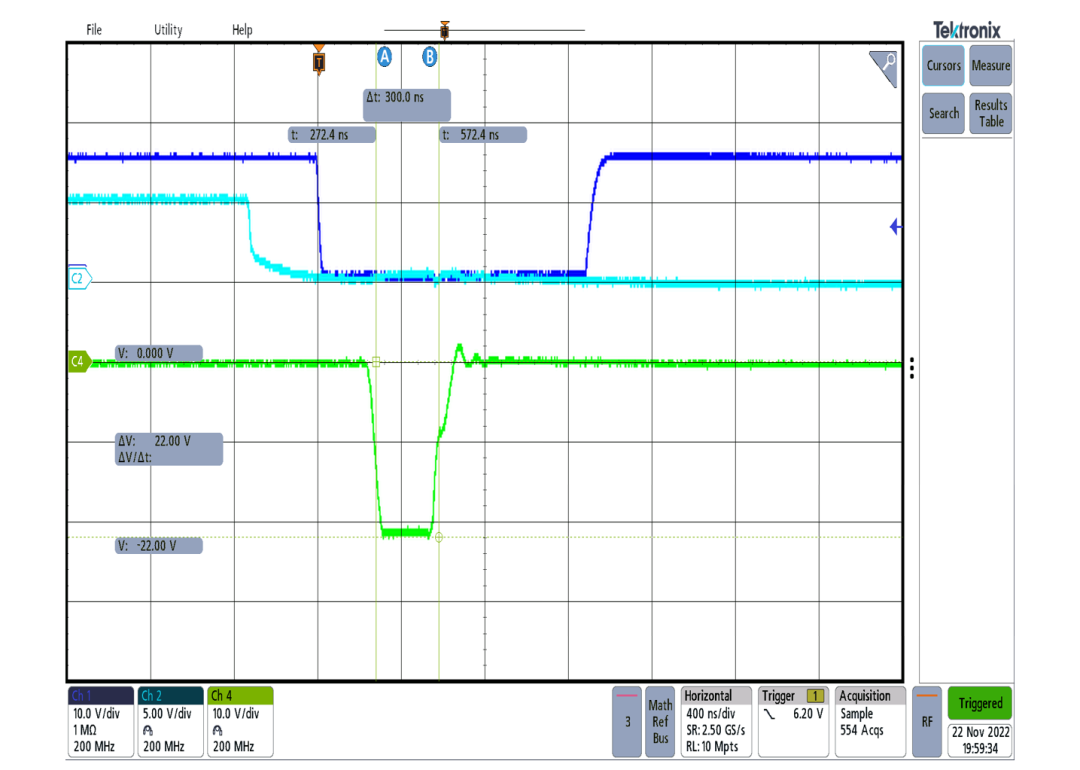

SLM2304S负压测试波形

图 7. SLM2304S VS 端没有串联电阻

-22V 300ns 负压波形

CH1: HO 丨 CH2: HIN 丨 CH4: VS

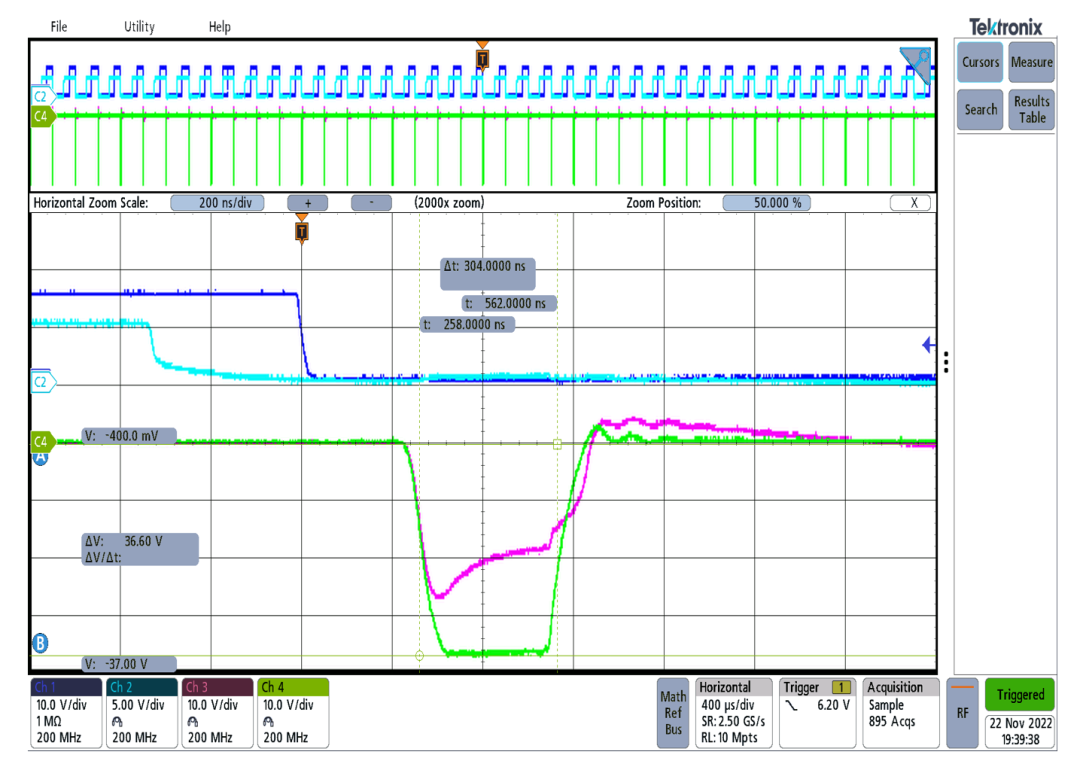

图 8. SLM2304S 串联电阻Rvs=10ohm

-37V 300ns 负压波形

CH1: HO 丨 CH2: HIN

CH3: 芯片端VS 丨 CH4: 半桥中点VS

从图7,图8对比可看出,VS端未串联电阻,在300ns,负压22V就出现了波形异常,而VS端串联了10Ω电阻,负压达到了37V才出现异常。另外如图8所示,在半桥中点 有37V的负压,而芯片端的VS电压最大值只存在了20V附近,大大降低了芯片端的负压值;从而有效的抑制了外部负压的数值,相当于提高了芯片的耐负压能力。

- 半桥中点负压及应对策略 -

测试总结

VS的负压大小与持续时间关系到驱动芯片的安全、正常工作。瞬态负压的大小主要取决于寄生电感,电流变化的速率。通过对外围电路的有效设计,可以增强驱动芯片在系统中对负压的耐受能力,使其能在恶劣工况中安全工作。

审核编辑:汤梓红

-

民营影视传媒公司应对策略分析2009-05-05 0

-

关于电压型半桥逆变中点电压偏移的问题2017-05-27 0

-

求助双电源供电半桥驱动中点电压很高,该怎么办?2018-03-22 0

-

什么是地线?应对地线干扰的对策有哪些?2021-04-20 0

-

90W笔记本电源半桥谐振电路2023-09-28 0

-

单片机破解的常用方法及应对策略2007-05-24 701

-

网络通信安全问题及其应对策略研究2016-03-28 457

-

三电平ANPC变流器中点电位控制策略研究2017-01-05 890

-

基于谐波观测器的ConergyNPC单相逆变器中点平衡策略_易灵2017-01-08 565

-

电磁兼容问题诊断及应对策略的详细资料说明2019-02-27 1036

-

EMI解析:影响、防护与应对策略?2024-03-12 188

-

解析EMI电磁干扰:原理、影响与应对策略2024-04-02 291

全部0条评论

快来发表一下你的评论吧 !