香农解码器:PWM DAC的(更快)替代品

描述

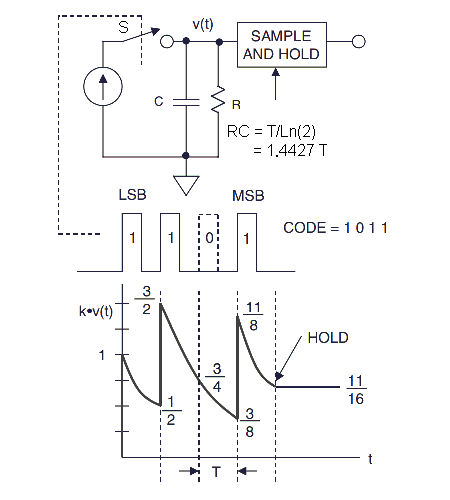

读者会认出著名的克劳德·埃尔伍德·香农(Claude Elwood Shannon),他被广泛誉为“信息论之父 ” ,也是许多发现和发明的鼻祖。其中包括一个优雅而开创性的(首次发表于1948年!)的DAC设计理念,称为香农解码器(SD),如图1所示(插图修改自《 数据转换手册 © 2005 ADI公司 》)。

图1香农解码器DAC。

图1香农解码器DAC。

在操作中,输入串行(LSB 优先)位串控制开关 S ,以便1位向电容器C添加一个电荷单位,而0位保持不变。位(在这个简单示例中总共四个)以时间间隔T 到达。因此,在4T结束时,C上累积的最终电压V表示字符串的数字内容。使V与字符串表示的二进制数N成比例的非常简单(感谢香农的天才)技巧是

广告

RC = T/Ln(2)。 这导致C上累积电压的一半在每个间隔T期间放电,从而提供正确的数模转换所需的二进制位权重。然后,S&H在4T下捕获C上存在的最终结果。仅此而已。我们仅使用开关、单级RC和S&H,仅使用四位时间就完成了4位DAC转换。

广告

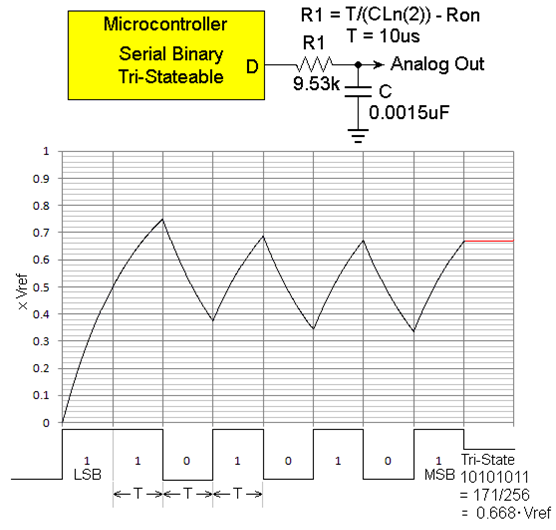

图 2显示了使用 1948 年以来出现的设备时 8 位 SD 的外观。请注意,它与基本的PWM DAC非常相似,仅由典型的通用输出位D和单级RC( R + Ron)C = T/Ln(2) 组成。导通项提供输出端口导通电阻的校正,典型值为20Ω至200Ω。我们稍后会看到为什么罗恩很重要。假设示例 8 位串行串 = 10101011 = 171, T =10μs, C =0.0015μF, Ron =120Ω, R =9.53kΩ,Vref = 5V 逻辑电源, 模拟输出 = 171/256 * 5V = 3.34V 。

图2现代香农解码器实现。

所需的S&H功能在模拟输出累积后只需三态D即可免费提供,允许电容器C保持最终电压,从而成为自己的S&H。

以前我声称SD是PWM的更快替代品。嗯,是吗?8位PWM的基本周期为256个时钟周期,为了将纹波抑制到LSB电平,RC滤波器时间常数需要等于~64个PWM周期,并且还需要一个Ln(256)= 5.5个时间常数才能稳定到1 LSB。PWM DAC的总转换时间为256 645.5 = 90,112个时钟周期,用于转换、滤波和建立到最终的8位值。

同时,8位SD仅在8个T周期内完成所有这些工作,显然产生了90,112/8 = 11,264:1的SD与PWM速度比,使用与基本PWM相同的零件数完成!

但这真的是一个公平的比较吗?嗯,不完全是。

首先,关于速度,PWM时钟周期通常会在专用的片上计数器定时器硬件中产生,而输出端口位的SD位移位和最终三态可能需要一些软件交互。这种差异可能会使SD比特率比PWM时钟慢。也许慢 10 倍。因此,SD与PWM速度比的更现实估计可能更接近1,100比1,而不是11,000比1。

其次,关于器件数量,需要考虑以下因素:虽然PWM会持续自动刷新其输出,但图2所示的基本SD则不会。图2每隔几毫秒就需要运行一个转换周期,以刷新C的电荷,抵消电压下降并保持稳定的输出。当然,在这些转换过程中,模拟输出将 不稳定 ,从而产生负载将被视为瞬时输出毛刺。

有些负载可以容忍这种周期性干扰,但许多负载不会。避免故障是可能的,但要做到这一点,必须增加零件数量。图 3提出了一种可能的解决方案:

图3辅助PWM可防止SD输出下降。

通过将“维持器”PWM设置为与SD相同的输出电压来补充SD的速度,以保持SD最初(快速)设置的相同电容电荷。

该解决方案仍然不够完美,因为SD和PWM时间常数之间的大比率意味着R1和R2之间的比率同样大,对R2施加了高电阻以获得足够的纹波抑制,因此模拟输出的稳态驱动能力非常有限**。**当然,每当SD转换序列设置新的输出电压时,仍然存在输出毛刺。

图4显示了解决这些问题的完整方法,通过实施两个S&H转换/保持电容,通过U1c 切换 ,其中一个提供S&H功能(C0/1作为X/Y Select = 0/1)和恒定输出电压,而另一个通过U1a和U1b执行下一个DAC转换。于是他们转换角色,八达亚达等等。

图4切换的标清。

图4拓扑的另一个特点是能够接受独立于逻辑电源和地的基准电压输入(+ Vref , -Vref )。这允许更好的DAC精度,而不是依赖逻辑电源的(通常有限的)稳定性,如果-Vref为负,则双极性(-Vref至**+Vref**)输出范围。

它仍然只需要四个部分。

SD 具有固有的可编程分辨率。无需修改任何电路即可容纳任何长度的位串(6、10、12 等)。此外,由于SD转换时间与位串长度(n)成线性比例,而PWM转换时间与 2^n^ ,SD 的速度优势只会随着字符串长度的增加而变得更好。

SD 精度取决于 RC 时间常数与位间隔 T/Ln(2) 之间的精确匹配。这两个数字之间的差异将导致位权重与正确的2.0不同,单调性和微分线性度因此受到影响。因此,建议使用精密金属膜电阻器和零温度系数C0G或NPO电容器,以及如前所述,对SD信号路径中开关元件的阻抗( Ron )进行R校正。

图5显示了RC时间常数误差从0%( RC = 1.44269 T)到10%( RC = 1.58696 T )对转换结果的影响。

图50% 至 10% RC 误差的影响。

审核编辑 黄昊宇

-

寻找松下TX2-12V的替代品2012-11-17 0

-

寻求Ubuntu13系统下软件替代品……2013-10-26 0

-

如何寻找芯片IS61LV51216的替代品2016-05-17 0

-

MMBFJ176替代品??2017-07-21 0

-

IF增益可控放大IC,即MC1350的替代品2017-08-22 0

-

请问仪表放大器AD624有没有便宜的完全兼容的替代品?2019-01-23 0

-

电解电容廉价替代方案(寻找红宝石电容替代品)2019-04-27 0

-

是否有TDA2003的替代品2019-08-05 0

-

如何使用ISP1763作为替代品?2019-09-04 0

-

如何找到PIC18F4620的替代品2020-04-10 0

-

Commodore 6540 ROM的替代品2022-09-02 0

-

什么是STM32MP157D微处理器的最佳替代品呢?2022-12-14 0

-

请问一下有stm32f429iit6的替代品吗?2023-01-05 0

-

MC908JL3ECDWE的替代品是什么?2023-06-05 0

-

ADC和DAC、DSP!解码器和独立DAC2019-05-06 25114

全部0条评论

快来发表一下你的评论吧 !