PCB布线规则和技巧图解(上)

PCB布线规则和技巧图解(上)

描述

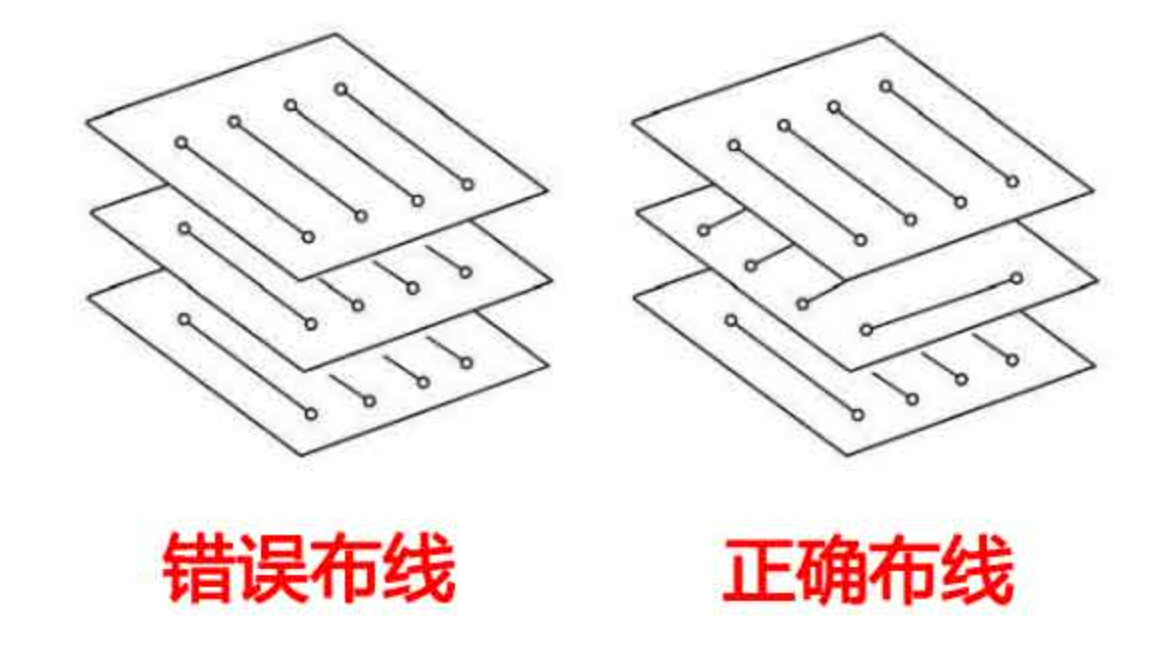

一.控制走线方向

输入和输出端的导线应尽量避免相邻平行。在 PCB 布线时,相邻层的走线方向成正交结构,避免将不同的信号线在相邻层走成同一方向,以减少不必要的层间窜扰。当 PCB 布线受到结构限制(如某些背板)难以避免出现平行布线时,特别是在信号速率较高时,应考虑用地平面隔离各布线层,用地线隔离各信号线。相邻层的走线方向示意图如下图。

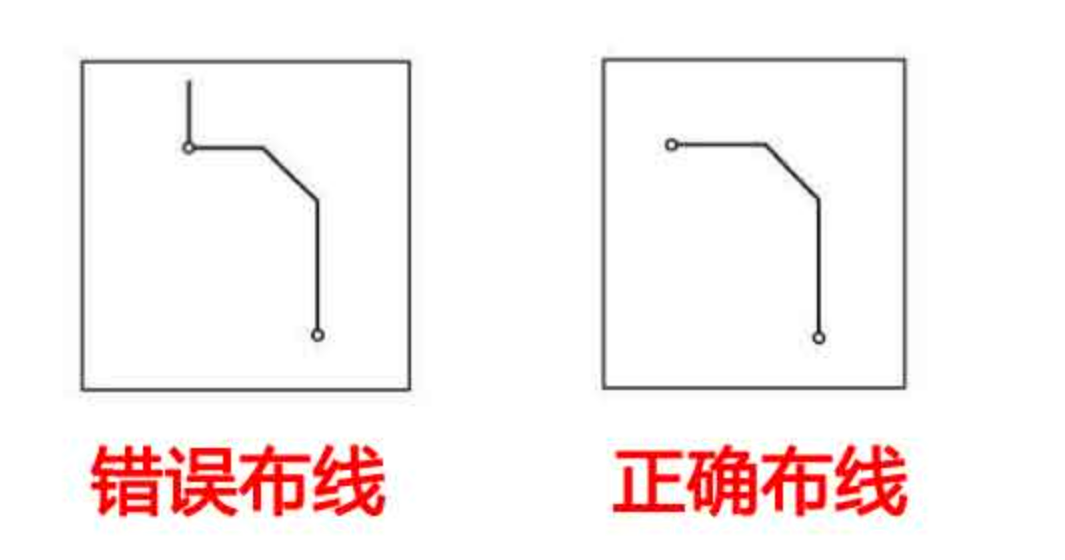

二.检查走线的开环和闭环

在PCB布线时,为了避免布线产生的“天线效应”,减少不必要的干扰辐射和接收,一般不允许出现一端浮空的布线形式,否则可能带来不可预知的结果。

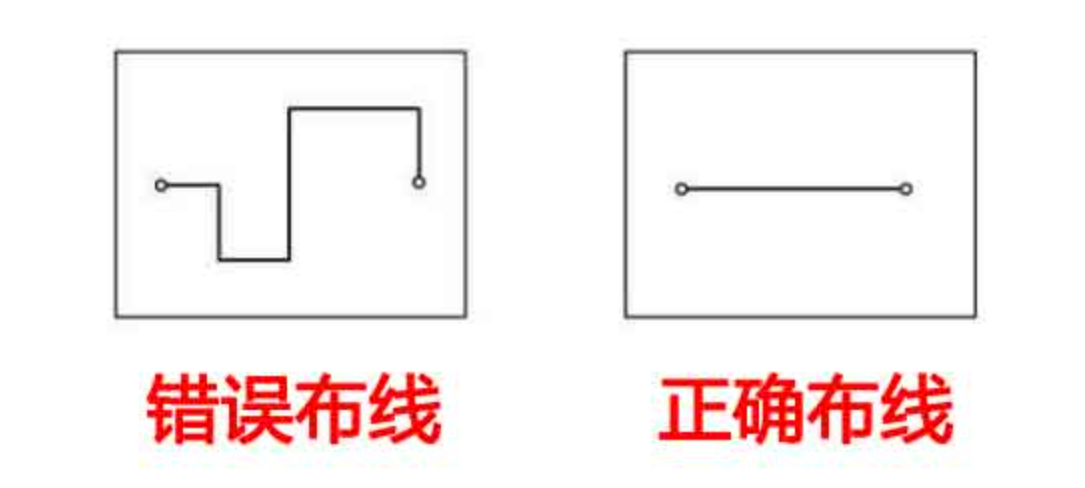

要防止信号线在不同层间形成自环。在多层板设计中容易发生此类问题,而自环将引起辐射干扰。

三.控制走线的长度

1.使走线长度尽可能的短

在 PCB 布线时,应该使走线长度尽可能的短,以减少由走线长度带来的干扰问题

2.调整走线长度

数字电路系统对时序有严格的要求,为了满足信号时序的要求,对PCB上的信号走线长度进行调整已经成为PCB设计工作的一部分。

走线长度的调整包括以下两个方面的要求。

a.要求走线长度保持一致,保证信号同步到达若干个接收器。有时在PCB上的一组信号线之间存在着相关性,如总线,就需要对其长度进行校正,因为需要信号在接收端同步。调整方法就是找出其中最长的那根走线,然后将其他走线调整到等长.6.控制两个器件之间的走线延迟为某一个特定值,如控制器件A、B之间的导线延迟为1ns,而这样的要求往往由电路设计者提出,但由PCB工程师去实现。需要注意的是,在PCB上的信号传播速度是与PCB的材料、走线的结构、走线的宽度、过孔等因素相关的。通过信

号传播速度,可以计算出所要求的走线延迟对应的走线长度。

走线长度的调整常采用的是蛇形线的方式

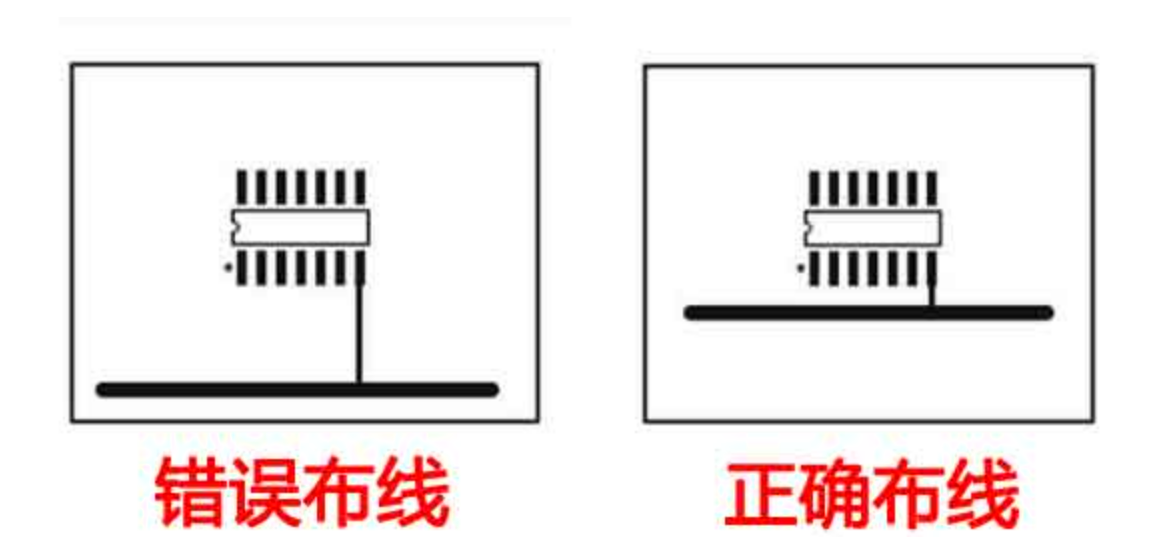

四、控制走线分支的长度

在PCB布线时,尽量控制走线分支的长度,使分支的长度尽量短,另外一般要求走线延时tdelay≤trise/20,其中trise是数字信号的上升时间。走线分支长度控制示意图

-

PCB布局布线规则2013-08-06 0

-

PCB布线规则2012-06-06 0

-

PCB的布局布线规则2021-11-11 0

-

pcb布线规则2007-12-10 24603

-

PCB布线规则之PCI卡篇2009-11-18 1123

-

PCB布线规则详解解说2009-11-24 1768

-

EMI相关PCB布局布线规则2016-07-26 1142

-

高频在PCB中的布线规则2016-07-26 817

-

PCB绘制-布局布线规则2016-07-26 1158

-

高频PCB板布线规则2016-07-26 1113

-

PCB手动布线规则2016-08-16 1467

-

DDR2_DDR3_SDRAM,PCB布线规则指导2017-10-31 1630

-

PCB布线规则和技巧图解(下)2022-12-16 3636

-

「实用干货」7条实用的PCB布线规则,可收藏2023-02-01 952

-

7条实用的PCB布线规则2022-09-30 1670

全部0条评论

快来发表一下你的评论吧 !