PCB板上的差分传输线长度匹配问题

PCB设计

描述

问题的由来

一台设备在输入HDMI信号时测试辐射特性,主要是HDMI的CLK频率及其倍频的辐射强度易超标,有时换一条HDMI线缆或者换一台作为信源的PC后,被测机器的测试结果也会有数dB甚至十多dB的变化,一时让很多硬件工程师头疼不已。

问题的分析

造成HDMI辐射超标的原因有多种可能,就不一一分析了,这里只重点谈谈与差分线传输线长度差有关的问题。

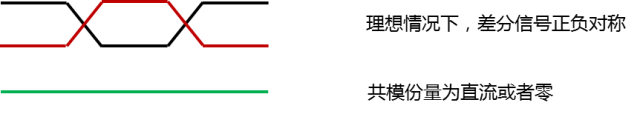

理想情况下,差分信号是正负对称的,其共模份量为零或者只有直流份量,如图1所示。如果差分线的正负传输线长度不等,造成传输时间不一致,实际上就是信号在时间轴上的不对称,在终端负载电阻上就能观察到图2所示的波形。显然此时的正负波形不能严格对称,差分电路中的正负电流无法抵消,于是其电源中就有共模电流份量在流动。研究过EMI的人都知道,共模辐射是最难对付的。

图1

图2

差分信号转共模信号的现象,在李玉山教授翻译的Bogatin的《信号完整性》一书中第11.15章和11.16章中对此有详细的解释。书中给出的指导原则是差分线的长度偏差必须在上升沿空间拓展的20%以内,如果上升时间是100ps,那么长度差应该控制在100mil以内(以FR4材质的PCB为例),否则会引起EMI问题。

用实验来验证

让我们先用实验来验证一下上面的分析,看看能否能证实这个推断。

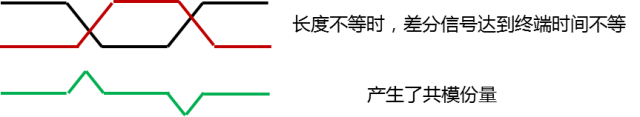

实际测量一下差分信号,如图3所示,图中最下面一条图形为共模电压份量,很明显在波形正负边沿交叉的时候的确有脉冲输出。

图3

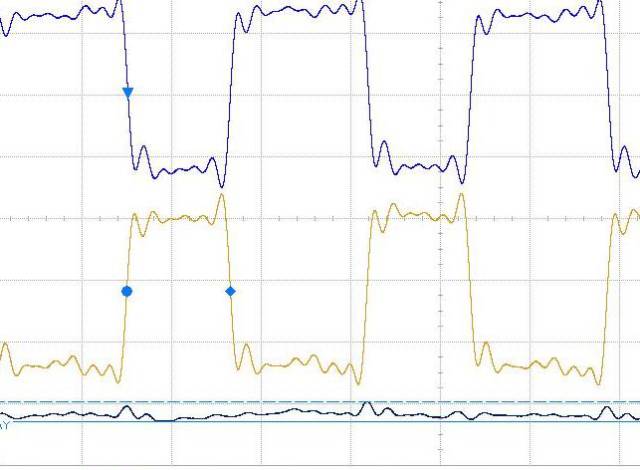

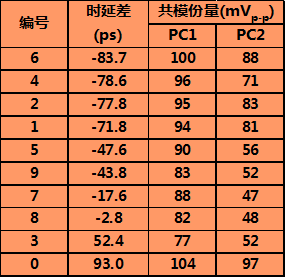

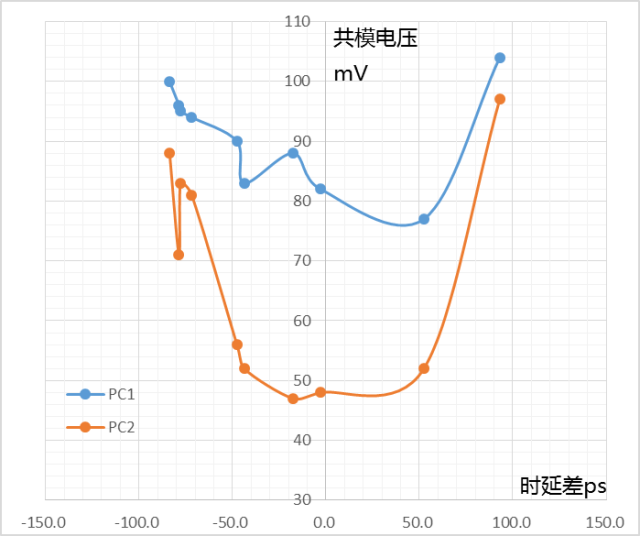

我们随机选取了10条HDMI线,使用网络分析仪测试了每条线的CLK差分线的时延差,因为时延差直接反映了正负传输线的长度差,10条线的时延差如表1中所示。

表1

接下来,分别选两台EMI测量用PC作为HDMI信源,接上负载,然后测量每条线所产生的共模电压的峰峰值,如表2中所示,将它们绘制在图4中。

表2

从图4中,我们可以看到直观的看到:只要时延差(横轴表示)大的,无论是正值还是负值,其共模电压幅度(纵轴表示)均较高,且两台电脑呈现相同的趋势。这就是说时延差大的,也就差分线长度匹配差异越大,产生的共模电压越高。

图4

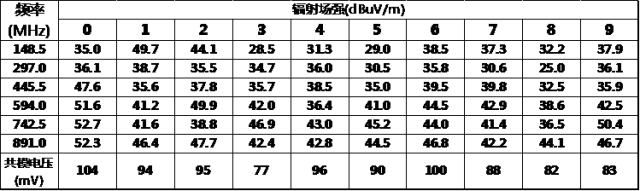

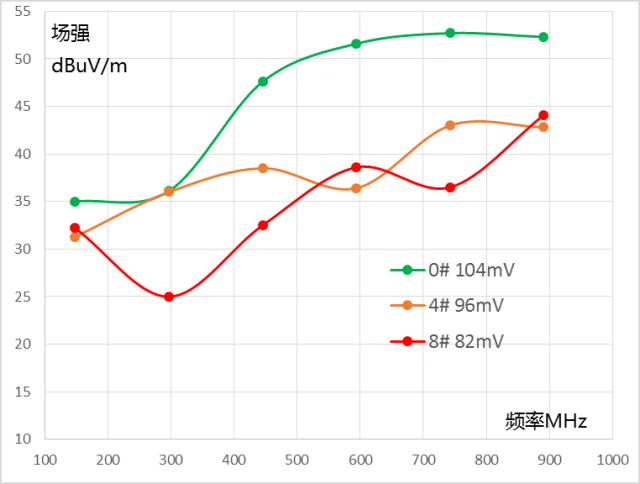

在随后的辐射测试中,保持测试电脑(PC1)及被测机器不变,依次更换10条HDMI线,其结果印证了我们的预计,数据详见表3。为了图形的清晰,选择共模电压最小、中间、最大的8#、4#、0#这3条线的测试数据用图形表示,如图6所示。0#线时延差最大,辐射也最大;8#线时延差最小,辐射也最小。绝大部分频率点上的辐射特性强弱与共模电压大小几乎都有直接的对应关系。

表3

图6

以上实验说明差分线长度的不匹配程度越大,共模辐射也越大,也就解释了换用不同的HDMI线其辐射测试结果相差甚远的原因。

关于眼图的X轴抖动

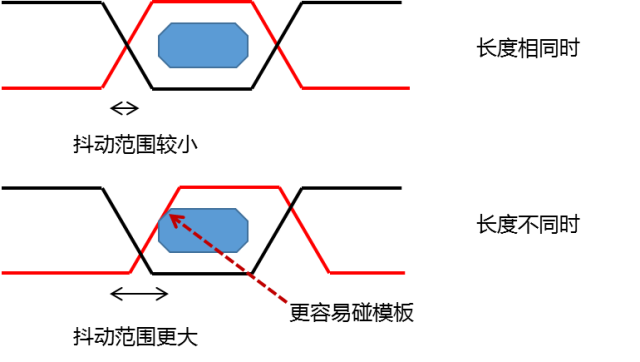

通过前面的分析,我们自然会联想到信号在时间轴上的不对称一定会影响眼图的质量,如X轴上的抖动范围会更大,因为差分信号的边沿更容易触碰模板了,如图7所示。

图7

需要注意的是,长度匹配是指芯片到芯片(即差分信号发送端到接收端)之间的链路,并不是对PCB走线的单一要求。经与IC供应商了解后发现,其内部的差分线金线的长度差有时可以达到40-60mil这样的数值,显然是不能被忽略的。在芯片供应商提供了IC内部每条差分线金线的长度后,要求PCB工程师根据此数据将差分走线的进行长度匹配,总偏差控制在10-20mil(注意:是同一对差分线的正负线长度差,不是差分对与差分对的长度差)。

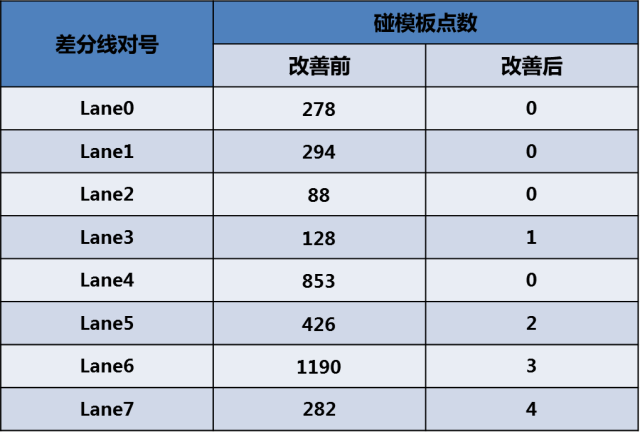

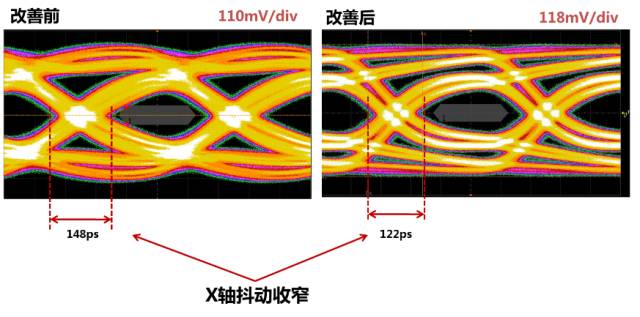

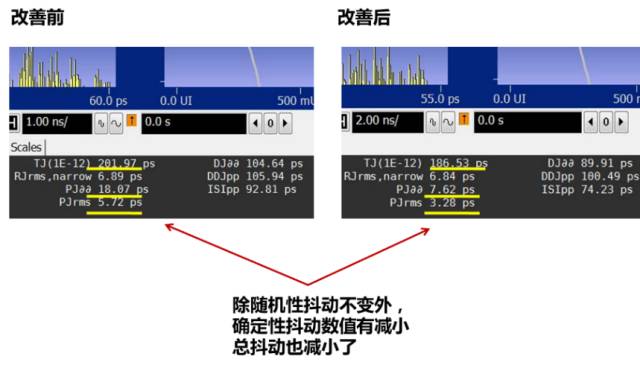

某产品在仅仅改善了差分线的长度匹配之后,眼图测试中触碰模板的数量便大幅度得到改善,如表4所示,水平轴上的抖动也从148ps降低到122ps,确定性抖动与总抖动也有不同程度的下降,如图8所示。

表4

图8

小结

差分电路的好处是在于对称,包括传输线的长度对称,倘若做不到,差分信号转共模信号后会带来EMI和眼图等问题。上升沿速度越快,对差分长度匹配要求越高。

对于在PCB板上的差分传输线,必须考虑差分芯片收发整个链路的长度差,这一点在设计中常常被忽略。

信号上升沿在100ps级别时,笔者认为Bogatin提出的100mil匹配要求(FR4材质PCB)对于EMI来说还是有很大风险的,差分线的长度匹配控制在10-20mil以内比较稳妥。

参考文献

【1】伯格丁(Bogatin)著,李玉山等译,信号完整性分析,电子工业出版社,2005

【2】约翰逊(Howard Johnson)等著,高速数字设计,电子工业出版社,2010

【3】劳迪(Geoff Lawday)等著,信号完整性指南:实时测试、测量与设计仿真,电子工业出版社,2010

【4】邵鹏著,高速电路设计与仿真分析:Cadence实例设计详解,电子工业出版社,2010

作者简介:

何庆松,资深硬件工程师。

何庆松,1987年毕业于安徽大学物理系,曾任安庆市无线电厂设计所、中山市爱多电器有限公司研究院、深圳市三诺电子有限公司设计所、TCL多媒体AV所&研发中心等单位的设计师、部门经理等职务。主要从事电视、电声、仪器设备等产品的设计开发,擅长模拟电路及整机系统架构设计。

编辑:黄飞

-

传输线的特性阻抗分析2009-09-28 0

-

max485差分传输匹配电阻2014-12-31 0

-

避免传输线效应的方法有哪些?2017-06-08 0

-

PCB传输线参数2018-09-03 0

-

印制电路板传输线信号损耗测量方法2018-09-17 0

-

PCB传输线之SI反射问题的解决2018-09-21 0

-

请问pcb板阻抗与导线长度有关吗2019-01-30 0

-

如何实现Altium PCB设计中的内部走线长度?2020-08-12 0

-

差分线传输线长度差有关的问题2020-11-04 0

-

什么是传输线?PCB的传输线结构是如何构成的?2021-06-29 0

-

PCB设计之实例解析传输线损耗2022-11-10 0

-

pcb如何在走线长度匹配中考虑整个信号带宽2021-01-05 3735

-

工程师头疼的差分线传输线长度差问题资料下载2021-04-02 734

全部0条评论

快来发表一下你的评论吧 !