高速PCB并行总线和串行总线

高速PCB并行总线和串行总线

描述

作为一名PCB设计工程师,具备一些高速方面的知识是非常有必要的,甚至说是必须的。就信号来说,高速信号通常见于各种并行总线与串行总线,只有知道了什么是总线,才能知道它跑多快,才能开始进行布线。

总线

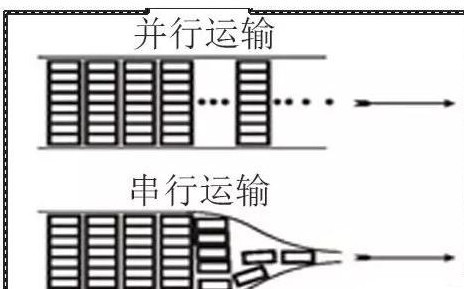

总线是两个或两个以上设备通讯的共享物理通路,是信号线的集合,是多个部件间的公共连线,用于在各个部件间传输信息。接照工作模式不同,总线可以分为两种类型:一种是并行总线,一种是串行总线。

01并行总线

同一时刻可以传输多位数据,好比是一条允许多辆车并排开的宽敞道路,而且它还有双向单向之分。

02串行总线

在同一时刻只能传输一个数据,好比只容许一辆车行走的狭窄道路,数据必须一个接一个传输、看起来仿佛一个长长的数据串,故称为“串行”。

并行传输最好的例子就是存储芯片DDR,它是有一组数据线D0—D7,加DQS,DQM,这一组线是一起传输的,无论哪位产生错误,数据都不会正确的传送过去,只有重新传输。所以数据线每根线要等长,必须得绕几下才行。

串行数据就不一样,数据是一位一位的传,位与位之间是没有联系的。不会因为这位有错误,使下一位不能传输。并行数据是一组数据其中一位不对,整组数据都不行。

布线要求

01并行总线的布线要求

(1)建议总线优选内层布线,尽量增大与其它布线的间距。

(2)除特殊要求外,单线设计阻抗保证50欧,差分设计阻抗保证100欧。

(3)建议同一组总线保持布线基本等长,与时钟线遵循一定的时序关系,参照时序分析强果控制布线长度。

(4)建议尽可能的靠近本组总线的I/O电源或GND参考平面,保证参考平面的完整性。

(5)上升时间小于1ns的总线,要求有完整参考平面,不得跨分割。

(6)建议低位地址总线参照时钟布线要求。

(7)蛇形绕线线的间距不得小于3倍线宽。

02高速串行总线的布线要求

频率高于100Mbps的串行总线,在布线设计中除遵循并行总线通用的串扰控制、布线规则之外,还需额外考虑一些要求:

(1)高速串行总线需要考虑布线的损耗,确定线宽线长。

(2)建议一般情况下线宽不小于5mil,布线尽量短。

(3)高速串行总线除Fanout过孔外,尽量不要打孔换层。

(4)串行总线所涉及的插件管脚,速率达3.125Gbps以上时,应优化反焊盘以减少阻抗不连续带来的不射影响。

(5)建议高速串行总线布线换层时,选择使用过孔Stub最小的布线层,对于到连接器的信号,在布线空间有限时,过孔Stub短的布线层,优先分配给发送端。

(6)建议速率达3.125Gbps或以上时,信号过孔旁打地孔,AC藕合电容也要对反焊盘特殊处理。

(7)如果高速信号过孔采用背钻处理,需要考虑电源地平面通流能力变小,以及通流瓶颈变窄后的滤波环路电感增大带来的影响。

(8)高速信号避开平面层的分割线,信号线边缘与分割线边缘空间水平间距保证3W。

(9)收发两个方向的高速信号,不能交叉在一起走线。

审核编辑:汤梓红

-

串行总线会替代并行总线吗?#高速接口我是Coder 2021-08-11

-

什么是基于FPGA的ARM并行总线?2019-09-17 0

-

高速串行总线与并行总线的差别是什么?2021-05-12 0

-

高速串行总线的常用测试码型2011-01-04 3922

-

串行总线和并行总线的区别2017-11-13 40828

-

并行总线有哪些?串行总线有哪些?2017-11-13 79354

-

串行总线是什么?(优点和作用)2017-11-13 25714

-

了解了串行/并行高速信号,你才能开始PCB布线2019-02-05 2232

-

PCB设计必备知识:并行总线VS串行总线2020-07-29 2458

-

并行总线和高速串行总线的布线要求2020-10-21 4477

-

什么是串行总线和并行总线?2021-06-11 16576

-

串行总线的优缺点优点2021-10-15 7621

-

从以太网到高速串行总线,pcb绝缘阻抗标准指南2023-09-19 672

-

并行总线和串行总线的区别2023-12-07 2006

全部0条评论

快来发表一下你的评论吧 !