ADC时钟极性与启动时间的关系

描述

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样时钟时的预期启动时间长。 令人惊讶的是,这种延迟的原因往往是错误的启动 外部施加的ADC采样时钟的极性。

许多高速ADC具有以下采样时钟输入 特性:

微分

内部偏置至设定的输入共模电压 (VCM)

设计用于交流耦合到时钟源

此讨论适用于具有具有 这些属性。

差分ADC时钟输入缓冲器通常具有设计输入切换 阈值偏移。如果没有这样的偏移,切换阈值将 发生在0V差分时。在没有偏移的时钟缓冲器的情况下 在非驱动和交流耦合的情况下,时钟输入(CLK+ 和 CLK–)将 每个器件均在内部上拉至共模电压。在这种情况下, CLK+ 上的直流电压和 CLK– 上的电压是相同的,这 表示差分电压等于0V。

在输入端没有信号的理想世界中,时钟缓冲器不会 切换。实际上,电子系统中总是至少存在一些噪声。 在此假设情况下,输入切换阈值为0V,任何噪声 在输入端将超过时钟缓冲器的切换阈值并导致 无意中切换。

当时钟中设计了足够的输入切换阈值偏移时 缓冲区,相同的条件不会导致切换。因此,设计 交流耦合差分时钟的切换阈值电压的偏移 缓冲器是有益的,因此,时钟缓冲器通常包括 切换阈值偏移。

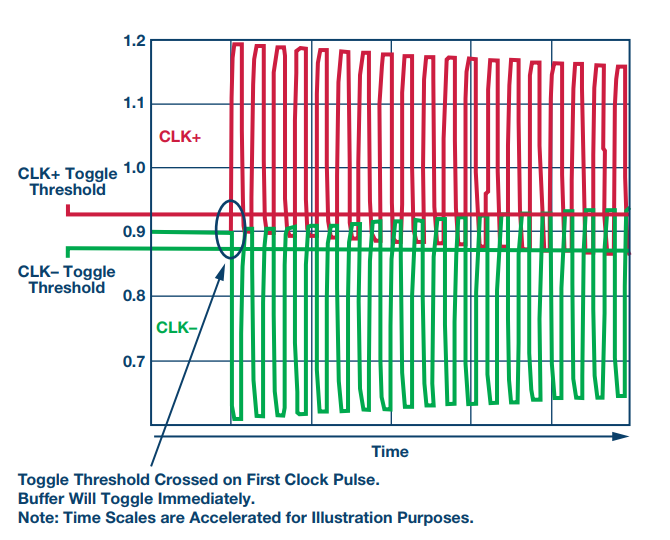

在没有应用时钟的情况下,CLK+ 和 CLK– 将分别被拉到相同的位置 VCM由时钟缓冲器中的内部偏置电路实现。当时钟 最初应用时,CLK+ 和 CLK– 上的时钟边沿将正摆动 和消极的,或消极的和积极的远离以前 建立了市调机制。在图1中,VCM = 0.9V。

图 1 显示了时钟处于非活动状态后应用的时钟(任一 首次启动系统时,或时钟驱动程序处于非活动状态后 一段时间)。在这种情况下,CLK+ 在第一个边缘上摆动为正 和 CLK– 摆动为负。在输入切换开关中添加正偏移 阈值,此时钟信号将在其第一个边沿切换时钟缓冲器,如 如图 1 所示。时钟输入缓冲器将立即产生时钟

图1.启动时,CLK+ 在第一个边缘摆动为正,CLK– 摆动为负。

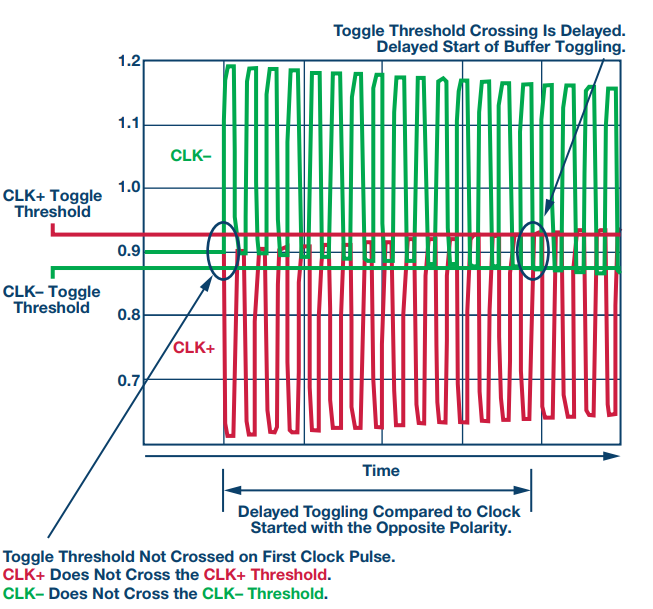

如果时钟以相反的极性开始,CLK—— 在第一个边缘摆动为正,CLK+ 摆动为负。随着 输入切换阈值增加相同的正偏移,此时钟信号 不会在其第一个边沿和后续边沿上切换时钟缓冲器 直到波形被拉到稳定状态,并穿过切换开关 随时间变化的阈值,如图 2 所示。

图2.启动时,CLK+ 在第一个边缘摆动为负,CLK– 摆动为正。

可以看出,初始启动时钟的极性会有所不同 在切换具有输入阈值偏移的时钟缓冲器时。在一种情况下(CLK+ 在本例中最初上升)时钟缓冲区理想情况下将开始切换 首次应用时钟时立即。极性相反 (CLK+在本例中最初落下),时钟缓冲区将不会启动 首次应用时钟时立即切换。

如果您发现 ADC 启动出现意外延迟,请尝试反转 时钟启动极性。这可能会改变您的启动时间。

审核编辑:郭婷

-

ADC时钟极性与启动时间2018-10-17 0

-

如何去启动ADC时钟2021-09-23 0

-

请问CPLD加载启动时间如何调整?2023-08-11 0

-

电机启动时间一般是多久?怎么缩短启动时间呢?2023-11-16 0

-

电机启动电流与启动时间的关系是什么?2023-12-12 0

-

电脑启动时间长的原因及处理方法2010-02-25 2615

-

Linux系统启动时间优化方案2011-05-13 2726

-

基于FPGA的PCIe设备如何才能满足PCIe设备的启动时间的要求?2018-06-19 7722

-

你知道ADC时钟极性与启动时间?2019-04-15 2614

-

嵌入式 Linux 启动时间优化2021-11-01 227

-

优化嵌入式Linux的启动时间之文件系统2021-11-02 356

-

电机星三角降压启动时间的计算方法2022-04-08 18164

-

星三角降压启动时间你知道怎么计算吗?2023-11-25 1533

-

开关电源启动性能检测之启动时间测试方法2024-01-22 363

-

i.MX 9系列-启动时间测量方法应用指南2024-02-20 56

全部0条评论

快来发表一下你的评论吧 !