LTC5589/LTC5599低功率IQ调制器的基带设计示例

描述

为了产生复杂的调制,需要两个相同的通道(I和Q)。为简单起见,此处仅显示一个通道。

调制参数

在此示例设计中,系统规格如下:

符号速率 = 30 ksps

数字滤波器 alpha= 0.35

下一步是确定基带滤波器要求:

总信号带宽 = 30*1.35= 40.5 kHz,即每个 I 和 Q 通道为 20.25 kHz。这决定了滤波器通带。

滤波器阻带要求主要由DAC更新速率决定,在本例中为240 ksps,或每个符号8倍插值。

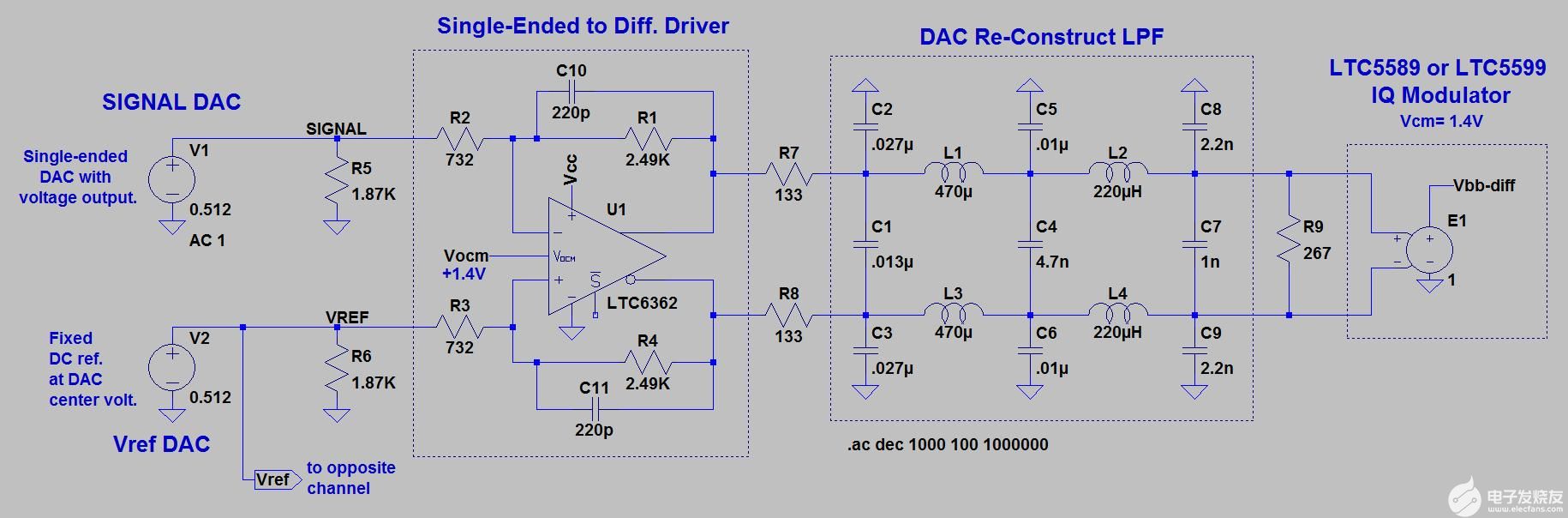

现在让我们快进到完整的电路,然后是描述。请注意,为简单起见,仅显示两个相同的I&Q通道之一:

图1.基带驱动电路将单端DAC转换为差分。建议使用无源DAC重构滤波器以实现低噪声。

DAC 输入和参考

首选差分DAC输出。但是,当使用单电源、单端DAC输出时,则需要固定的Vref,该Vref可能来自第3个DAC或V。裁判的信号 DAC。Vref只是DAC的零基准电压源,可以在I和Q通道之间共享,但要确保它是低源阻抗,以实现I和Q通道之间的最小串扰。缓冲液 V裁判必要时采用一个 LTC6246 电压跟随器。

在本例中,单端I和Q DAC配置为0至+1.024V输出。请注意,DAC数字驱动器应缩放以使用所有可用的DAC位,但切勿触及满量程极限。

可选电阻R5和R6用于DAC的低平均直流电流。在本例中,输入共模电压被下拉至0.512V,以匹配DAC输出电压范围的中心。

单端至差分驱动器

与单端基带驱动相反,使用差分基带信号驱动调制器是非常优选的。差分驱动提供高 6dB 的射频输出功率和最低的误差矢量幅度 (EVM)。

选择具有差分输入和输出的放大器还可以简化设计,因为

设计对称性降低了输出直流失调误差,从而减少了LO馈通(LOFT)并提高了调制精度。

输出共模电压(VOCM) 可以独立更改以满足调制器的要求,并且

增益可以独立改变,而不影响VOCM.

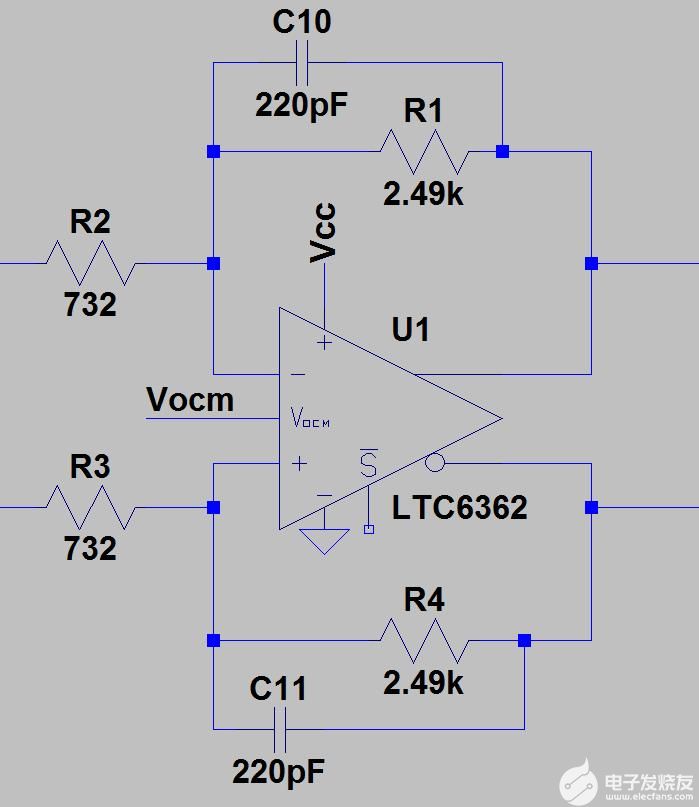

图2.差分驱动器通过提供增益和输出共模电压的独立调整来简化设计。

选择LTC6362用于此应用,是因为它仅吸收1mA的电源电流,而且噪声相当低。对于基带信号源具有低近端噪声密度的设计,低放大器噪声非常重要,这意味着使用非常高阶基带数字滤波器以及高分辨率DAC。我们不希望放大器使这种接近信噪比变得更糟。

选择电容C10和C11来降低HF噪声,同时在最高基带频率下提供可忽略不计(<0.1 dB)幅度误差贡献。LTspice仿真对于此目的非常有用。

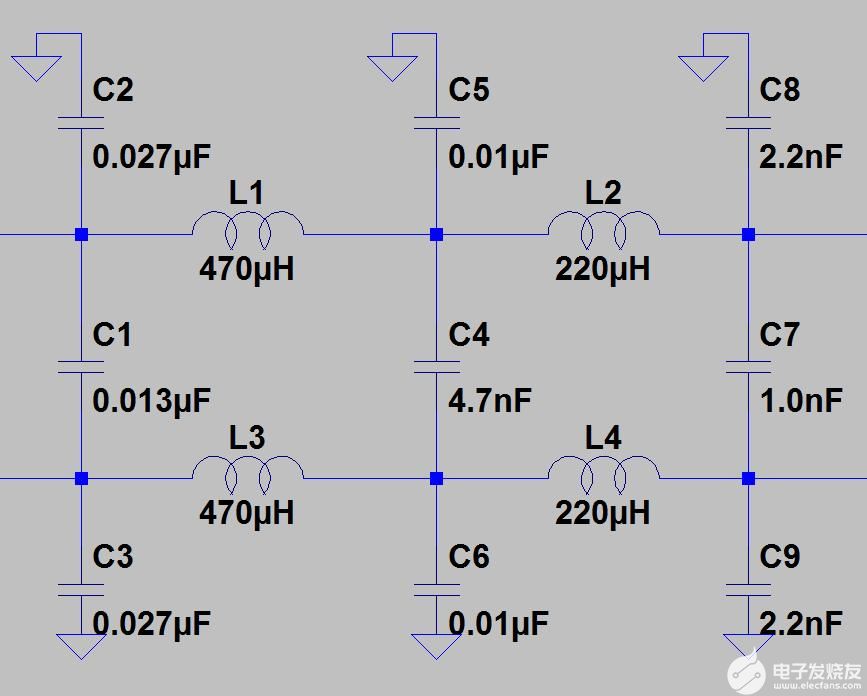

DAC LC 重构滤波器

DAC重建滤波器对于平滑DAC阶梯输出非常重要,它减少了高频奈奎斯特镜像。另一个重要功能是将调制器输出端的宽带本底噪声降至最低。

图3.LC重建滤波器。此设计适用于 266 欧姆源极和负载端接。

使用经典的滤波器设计CAD工具为您的设计合成这些LC元件值。为获得最佳调制精度,请选择贝塞尔LPF响应作为线性相位。在本例中,-3dB转折放置在50 kHz,这适用于高达~30 ksps的符号速率。

DAC镜像杂散相对于所需信号的幅度可以通过SIN(x)/x估计,其中x = π f / f时钟,对于此设计的频率计划,我们可以预期在220 kHz时具有25dB的图像衰减。再加上DAC LC重建滤波器在220 kHz(45dB)处提供的衰减,以估计70dB的总奈奎斯特镜像抑制。

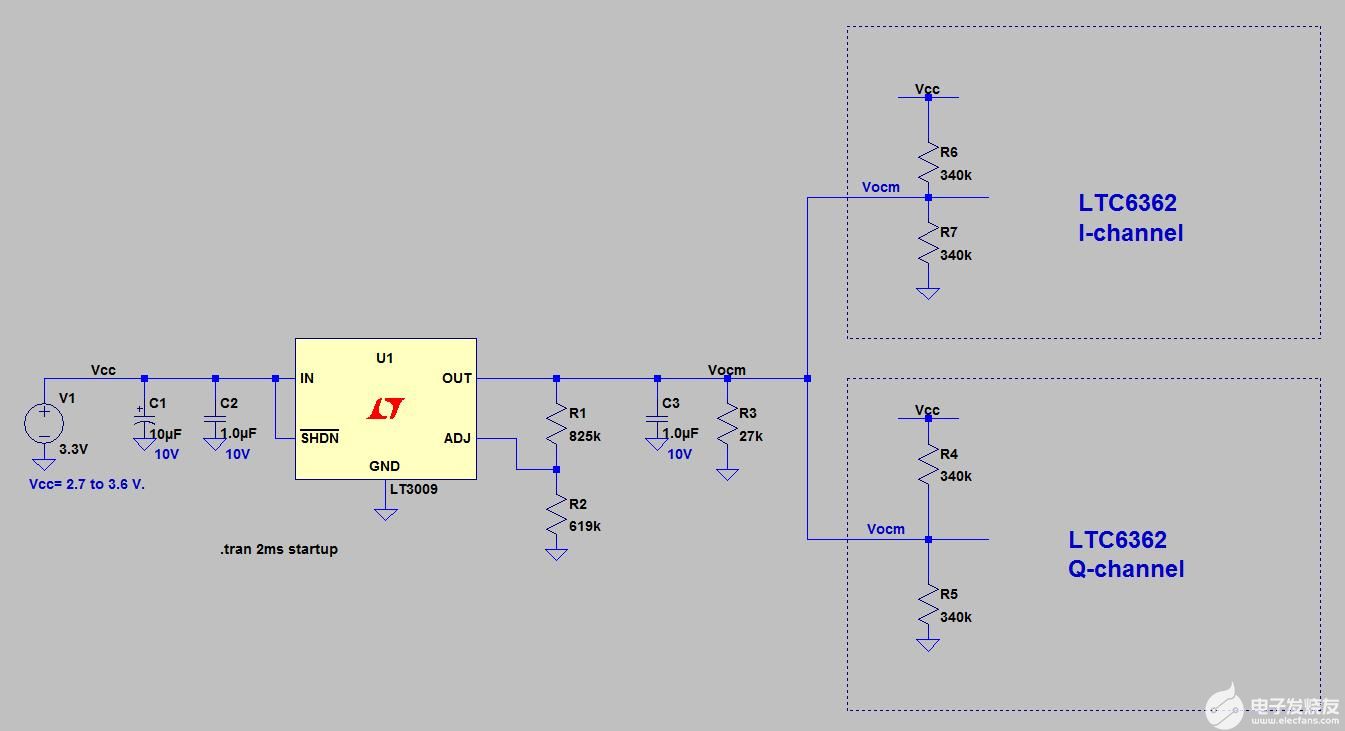

推导 VOCM源

当 V抄送监管良好,VOCM可以从简单的Vcc电阻分压器获得。否则,VOCM由一个可调电压稳压器高效衍生而来,该稳压器支持低至 1μA 的电阻分压器电流。 适当的 VOCM电压对于建立正确的IQ调制器工作点至关重要。

图4.简单的 LT3009 提供了调节良好的低噪声 Vocm,同时将电流浪费降至最低。

请注意,LTC6362 具有一个内部 VOCMV 时的分压器抄送/2,因此每当 Vcc 超过 2.8V 时,VOCM需要一些下拉才能保持在1.4V。这就是 R3 的目的。

增益缩放

通常,对于许多 LTC5589 和 LTC5599 应用,差分驱动电平约为 330mV有效值是一个很好的起点,在IQ调制器的I和Q输入端进行差分测量。由于LC滤波器损耗,LC滤波器输入端的驱动电压通常略高,约为358mV有效值在每个差分放大器输出端。应使用频谱分析仪来确认是否达到了所需的调制器RF输出频谱纯度。

以更高的V驱动IQ调制器有效值用于更高的输出功率或更低的 V有效值用于降低 IMD 和提高调制精度。放大器反馈电阻可以为此目的进行调整。

仿真结果

滤波器合成应该已经正确。然而,由于滤波器设计必须从单端转换为差分,因此存在一些设计误差的蔓延空间。另一个误差来源可能是放大器的延迟,这成为更高符号速率的一个因素。快速的LTspice仿真有助于验证这两个误差源是否保持良性。

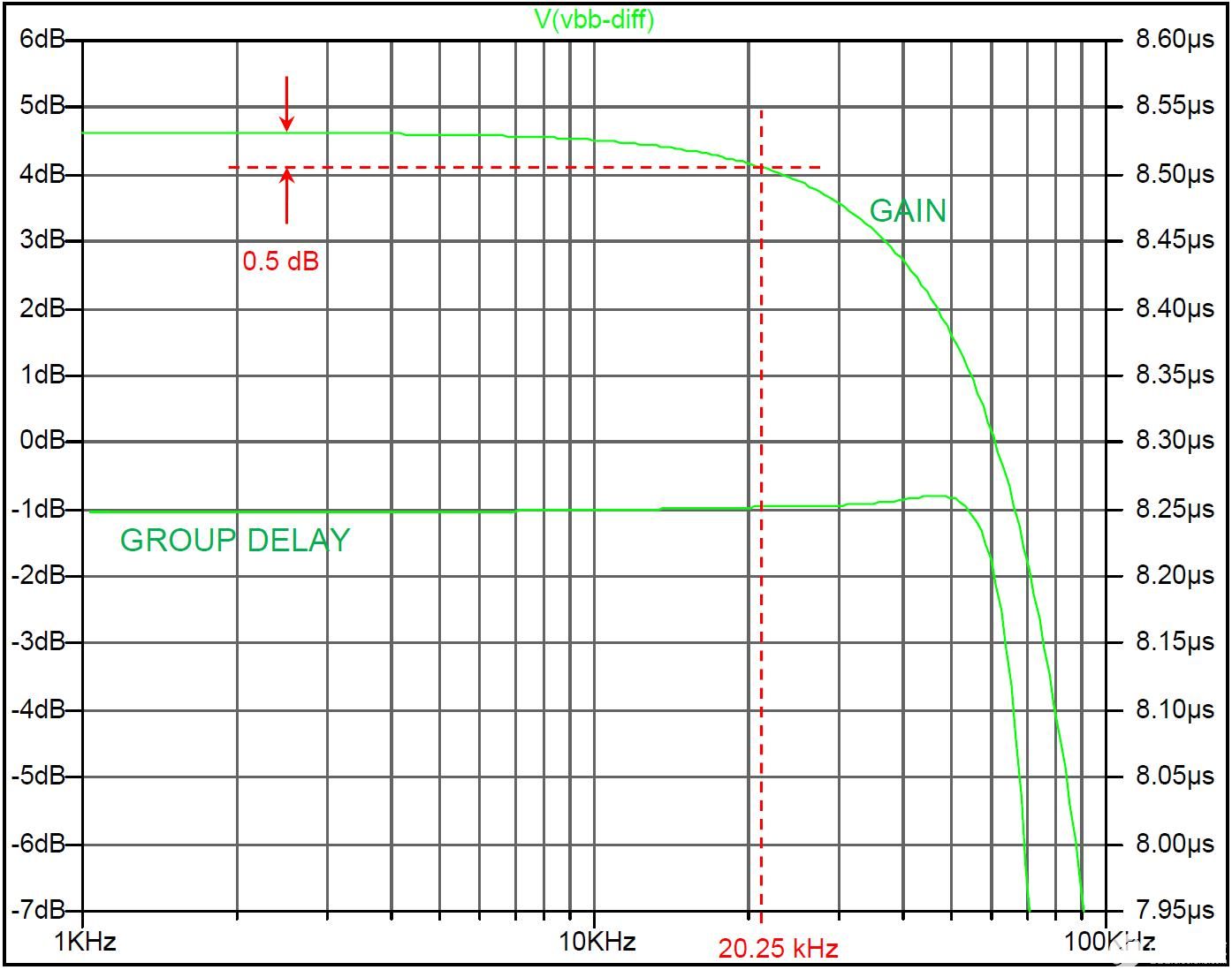

首先分别查看通带和阻带响应:

图5.整体电路通带响应。在这里,我们寻找最高信号频率(本设计示例中为20.25 kHz)下的最小增益滚降和群延迟变化。

请注意,在20.25 kHz的最高信号频率下,响应下降仅为0.5dB。低于1dB是一个很好的目标。群延迟非常平坦,您需要增量标记才能在上面的仿真图上测量它。它只有3.7ns,与1/30k或33.3us的符号周期相比,可以忽略不计。少于符号周期的百分之几是一个很好的目标。在这种情况下,群延迟变化非常好,这要归功于贝塞尔滤波器。

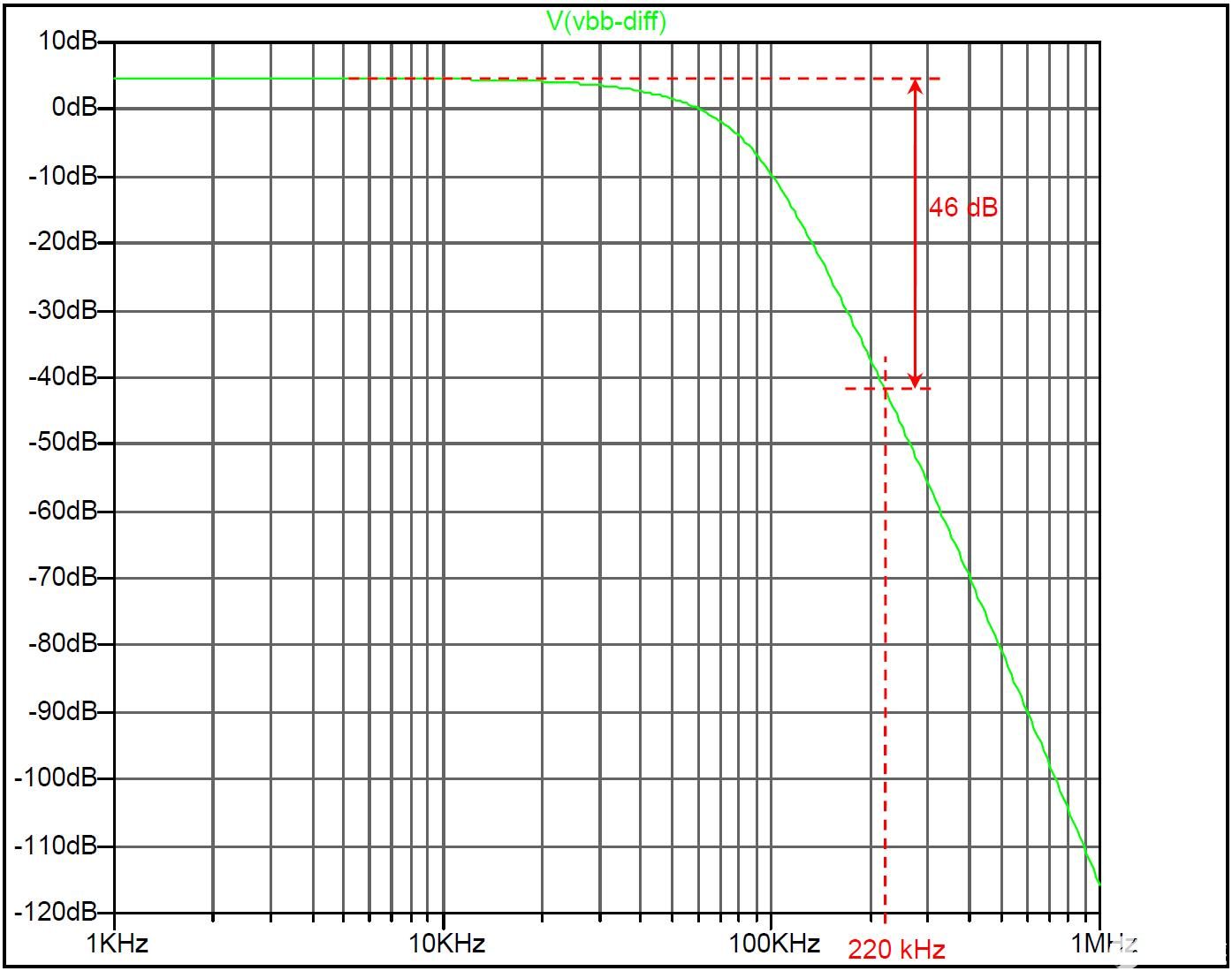

图6.整体电路阻带响应。在这里,我们正在寻找奈奎斯特图像频率(本设计示例中为220kHz)下的足够衰减。

在本例中,我们看到镜像频率处的衰减为46dB。结合 25dB sin(x) / x,即 71 dB。这里一个好的目标是大约 70dB 或更好。对于无线应用,监管机构的要求在这里发挥作用。

请注意,滤芯损耗可能不那么容易准确模拟。它们的效果将在下一个主题中很明显:

测试结果

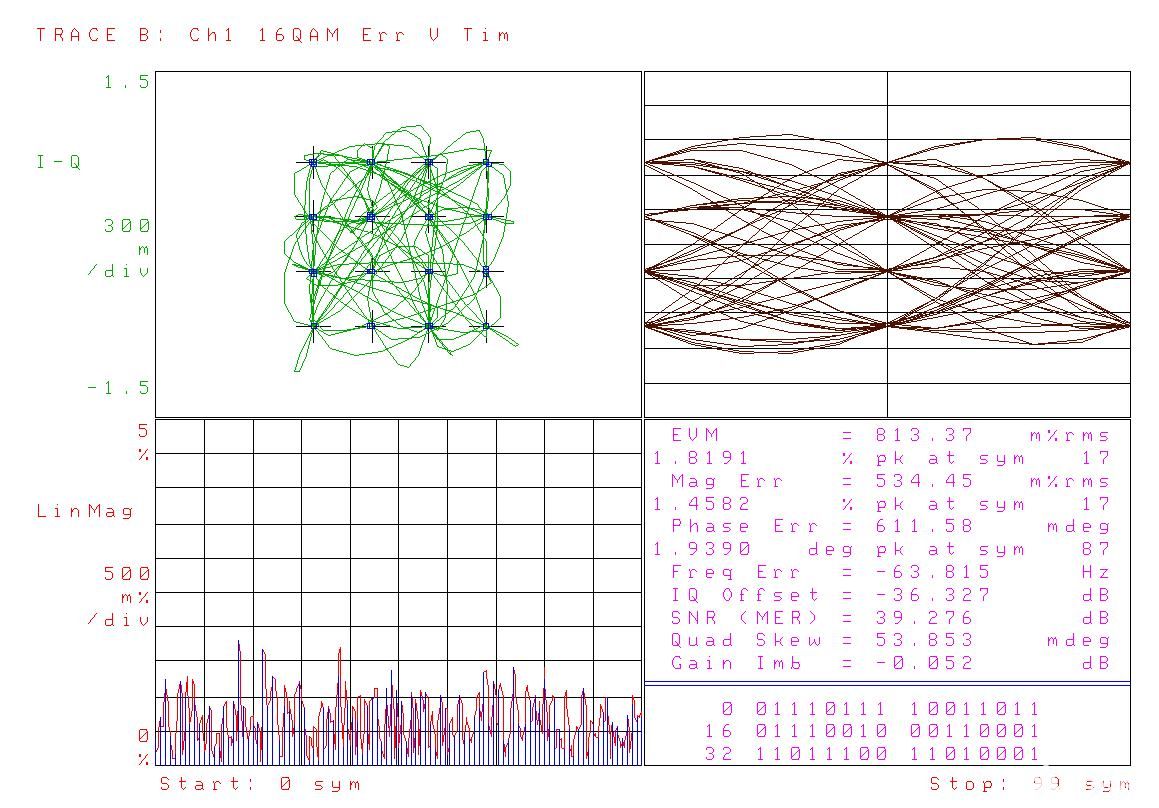

对于数字调制,调制器精度的最终测试是EVM。

图7.LTC5599 0.8% rms 的 EVM 测量值符合预期。除设置为450MHz的LO频率外,所有SPI寄存器均采用默认值。

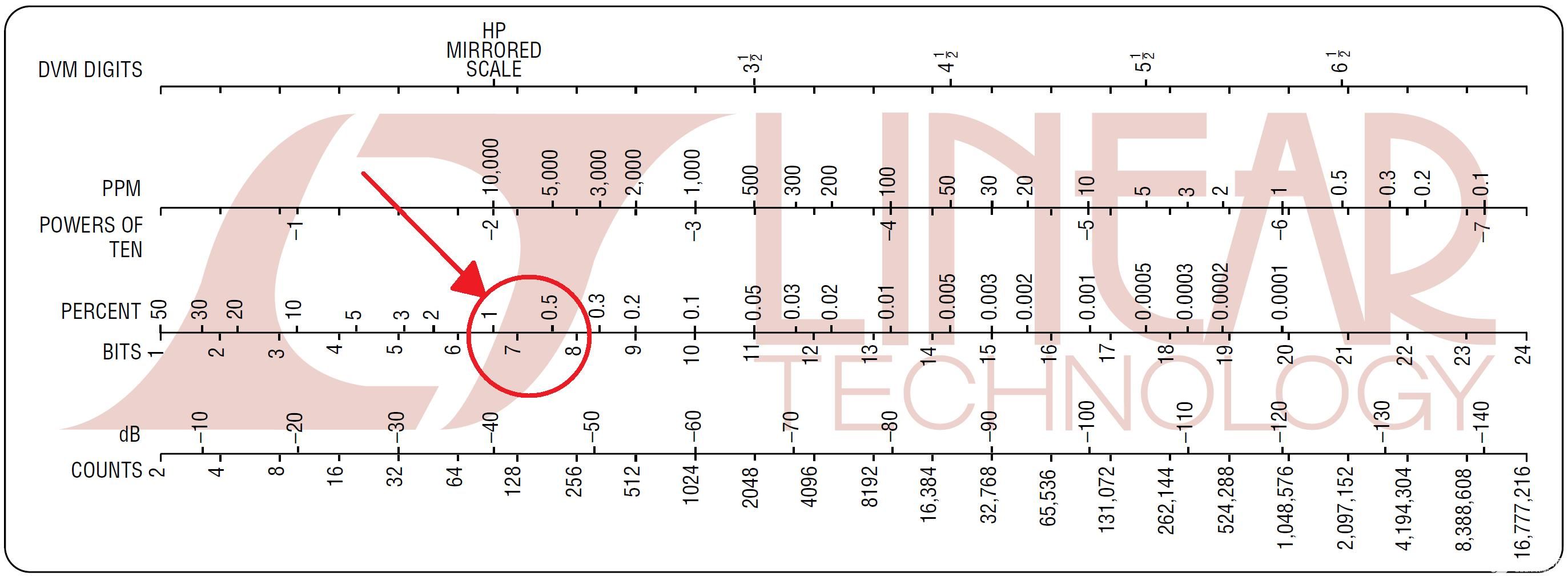

考虑到该系统使用的是 8 位 DAC,EVM 的测量值约为 0.8% 也就不足为奇了,因为考虑到 ENOB 将小于 8 位,从根本上说,这是可实现的最佳目标:

图8.索取免费的线性技术精度转换器!本例显示了有效的DAC分辨率如何限制调制精度。

EVM 测试结果与之前公布的测量结果一致,对于大多数数字调制应用来说绝对足够好。

进一步的EVM改进需要更多的FIR滤波器抽头,更高分辨率的DAC,也许还需要一些数字滤波器补偿,用于sin(x)/x滚降和DAC重建滤波器滚降。

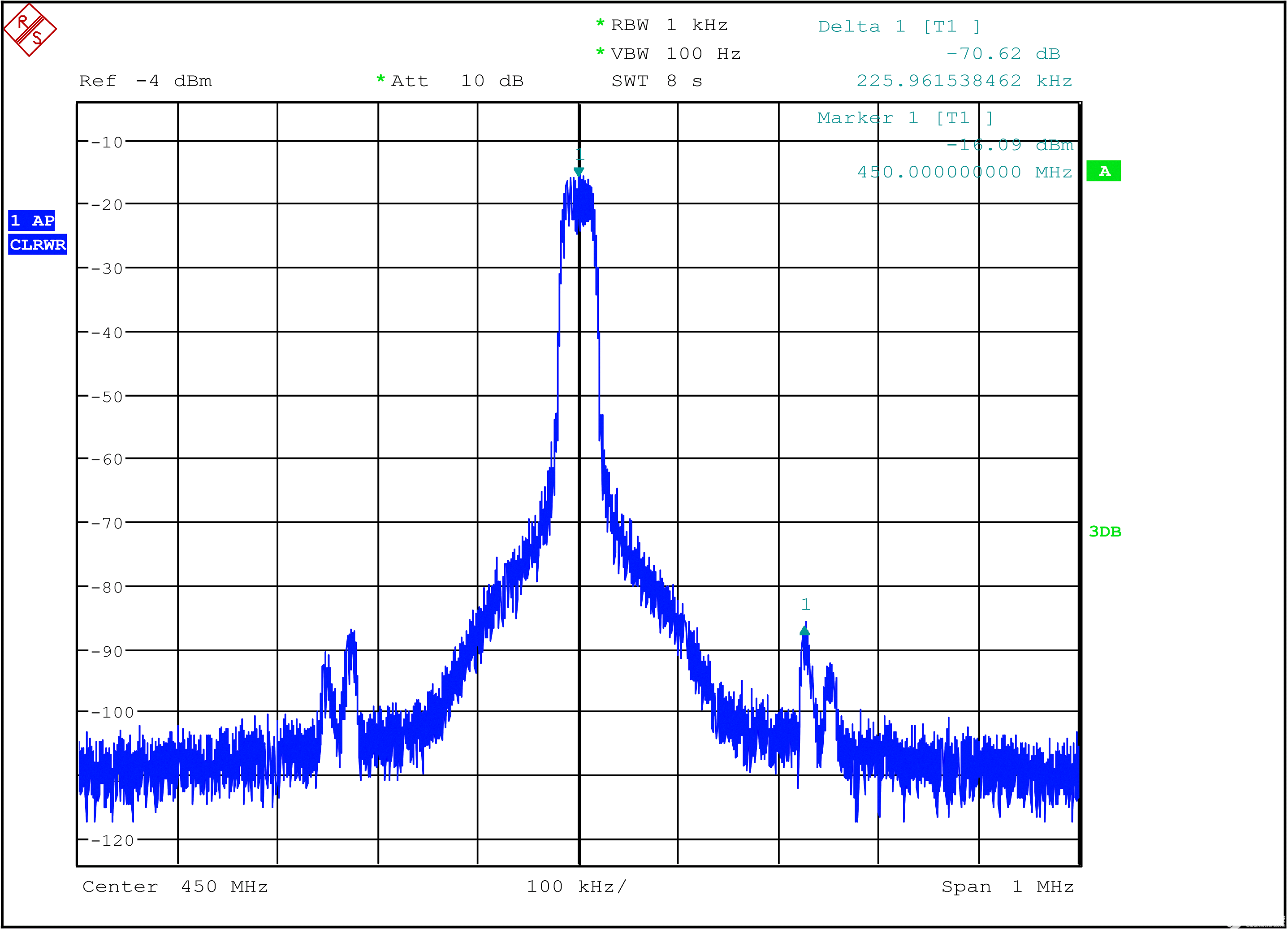

图9.-4dBm 输出功率时的射频输出频谱。请注意,最差的DAC镜像约为-70dBc,足以满足大多数应用的需求。

从输出频谱来看,近端噪声频谱密度由几个因素决定:FIR滤波器阶数、LO相位噪声和调制器驱动电平。

结论

本博客阐述了利用低功率 IQ 调制器(如 LTC5599 和 LTC5589)的详细设计技术。为实现最高调制精度、最低噪声和最低直流功耗,设计人员必须仔细考虑每个电路模块,如本文所示。

审核编辑:郭婷

-

LTC5599为什么不受程序控制?2024-01-05 0

-

30MHz至1300MHz低功耗直接正交调制器2020-06-18 0

-

直接转换IQ调制器LTC55881相关资料下载2021-04-19 0

-

一文详解IQ正交调制器基础知识2023-05-16 0

-

6GHz 低功率直接转换 I/Q 调制器2016-05-27 1312

-

LTC5599:具有边带抑制和载波泄漏抑制性能2018-06-28 4897

-

LTC5599 30MHz 至 1300MHz 低功率直接正交调制器2019-02-22 229

-

LTC5589 700MHz 至 6GHz 低功率直接正交调制器2019-02-22 255

-

了解一款非常低功率的高性能 I/Q 调制器2020-07-01 2343

-

LTC6362/LTC5599 Demo Circuit - Low-Power I/Q Modulator Driver (Baseband Design)2021-03-10 736

-

LTC5589:700 MHz至6 GHz低功耗直接正交调制器数据表2021-05-15 459

-

LTC5599:30 MHz至1300 MHz低功率直接正交调制器数据表2021-05-23 496

-

LTC6362LTC5599演示电路-低功耗IQ调制器驱动器(基带设计)2021-05-31 528

-

基于LTC5599_Typical Application调制器的参考设计2021-07-05 337

-

用于数字通信的低功耗IQ调制器2023-01-08 3122

全部0条评论

快来发表一下你的评论吧 !