使用DS26504抖动衰减器的设计考虑

描述

建筑集成定时电源(BITS)是网络同步中广泛使用的一种时钟。它是需要同步的网络内所有已部署设备的主定时电源。DS26504是BITS时钟恢复元件,可用于这些应用。该器件的接收器部分可以从 T1、E1、64kHz 复合时钟 (64KCC) 和 6312kHz 同步定时接口恢复时钟。

DS26504的一个重要模块是其抖动衰减器,它无需专用晶振即可工作,并使用MCLK工作。DS26504内置无晶振抖动衰减器,具有旁路模式,用于T1和E1工作。

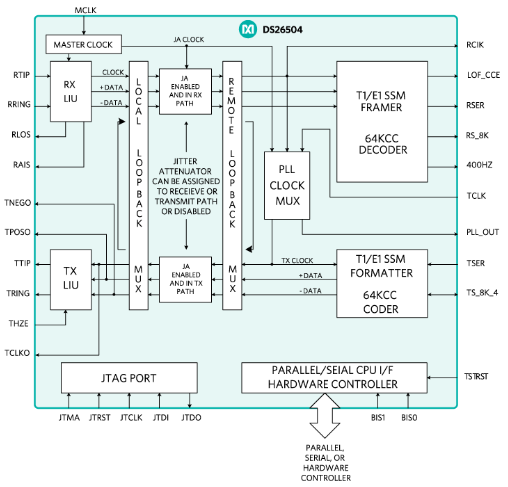

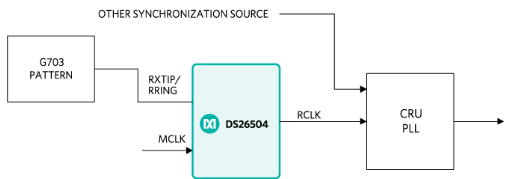

图1所示的抖动衰减器可以插入发射或接收路径。

图1.DS26504原理框图

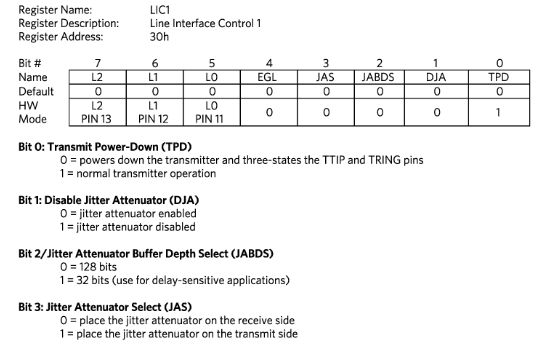

寄存器线路接口控制1(LIC1)(图2)允许客户选择抖动衰减器的位置(在Rx或Tx路径中),并打开或关闭抖动衰减器。此外,抖动衰减器可以通过JABDS位(LIC1.2)设置为32位或128位的深度。128 位模式用于预计会出现较大漂移偏移的应用程序。32 位模式用于延迟敏感型应用。

图2.寄存器线接口控制 1 说明。

请注意,图2中分层数字接口的物理和电气特性在G.703 ITU同步标准中定义。

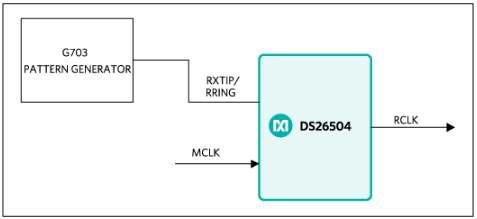

在本应用笔记中,如图3所示,DS26504输入信号表示为G.703,DS26504的主时钟表示为MCLK,从输入信号中恢复的时钟命名为RCLK。

图3.DS26504系统框图

抖动衰减器操作

DS26504内部的抖动衰减器采用恒定平均延迟架构。这意味着输入时钟和主时钟(MCLK)之间的频率差会导致抖动衰减器为输出时钟选择离散延迟。输出时钟延迟以 1 个 UI 步长发生,每 2ppm 的频率差就会发生。由于主时钟输入通常来自晶体振荡器(XO),因此主时钟频率随温度变化而变化。如果温度变化足够大,则频率差达到输出时钟 (RCLK) 偏移 1 UI 的点。

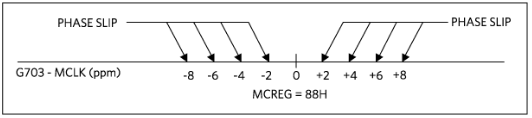

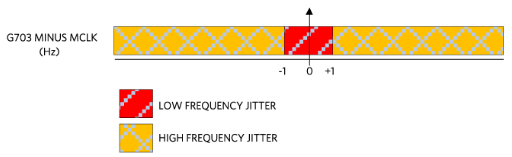

在这种情况下,如图4所示,恢复时钟(RCLK)每2ppm的频率差就会解锁并再次锁定,这可以称为“相位滑移”。如果主时钟频率稳定且输入信号的频率发生变化,则会出现相同的现象。

图4.G.703 和 MCLK 之间的频率差会在 RCLK 上产生相位滑移。

在诸如电信设备的定时单元等应用中,系统可以同步到输入的G.703信号,当发生相位滑移并在数据通信中引入错误时,BITS输入可能会被取消资格。

此外,如果在最大时间间隔误差 (MTIE) 和时间偏差 (t开发) 使用长达 20 分钟的观察时间的测量,测试失败。

因此,考虑到抖动清除可以从BITS之后的第二个PLL进行管理,建议在定时单元应用中保持抖动衰减器关闭,该PLL通常用于管理其他同步源(见图5)。

图5.DS26504在典型定时单元应用中的应用。

不使用抖动衰减器时,由于输入信号采样,恢复的信号会受到62.4ns范围内的高频抖动的影响(见图6)。

图6.当 G.703 和 MCLK 之间的频率差大于 1Hz 时,恢复时钟 (RCLK) 上的高频抖动。

如图7所示,G.703和MCLK之间的频率差异非常小,在1Hz(0.5ppm)范围内,会在RCLK上引入漂移(低频抖动)。

图7.抖动类型根据 G.703 和 MCLK 之间的频率差异而变化。

虽然高频抖动可以很容易地从后续PLL中消除,但其带宽不足以消除漂移。

在此拐角条件下,影响RCLK的漂移会在最大时间间隔误差(MTIE)和时间偏差(t开发) 测试。

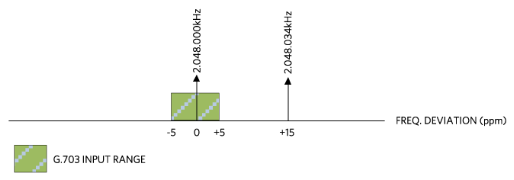

通过选择频率高于预期输入信号范围的信号作为主时钟(MCLK),可以避免这种情况。例如,如图8所示,假设输入信号为2.048MHz±5ppm,为了避免漂移,主时钟可以选择为2.048MHz + 15ppm。

图8.根据输入信号范围选择MCLK频率可以避免RCLK上的漂移。

通过这种安排,RCLK会受到高频抖动的影响,而高频抖动可以很容易地从PLL跟随位中消除。

结论

在定时单元应用中,建议保持抖动衰减器关闭,以避免上述相位滑移。

为避免漂移,在抖动衰减器关闭的情况下,G.703信号和主时钟(MCLK)之间的频率差必须大于1Hz。

审核编辑:郭婷

-

衰减器2017-10-11 0

-

衰减器的应用2017-11-07 0

-

光纤衰减器2017-11-09 0

-

固定衰减器2018-01-18 0

-

衰减器如何分类与选择2019-07-09 0

-

使用抖动衰减器常见设置测量状况的原因2021-03-08 0

-

DS26504 pdf datasheet(时钟恢复器件芯片2008-08-04 951

-

微波电调衰减器,微波电调衰减器是什么意思2010-03-05 801

-

光衰减器,光衰减器的工作原理是什么?2010-03-20 7004

-

光衰减器分类方式_光衰减器类型_光衰减器的原理2017-12-15 10224

-

衰减器分类_衰减器相关参数2019-08-08 5493

-

使用 DS26504 抖动衰减器的设计注意事项2022-11-16 36

-

射频衰减器受频率影响大吗 射频衰减器原理 射频衰减器的类型及作用2023-05-03 1287

全部0条评论

快来发表一下你的评论吧 !