FPGA ISP Bayer与常见颜色空间转换介绍

描述

前言

FPGA实现ISP(Image Signal Processor)过程中,在图像接收、处理、传输过程中往往会接触到各种各样的图像格式,比如接收图像可能是原始RAW数据,驱动LCD显示器需要RGB格式,HDMI/SDI显示需要YUV格式等。各种图像格式之间可能涉及到相互转换,本文简单介绍几种常见的图像格式以及Xilinx FPGA实现方式。

Bayer图像

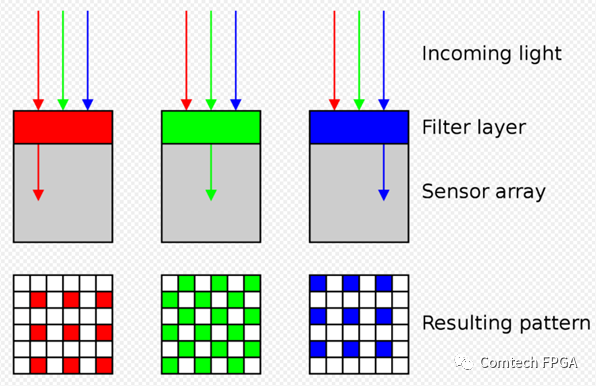

ISP通常是从接收到CMOS/CCD的图像信号开始,对于彩色图像传感器,输出图像格式可能是RGB、YUV或Bayer。为了降低成本,绝大部分的彩色图像传感器采用彩色滤镜阵列(color filter array,CFA)的方式捕获彩色图像,因此输出Bayer格式的Sensor最为常见。 典型Bayer图像的成像过程如下图所示。

图2-1 CFA示意图(图片来自wikipedia)

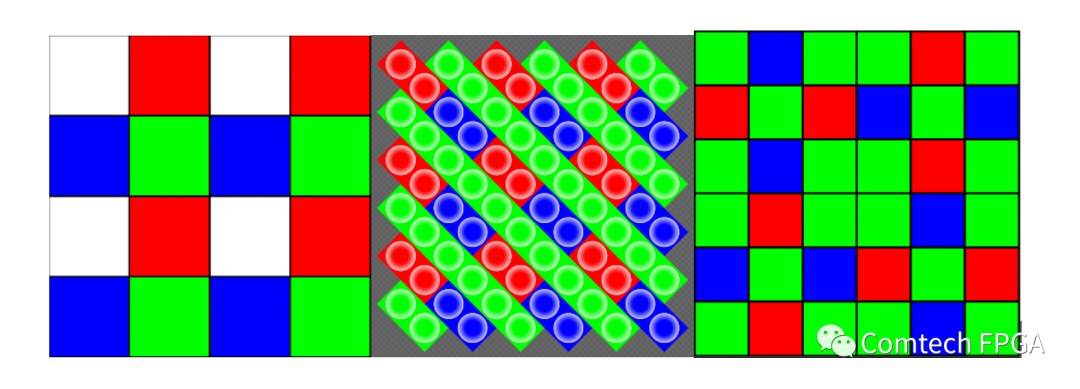

随着技术的发展,也有一些其他滤镜的Sensor出现,如RGBW、EXR、X-Trans等,如下图所示。

图2-2 RGBW、Fujifilm “EXR”、“X-Trans”示意图(图片来自wikipedia)

通过上图可以发现,这些滤镜中,绿色的分量最多。这是因为人眼对绿色最为敏感,所以保留最多的绿色分量。

Demosaic

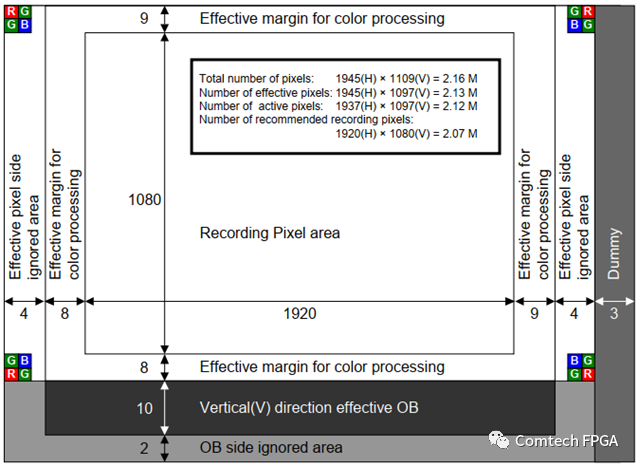

Bayer图像采集到FPGA以后,每个像素只有一种颜色分量。以Sony IMX290为例,输出图像的bayer格式如下图所示:

图3-1 SonyIMX290 Pixel Arrangement

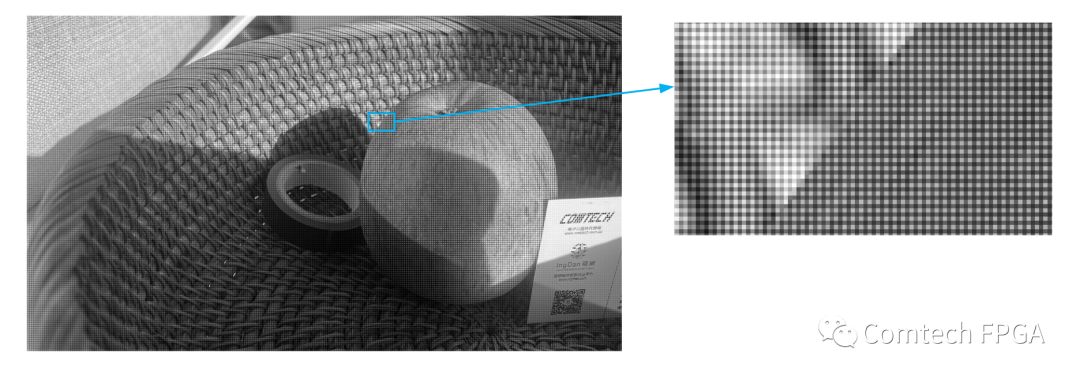

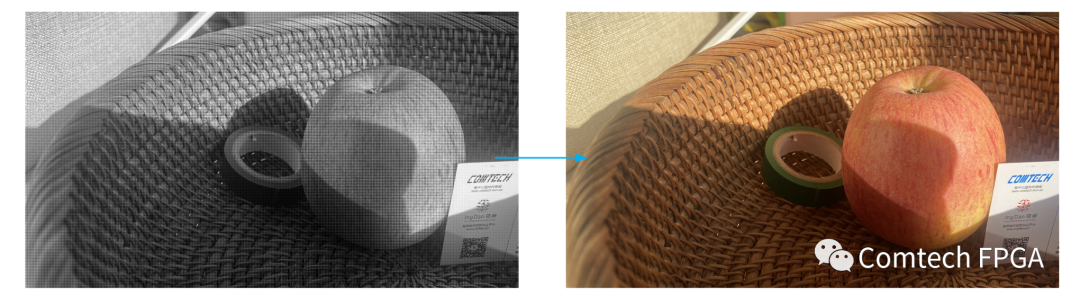

此时,如果将采集到的1920x1080图像以灰度展示,由于CFA的原因,图像会呈现一种马赛克现象,如下图所示:

图3-2 Bayerimage

所以将Bayer转成RGB的过程又称为Demosaic(去马赛克)。 每一个像素仅包含光谱的一部分,需要通过插值来填充每个像素的RGB分值。为了从Bayer格式得到每个像素的RGB格式,需要通过插值对每个像素填补缺失的两个颜色分量。插值的方法有很多(包括近邻、双线性等)。 插值后可以得到RGB图像:

图3-3 Bayerto RGB

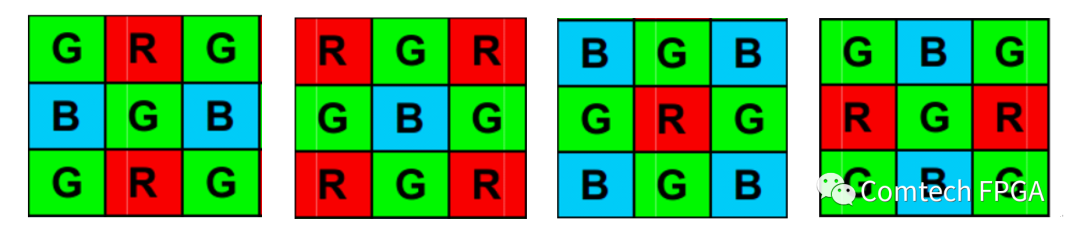

需要注意的是,Bayer图像根据第一个像素的颜色分量有4种排列方式,分别为GRBG、RGGB、BGGR、GBRG:

图2-4 Bayer4种排列方式

如果输入Bayer的排列与IP core配置中插值的排列方式不同,则图像颜色会错乱。

图3-5 Bayer排列方式与Demosaic配置不一致

RGB/YUV颜色空间转换

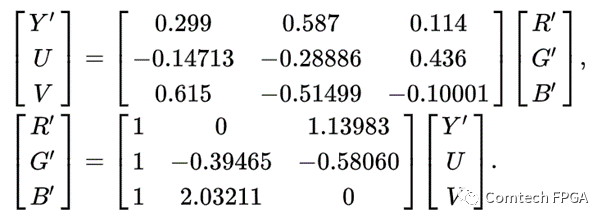

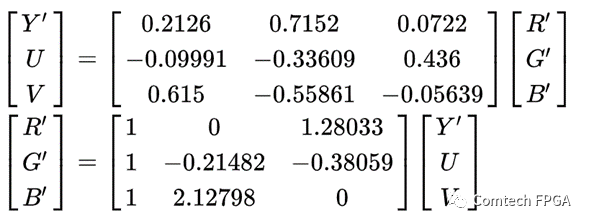

YUV是一种颜色模型。它对彩色图像或视频进行编码时考虑到了人类的感知,与 "直接 "的RGB表示相比,允许减少色度成分的带宽。YUV模型定义了一个亮度分量(Y),代表物理线性空间的亮度,以及两个色度分量,分别称为U和V。它可以用来与RGB或其他色域空间进行相互转换。 同样常见的还有YCbCr,但是在实际中,往往是把YUV和YCbCr认为是同一种色域,只有模拟和数字的区别。我们一般也统称为YUV。

由于YUV色域相比于RGB带宽更低,所以经常见于图像接口,如BT656、BT1120、HDMI等。也由于YUV亮度与色度分开的特性,许多图像增强算法也基于YUV来设计,如3D降噪、边沿增强等。 YUV于RGB颜色空间的转换可由公式表现,不同的标准如ITU601.SDTV、ITU709.PAL/NTSC参数略有不同。

图4-1 BT.601标准

图4-2 BT.709标准

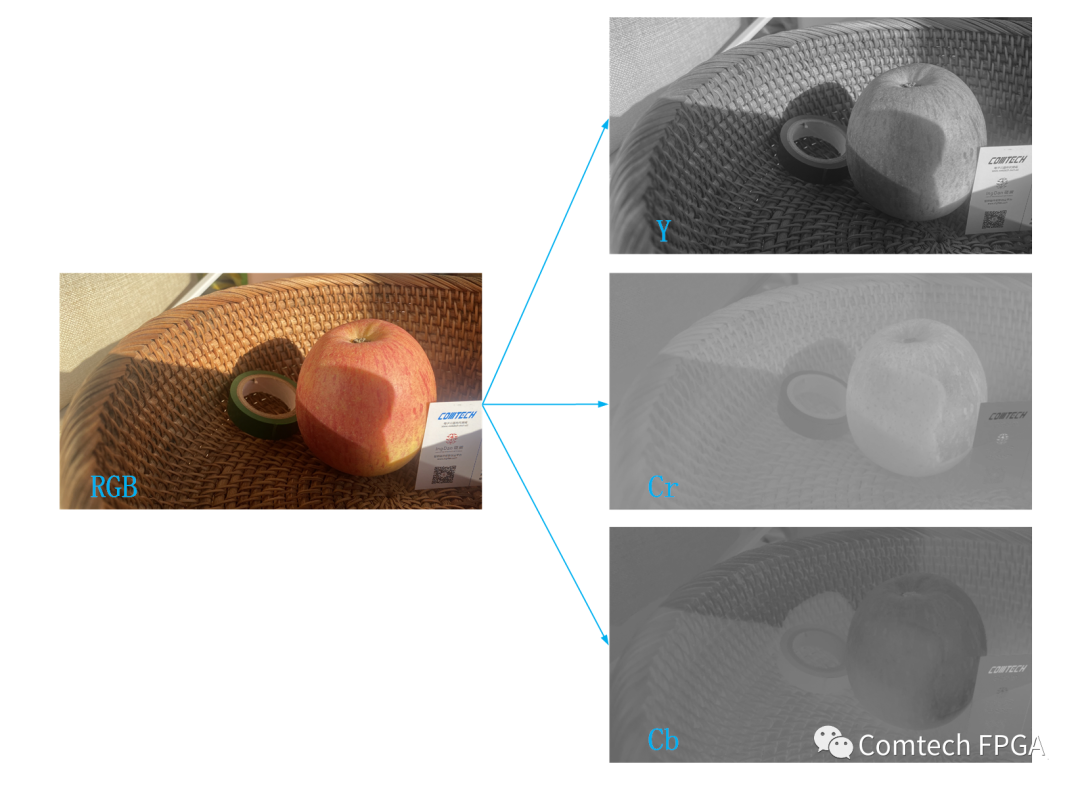

根据以上公式,可以由RGB图像得到YUV,此时YUV有三个通道,图像大小相比于RGB没有变化,我们通常称之为YUV444。

图4-3 RGBto YUV444

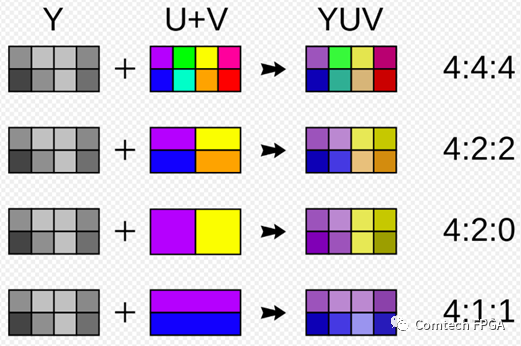

由于人眼对亮度敏感而对色度不敏感的特点,因此在YUV格式中减少了UV的数据量,在不影响用户观看的情况下有效的压缩了总体的数据量。所以YUV与RGB格式相比,占用更少的存储空间,相对应的在传输过程中也会减少带宽的消耗量。常见的YUV格式有YUV444、YUV422、YUV420等。

图4-4 Chromasubsampling示意图(图片来自wikipedia)

延伸

在RGB转YUV的过程中,我们通常可以加一个系数,作为比例因子放大和缩小UV的分量,达到调节图像饱和度的目的。以8bit图像深度为例,比例因子为r,公式如下:

Cb=U*r+128;

Cr= V*r+128;

调整比例因子r,能得到不同色彩饱和度的图像。

图5-1 饱和度设置效果

RGB/YUV的颜色空间转换并非完全无损。FPGA运算精度有限,多次转换可能导致颜色失真,尤其是当转入转出标准不同时,会引入累积误差。 比如网络上流传的有趣的表情包、梗图,在传来传去的过程中,网络平台可能会反复压缩、解压,而显示基于RGB,压缩基于YUV,所以对图片不断地进行RGB/YUV转换。虽然每次转换损失轻微,但久而久之,在不断取整的过程中,Y、U、V三个值就会不断减小,Y让图像越来越暗,UV让图像越来越向绿偏移。

图5-2 模拟“电子包浆”

AMD-Xilinx FPGA实现

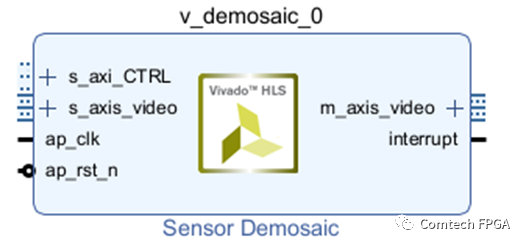

对于Demosaic,Xilinx提供IPcore供用户调用,用户可根据应用场景以及资源开销选择对应的插值方式,Fringe Tolerant Interpolation或者HighResolution Interpolation,支持RGB bayer和CMY bayer两种格式。详细说明参考Xilinx官网PG286。 IP接口如下图所示:

图6-1 XilinxDemosaic IP core

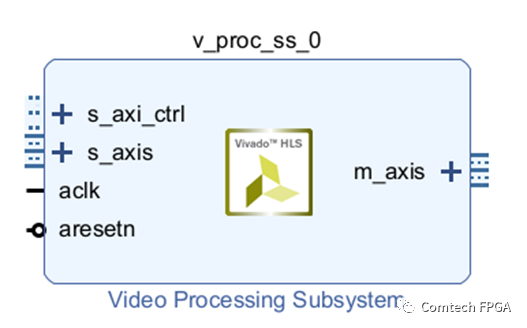

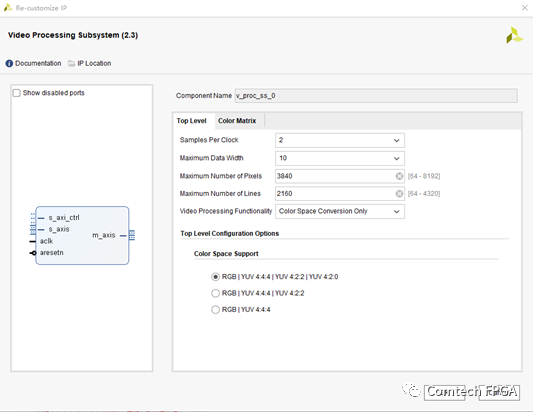

对于RGB与YUV的颜色空间转换或YUV444/YUV422/YUV420之间的转换,Xilinx也提供了IP core供用户调用。详细说明参考Xilinx官网PG231。

IP接口以及配置方式如下图所示:

图6-2 XilinxVPSS IP core

Xilinx提供的VPSS(Video Processing Subsystem),可以很方便地对RGB、YUV444、YUV422、YUV420进行互转。RGB与YUV的互转公式如下:

YUV to RGB:

B = Y + ((Cb * 2081)>> 10)

Cr = V -(1<<(HSC_BITS_PER_COMPONENT-1))

Cb = U -(1<<(HSC_BITS_PER_COMPONENT-1))

R = Y + ((Cr *1733) >> 10)

G = Y - ((Cb * 404+ Cr * 595) >> 10)

RGB to YUV:

V =(1<<(HSC_BITS_PER_COMPONENT-1)) + (((R-Y)*898)>>10)

Y = (306*R + 601*G+ 117*B)>>10

U =(1<<(HSC_BITS_PER_COMPONENT-1)) + (((B-Y)*504)>>10)

其中HSC_BITS_PER_COMPONENT = C_MAX_DATA_WIDTH (这里C_MAX_DATA_WIDTH可以由用户通过GUI设置。)

综上,使用这两个IP即可基于Xilinx FPGA快速实现Bayer与常见颜色空间转换。

审核编辑:刘清

-

基于CPLD/FPGA视频颜色空间转换电路的设计2013-05-02 0

-

ISP处理流程及应用场景2018-09-25 0

-

基于FPGA的rgb与yuv颜色空间转换2019-03-03 0

-

YCbCr色彩空间和RGB色彩空间之间的转换方法介绍2019-07-01 0

-

基于FPGA视频处理系统的颜色空间转换2010-07-28 394

-

常见的颜色模式HSB/RGB/CMYK详细介绍2010-02-23 5303

-

基于FPGA的Bayer到RGB图像格式转换设计2016-08-29 749

-

图像处理的颜色空间及其OpenCV实现2020-12-25 1481

-

图像的颜色空间及其OpenCV实现2020-12-26 1797

-

如何使用FPGA实现Bayer到RGB图像格式转换的设计2021-01-25 910

-

基于彩色MT9V034摄像头 Bayer转RGB FPGA实现2021-06-12 3117

-

颜色空间有哪些类别 如何在OpenCV中实现2023-02-07 547

-

图像Bayer格式介绍及差值原理2023-05-29 4836

-

IP库新增多种颜色转换空间IP简介2023-07-17 1110

-

基于FPGA的Bayer彩色自动白平衡设计2023-10-08 107

全部0条评论

快来发表一下你的评论吧 !