一文详解衬底偏压技术

描述

随着集成电路工艺尺寸的不断降低,静态功耗在总功耗中所占的比例越来越大,甚至是主要位置(65nm工艺下,某些情况下静态功耗占总功耗的50%)。 在实际的电路中存在着各种寄生效应,产生各种漏电流,带来静态功耗。

随着低功耗技术的不断发展,可以采用晶体管堆栈、电源门控、多阈值CMOS、电源电压缩放以及衬底偏压调节等技术来减少电路的漏电功耗。

一、衬底偏压技术

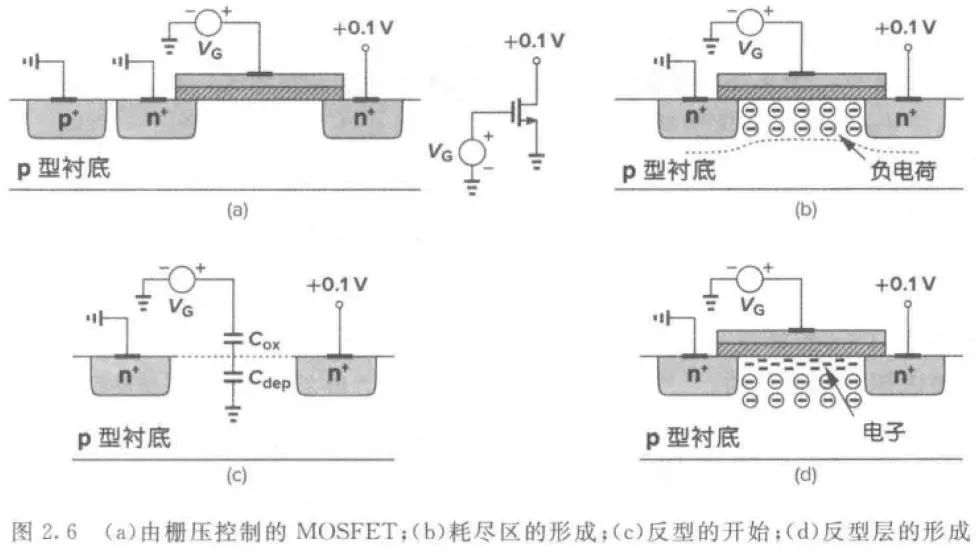

先简单回顾下MOSFET的导通过程。

当Vg从0V开始上升的时候,p衬底中的多子空穴会被赶离栅区从而留下负电荷(空穴无法移动,实际上是电子的移动,电子从衬底被抽取上来,与p型半导体中的受主杂质例如硼结合,使得共价键饱和,既没有可移动的电子,也没有可移动的空穴); 此时栅极与衬底构成电容器的两极,因此衬底上负电荷的量和栅上正电荷的量相同; 由于p型半导体中是多子空穴导电,最终在p型衬底中形成一个多子耗尽的区域即耗尽层;

随着Vg增加,耗尽层宽度以及,氧化物和硅界面处的电势也增加; 这时结构类似两个电容串联:栅氧化层电容(Cox,这是一个固定电容,Cox = εox/dox)和耗尽层电容(Cdep,这是一个可变电容,Cdep = εdep/ddep,ddep耗尽层宽度会增加);

当Vg进一步增加的时候,源漏之间的栅氧下就形成了载流子沟道; 形成沟道所对应的Vg成为阈值电压Vth;

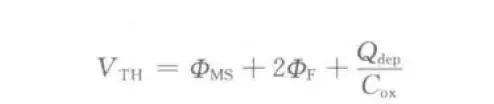

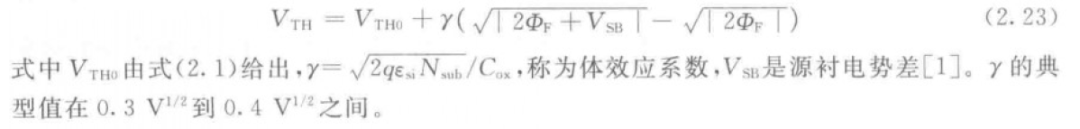

Vth通常定义为界面的电子浓度等于p型衬底的多子浓度时的栅压; Vth有如下表达式:

其中Qdep是耗尽层的电荷;

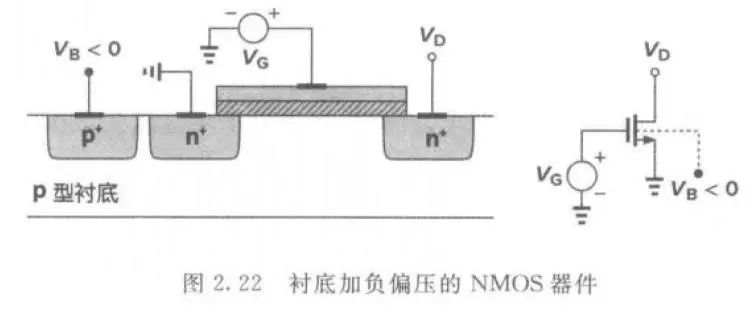

以上讨论都是假设衬底和源端是接地的,如果NMOS的衬底电压Vb比源端电压Vg小的时候会发生什么情况。

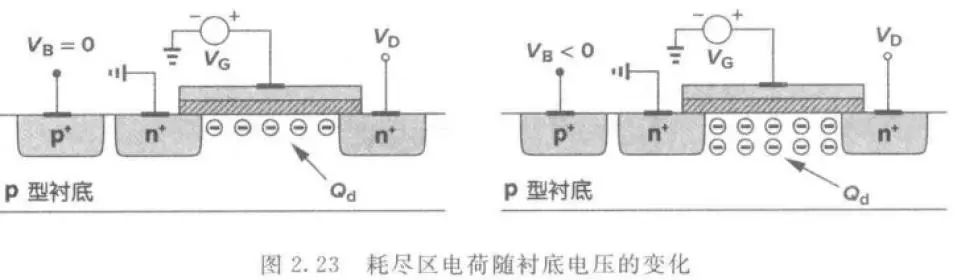

假设Vs=Vd=0,Vg略小于Vth使得栅下形成耗尽层但是还没有反型层形成。 当Vb变得更负的时候,将会有更多的空穴被吸引到衬底,同时留下大量的负电荷,耗尽层变得更宽了,由Vth的表达式可知,阈值电压是耗尽层电荷总数的函数,因为在反型之前,栅上的电荷是等于耗尽层电荷的。

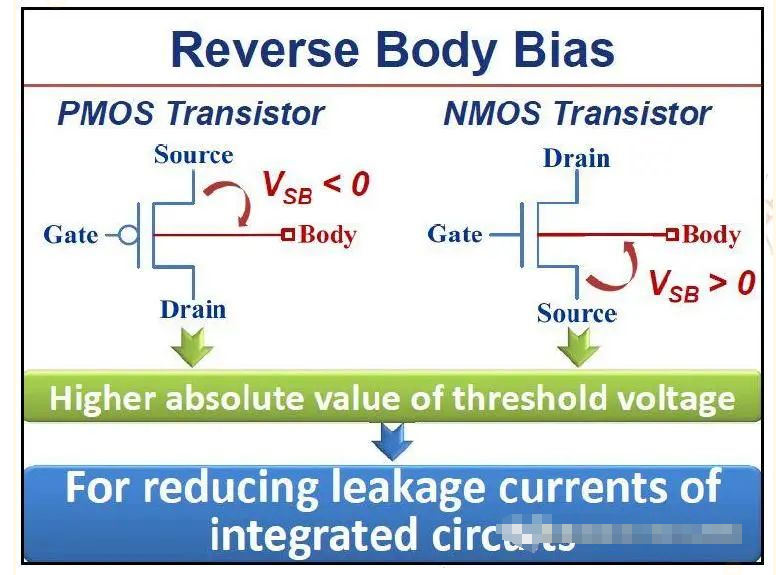

因此,随着Vb的下降,Qd增加,Vth也增加。 这称为反向衬底偏置或者体效应,可以表达为如下公式:

而阈值电压的增大,可以降低晶体管的漏电流,这种低功耗技术就称为反向衬底偏置技术。

上述讨论同时适用于PMOS,区别在于,对于PMOS来说,衬底加正偏压,Vsb < 0时阈值电压会增大。

二、衬底偏压的版图实现

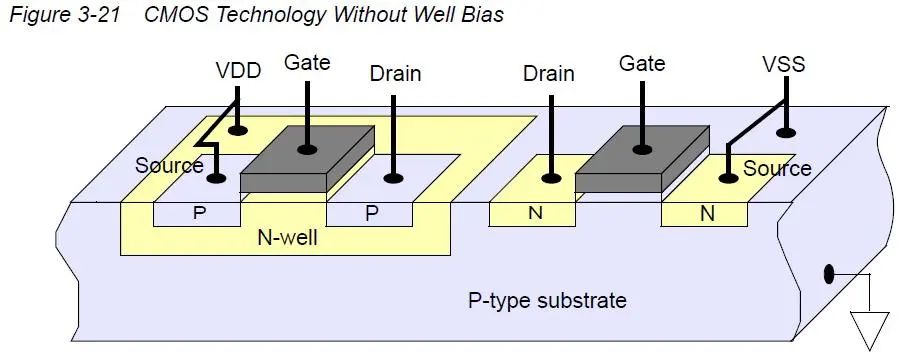

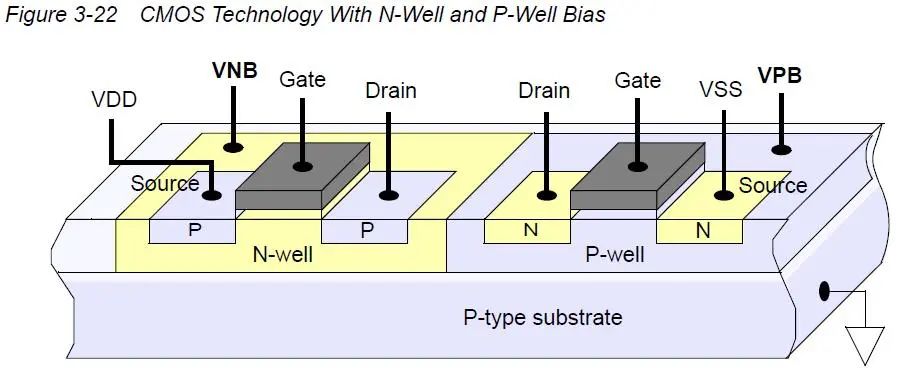

对于单阱工艺(Nwell)而言,所有NMOS的衬底都是接在一起的,因此我们无法给不同器件的P衬底分别供电。 但是对于PMOS而言,它们的Nwell其实是可以提供不同于VDD的电位的(有的标准单元库是可以给Nwell单独供电的),另外标准单元的Nwell并不是连续的,而是一排一排的。

无法实现衬底偏置

提供衬底连接的pin,VBN和VBP

三、自适应衬底偏压调节技术

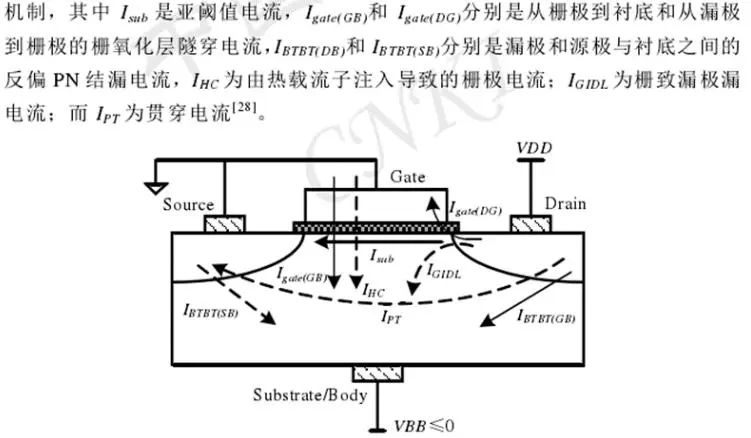

晶体管的漏电流有多种组成,如下图所示:

而各种漏电流随衬底偏置电压的变化趋势也并不相同,单调的施加衬底偏置电压并不一定会减小总体的静态功耗。

有研究表明,当处于关断状态的晶体管所产生的亚阈值电流等于带到带遂穿电流时,器件的总体漏电流达到最小值,此时所对应的衬底偏压值就是最佳值。

因此,可以设计出一个电路,该电路能够自动将衬底偏置电压调整至当前条件下(不同温度、电压、工艺)的最佳值。 这个电路一般被称之为Body Bias Generator。

关于衬底偏压技术在设计中的实现,有很多地方需要特别关注。

四、衬底偏压对亚阈值电流的影响

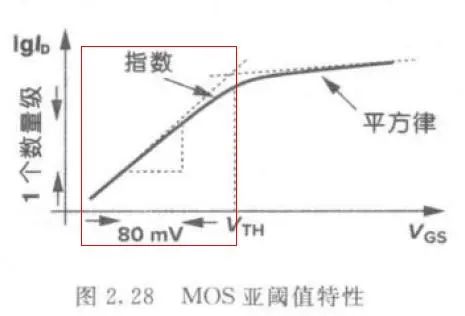

此前我们一直假设当Vgs下降到低于Vth时,MOSFET就会突然关断,实际上当Vgs小于Vth时,一个微弱的反型层是存在的,并且存在一些源漏电流,这种现象被称作亚阈值导电。

MOS的亚阈值特性如下图,当Vgs小于Vth时,漏电流Id并不为0,那么在包含数百万门的大规模集成电路中,亚阈值电流就会带来显著的功耗。 因此设计电路的时候必须考虑这个因素,阈值电压必须在合理的范围内,以确保栅压零偏的时候亚阈值电流不至于过大。

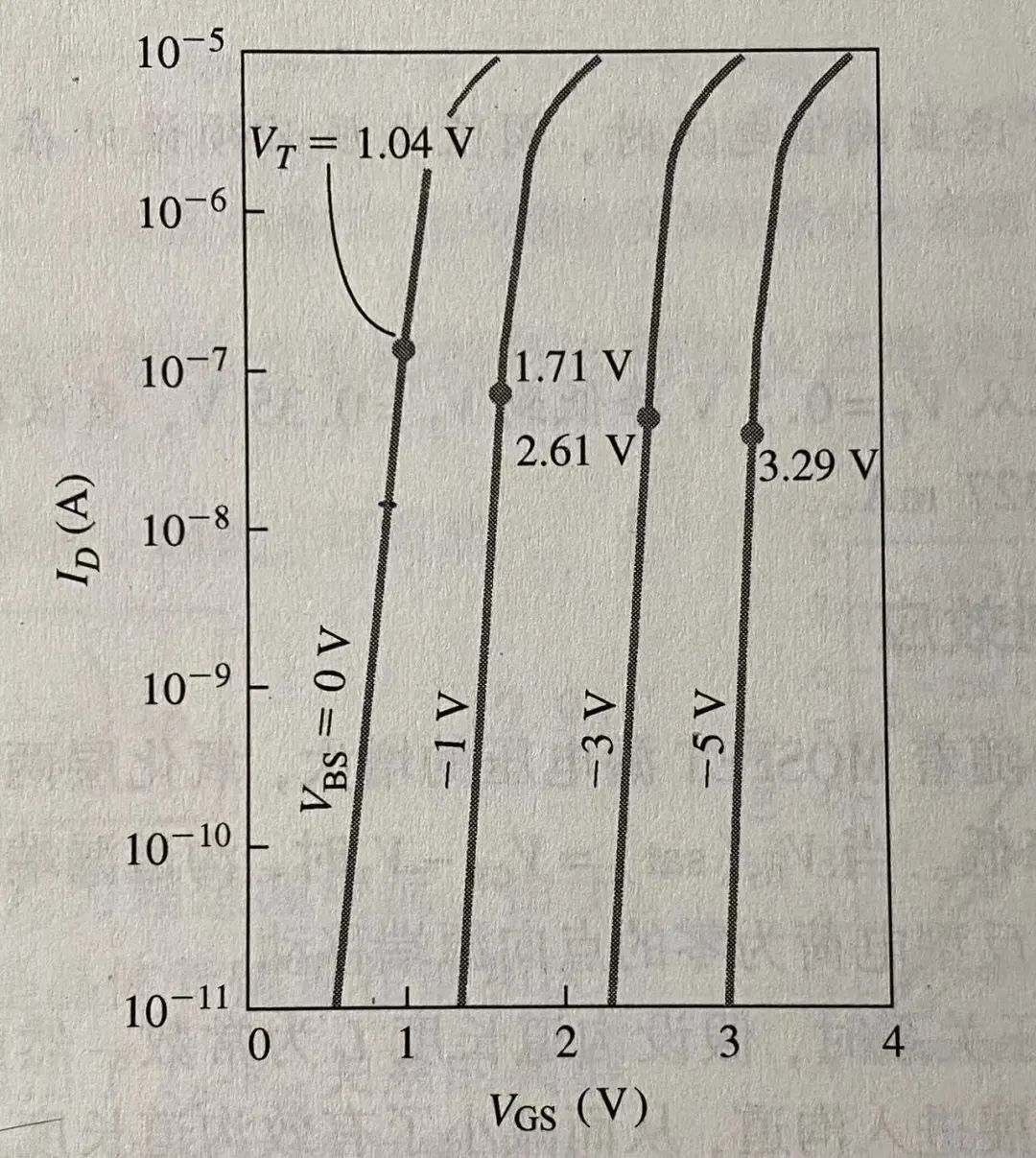

下图给出来NMOS施加不同的体源电压时,亚阈值电流的特性; Vgs一定时,当衬底反偏,即Vb小于0,Vbs < 0的时候,Id呈指数级下降。

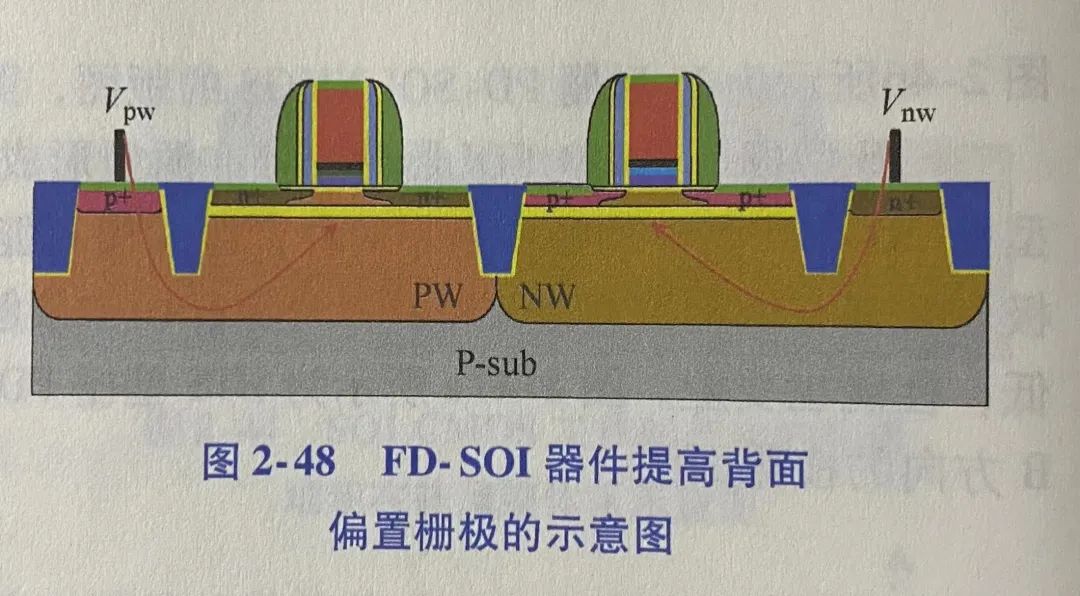

五、FD-SOI与衬底偏置

FD-SOI,Fully Depleted Silicon OnIsulation,全耗尽绝缘体上硅器件,主要应用在汽车电子、军事和航空航天等领域。

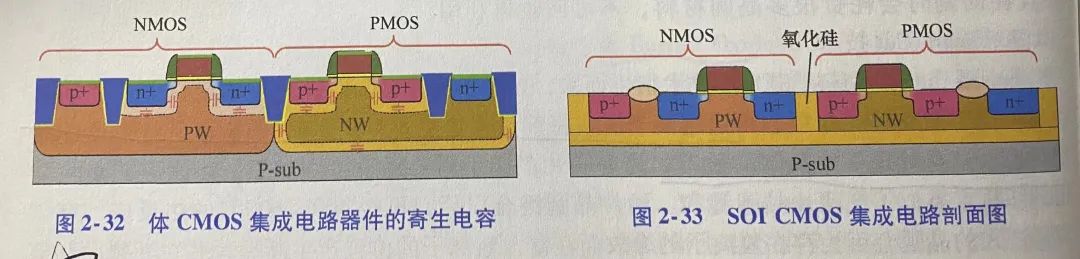

SOI器件中,氧化层埋层隔离了衬底和顶层硅薄膜层,器件就做在顶层的硅薄层中。

在体CMOS中,各种寄生电容非常多; 而在SOICMOS中,器件依靠氧化物隔离,隔离效果更好; 并且由于阱之间是不接触的,因此不存在漏电和闩锁效应。

对于FD-SOI器件,它并不是通过调整沟道掺杂浓度来调节阈值电压,因为FD-SOI器件的氧化埋层很薄,只有20nm; 这么薄的氧化埋层,可以当做是FD-SOI的第二个栅氧化层,衬底就是栅极(类似FIN-FET的结构)。

所以只需要调节背面偏置电压,就可以获得不同的阈值电压。

-

具有负偏压的IR2110 驱动电路2008-12-03 0

-

常见几种SOI衬底及隔离的介绍2012-01-12 0

-

简述LED衬底技术2012-03-15 0

-

传输门的源极与衬底问题2012-03-29 0

-

NE555中文资料详解2012-08-20 0

-

FAT32文件系统详解2016-08-17 0

-

一文详解无直流偏压的电感器设计2020-10-30 0

-

一文详解接地技术2020-11-02 0

-

基于Si衬底的功率型GaN基LED制造技术,看完你就懂了2021-04-12 0

-

负偏压增强金刚石膜与衬底结合强度的理论研究2009-05-16 797

-

马赫曾德尔调制器偏压控制技术研究2015-11-09 564

-

硅基氮化镓衬底是什么 衬底减薄的原因2023-02-14 1352

-

什么是电容的直流偏压特性?如何规避偏压影响呢?2023-11-10 1149

全部0条评论

快来发表一下你的评论吧 !