通过改进低值分流电阻器的焊盘布局来优化大电流检测精度

描述

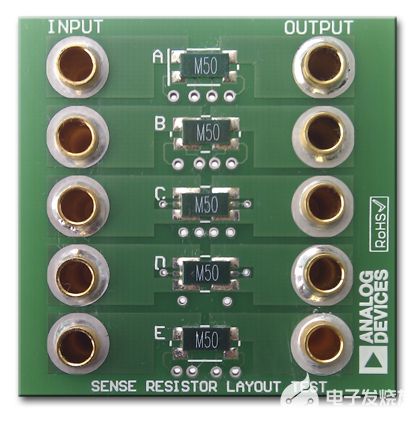

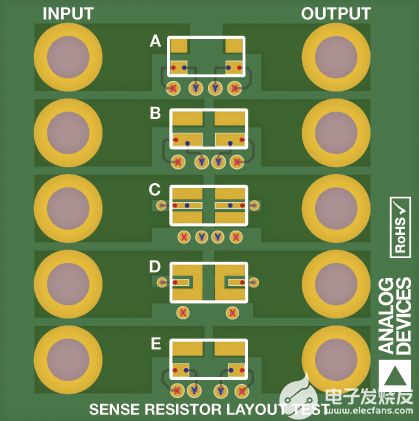

电流检测电阻器具有各种形状和尺寸,用于测量许多汽车、电源控制和工业系统中的电流。当使用非常低值的电阻(几毫欧或更小)时,焊料的电阻成为检测元件电阻的很大一部分,并显着增加测量误差。高精度应用通常使用4端子电阻和开尔文检测来降低这种误差,但这些专用电阻可能很昂贵。此外,在测量大电流时,电阻焊盘的尺寸和设计在确定检测精度方面起着至关重要的作用。本文介绍一种替代方法,该方法使用具有4焊盘布局的标准低成本2焊盘检测电阻实现高精度开尔文检测。图1显示了用于表征由五种不同布局引起的误差的测试板。

图1.检测电阻布局测试PCB。

检流电阻器

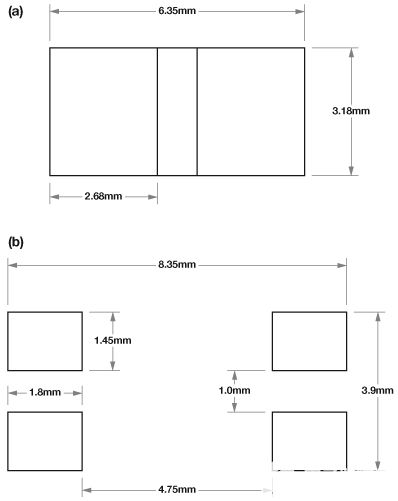

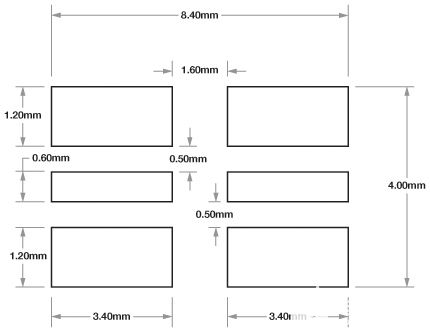

常用的检流电阻提供低至 0.5 mΩ 的电阻值,采用 2512 外壳封装,功耗高达 3 W。为了突出最坏情况下的误差,这些实验采用了一个0.5 mΩ、3 W电阻和1%容差(Welwyn/TTelectronics的部件号ULRG3-2512-0M50-FLFSLT)。其尺寸和标准4线基底面如图2所示。

图2.(a) ULRG3-2512-0M50-FLFSLT电阻器尺寸;(b) 标准 4 焊盘封装。

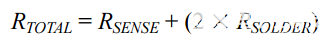

传统足迹

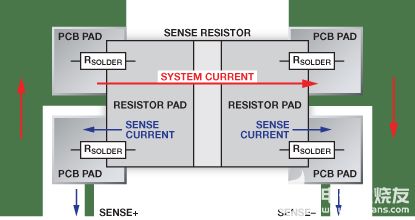

对于开尔文检测,必须对标准2线封装中的焊盘进行划分,以便为系统电流和检测电流提供单独的路径。图 3 显示了此类布局的示例。系统电流采用红色箭头所示的路径。如果使用简单的 2 焊盘布局,则总电阻为:

为避免额外的电阻,电压检测走线需要直接布线至检测电阻焊盘。系统电流仍会导致上部焊点两端的压降显著,但检测电流将导致下部焊点两端的压降可以忽略不计。因此,这种分离焊盘方法消除了测量中的焊点电阻,提高了系统的总精度。

图3.开尔文感应。

优化开尔文足迹

图3所示布局比标准2焊盘方法有了显著改进,但对于极低值电阻(0.5 mΩ或更低),焊盘上检测点的物理位置和流过电阻的电流对称性变得更加重要。例如,ULRG3-2512-0M50-FLFSLT是一种固体金属合金电阻器,因此沿焊盘的每一毫米电阻都会影响有效电阻。使用校准电流,通过比较五个自定义封装的压降来确定最佳检测布局。

测试线路板

图 4 显示了在测试 PCB 上创建的五种布局模式,标记为 A 到 E。在可能的情况下,将迹线路由到沿传感垫不同位置的测试点,如颜色编码点所示。各个电阻器占位面积为:

标准 4 线电阻,基于 2512 推荐封装(参见图 2(b))。焊盘外边缘和内边缘(x 轴)的检测点对(X 和 Y)。

与A类似,但焊盘向内拉长,以更好地覆盖焊盘区域(见图2(a))。感应点位于焊盘的中心和末端。

通过使用焊盘的两侧提供更对称的系统电流。还将感知点移动到更中心的位置。感应点位于焊盘的中心和末端。

与C类似,但在最内侧连接系统电流焊盘。仅使用外部感应点。

A 和 B 的混合体。系统电流流过较宽的焊盘,检测电流流过较小的焊盘。检测点位于焊盘的外边缘和内边缘。

图4.测试PCB布局。

使用模板施加焊料并在回流炉中回流。使用了ULRG3-2512-0M50-FLFSLT电阻器。

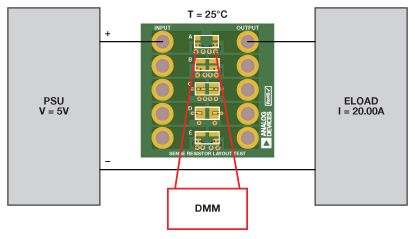

测试程序

测试设置如图 5 所示。20 A的校准电流通过每个电阻器,而电阻保持在25°C。 在使能负载电流后不到1秒内测量产生的差分电压,以防止电阻温度上升超过1°C。 监测每个电阻器的温度,以确保测试结果记录在25°C。 20 A时,0.5 mΩ电阻两端的理想压降为10 mV。

图5.测试设置。

测试结果

表1显示了使用图4所示检测板位置的测量数据。

表 1.测量的电压和误差

| 脚印 | 感应垫 | 测量值(毫伏) | 误差 (%) |

| 一个 |

Y |

9.55 | 4.5 |

| X | 9.68 | 3.2 | |

| B |

Y |

9.50 | 5 |

| X | 9.55 | 4.5 | |

| C | Y | 9.80 | 2 |

| X | 9.90 | 1 | |

| D | X | 10.06 | 0.6 |

| E | Y | 9.59 | 4.1 |

| X | 9.60 | 4 | |

| 顶垫* | 12.28 | 22.8 | |

| *无开尔文感应。测量主大电流焊盘两端的电压,以证明与焊接电阻相关的误差。 | |||

观察

封装 C 和 D 的误差最小,结果和变化在各个电阻容差范围内相当。首选封装 C,因为它不太可能引起与元件放置公差相关的问题。

电阻器外端的检测点可在每种情况下提供最准确的结果。这表明电阻器的大小由制造商调整到整个长度。

请注意,在不使用开尔文检测的情况下,与阻焊电阻相关的误差为 22%。这是约0.144 mΩ的等效焊接电阻。

封装 E 演示了不对称焊盘布局的效果。在回流焊期间,元件被拉到焊料最多的焊盘上。应避免这种类型的足迹。

结论

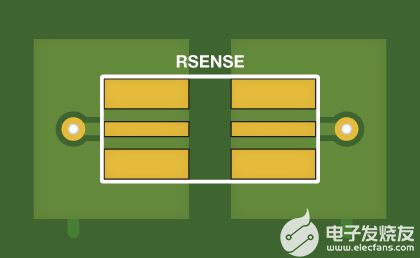

根据所示结果,最佳封装为C,预期测量误差小于1%。该封装的推荐尺寸如图 6 所示。

图6.最佳占地面积。

检测迹线的布线也会对测量精度产生影响。为了达到最高精度,应在电阻的边缘测量检测电压。图7显示了使用过孔将焊盘外边缘布线到另一层的推荐布局,从而避免切割主电源层。

图7.推荐的 PCB 走线布线。

本文中的数据可能不适用于所有电阻器,结果可能会有所不同,具体取决于电阻器的组成和尺寸。应咨询电阻器制造商。用户有责任确保封装的布局尺寸和结构符合各个 SMT 制造要求。ADI公司对因使用此足迹而可能出现的任何问题不承担任何责任。

审核编辑:郭婷

-

芯片分流电阻器 蝴蝶端电阻器2012-10-24 0

-

改进低值分流电阻的焊盘布局,优化高电流检测精度2018-10-23 0

-

分流电阻因测量电流而发热2018-11-27 0

-

电流检测基本原理与容易忽视的细节2019-03-24 0

-

浅析分流电阻器2019-05-21 0

-

如何根据精度要求和成本来选择分流器和电流检测放大器2020-12-30 0

-

电流检测电阻器的相关资料分享2021-12-31 0

-

如何使用分流电阻测量电路电流2022-07-27 0

-

改进低值分流电阻的焊盘布局,优化高电流检测精度2012-11-01 2362

-

改进低值分流电阻的焊盘布局,优化高电流检测精度2016-01-07 630

-

什么是电流检测电阻器2023-04-30 1311

-

分流电阻器的应用2023-12-23 356

-

分流电阻器的定义及特性 分流电阻器的电流共享能力简析2024-02-27 1099

-

ROHM 6432尺寸金属板分流电阻器2024-04-07 123

全部0条评论

快来发表一下你的评论吧 !