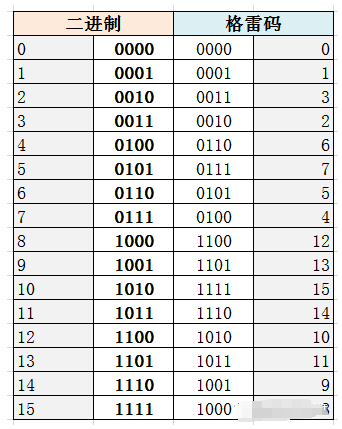

格雷码与二进制转换

描述

格雷码是一种循环二进制编码,特点是相邻数变化时只有一位数据跳变。

- 4位二进制和格雷码对应如下:

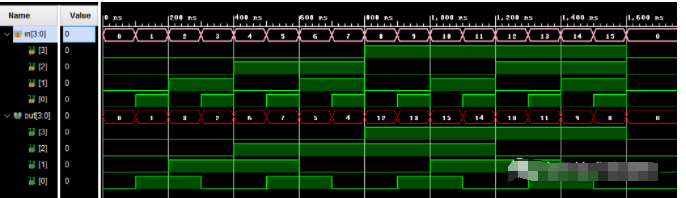

1、二进制到格雷码转换

- Verilog实现

1module bin_to_gray

2#(

3 parameter WIDTH = 4

4)

5(

6 input [WIDTH-1:0] in,

7 output [WIDTH-1:0] out

8);

9

10assign out = in ^ (in >> 1);

11

12endmodule

- 仿真波形:

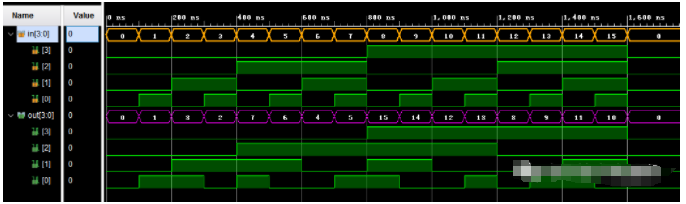

2、格雷码转二进制

- Verilog实现:

1module gray_to_bin

2#(

3 parameter WIDTH = 4

4)

5(

6 input [WIDTH-1:0] in,

7 output [WIDTH-1:0] out

8);

9

10// assign out[0] = ^in[3:0];

11// assign out[1] = ^in[3:1];

12// assign out[2] = ^in[3:2];

13// assign out[3] = in[3];

14

15genvar i;

16generate

17 assign out[WIDTH-1] = in[WIDTH-1];

18 for(i=0; i1; i=i+1) begin

19 assign out[i] = ^in[WIDTH-1:i];

20 end

21endgenerate

- 仿真波形:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

全部0条评论

快来发表一下你的评论吧 !