良好的ESD保护是什么样的

描述

随着系统复杂性的增加和灵敏度的不断提高,了解良好的ESD保护是什么样子以及如何选择适合系统及其应用的正确ESD保护器件至关重要。

电子系统正确运行是不够的,它必须在应用程序可能面临的所有条件下继续以安全的方式运行。因此,必须非常小心地保护系统免受ESD撞击的中断或损坏。

从系统的角度来看,我们可以通过仔细管理整体系统设计来帮助最大限度地减少任何潜在的ESD影响。例如, 我们可以首先确保将敏感和重要的电路放置在远离电路板周边的位置.旨在使用最短的电气路径连接到保护装置,并避免寄生电感。随着输入浪涌能量在保护器件中耗散,将低电容ESD保护尽可能靠近外部I/O端口非常重要。

我们还希望在正常运行期间保护装置对系统有效不可见。应尽量减少数据通道带宽的恶化 - 眼图应保持打开状态。然而,保护器件需要立即做出反应,在浪涌和ESD事件期间将危险的电流和电压尖峰分流到地。

如何保护设备 – 首先要做的事

了解罢工可能来自何处只是一个开始。是来自人体接触(人体模型)、其他设备(机器模型)还是来自设备的正常使用(带电设备模型)?回答这个问题将使人们了解设备需要什么级别的保护。

下一个要问自己的问题是,我们的目标是保护什么。接口特别容易受到ESD损坏和EMI干扰的影响,但对于大多数接口来说,外部ESD保护器件将提供良好的保护。相反,非常快的收发器SoC需要高度先进的ESD保护器件来实现目标IEC ESD鲁棒性。当今结合了电源和数据功能的接口,如USB Type-C,在选择保护时需要更加小心(因为我们还需要考虑数据线和电源线V之间的泄漏或短路情况)。总线).

系统级鲁棒性 – 最薄弱的环节

我们经常听说系统级鲁棒性与各个组件的鲁棒性直接相关。在实践中,这取决于几个因素。最弱的系统相关设备(通常是 SoC)的稳健性是关键。但保护器件的特性也是如此,例如,它能够将浪涌电压箝位到足够低的水平,让SoC能够生存,同时仍然反应足够快,并在其使用寿命期间承受许多ESD事件。其他重要因素包括PCB布局,电线的欧姆电阻和任何电容/电感寄生元件。

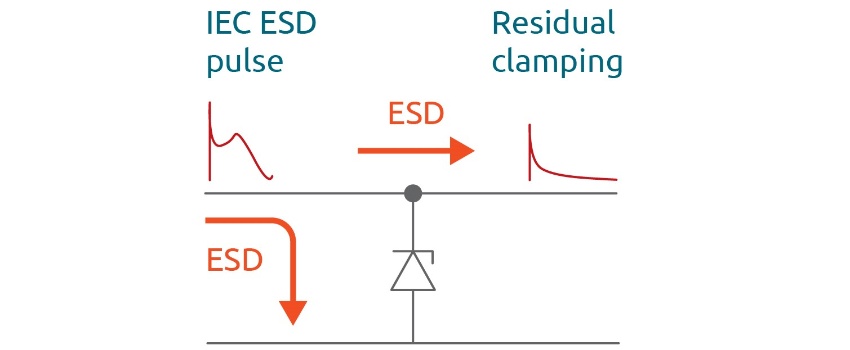

静电放电和残余钳位

为了获得良好的系统级鲁棒性,选择合适的ESD保护对于在ESD冲击或其他浪涌事件期间实现系统IC I/O引脚的最小残余电压至关重要。低电容规格和符合RF标准的布线概念将对信号完整性的影响降至最低。SoC 的端口引脚越敏感,保护应该越有效。

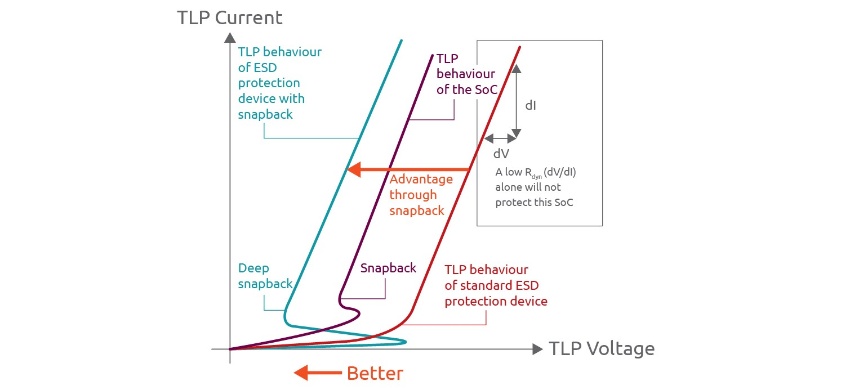

为了将低电容与极低的ESD脉冲箝位电压相结合,高级器件在ESD触发时提供主动回弹行为。此类设备在正常工作时具有高阻抗,但在触发后切换到低阻抗状态。在ESD事件发生后,它们将再次关闭,以便正常的数据通信可以继续。

动态电阻是保护器件的重要器件参数。低值意味着当器件必须分流较高电流时,钳位电压略有增加。

获得正确的特性

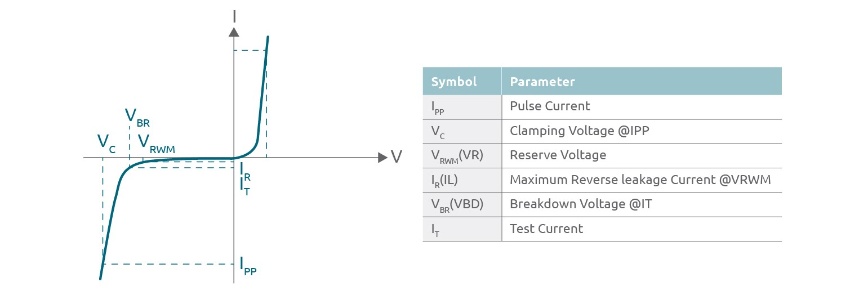

了解数据手册中器件的关键参数,尤其是“限值”,有助于选择合适的ESD保护器件。其中,关断电压VRWM表示漏电流低于指定值I的最大工作电压范围.RM.要指示设备的稳健性,还要检查 I公私合一这是应用具有 61000/4 μs 时序的 IEC5-8-20 脉冲时器件可以承受的最大浪涌电流。

ESD和TVS的单向IV特性曲线

而器件的击穿电压VBR很重要,对于回弹设备,此参数可能会产生误导。其他需要注意的特性包括二极管电容Cd这与信号线的最大频率有关。保护接口时,VCL箝位电压也是关键,对于不同峰值电流下的IEC61000-4-5脉冲IPP.最后但并非最不重要的一点是,寻找较低值的动态电阻R戴恩以获得更好的箝位性能并监控 TLP 曲线,该曲线显示了 ESD 等高速脉冲的箝位能力。

审核编辑:郭婷

-

ESD保护基础知识#电子元器件 #ESD #保护器件 #技术分享 #电子产品学习电子知识 2023-05-07

-

ESD保护基础知识六 #技术分享 #实用技术分享 #ESD#静电防护#电子元器件 #电子产品学习电子知识 2023-05-07

-

如何设计对esd保护上海雷卯电子科技有限公司 2023-07-09

-

ESD保护策略解析2010-08-18 0

-

ESD保护界线新技术2011-01-27 0

-

保护元件免受ESD的方法2014-02-14 0

-

TVS管与ESD保护二极管的区别2015-09-16 0

-

什么样的芯片才能真正的保护程序呢?2015-12-18 0

-

ESD保护管2018-10-17 0

-

ESD保护元件介绍2020-03-19 0

-

如何进行双极型集成电路的ESD保护?2021-04-07 0

-

对于450M带宽40兆,要保持良好的信噪比,应该选择什么样的AD?2023-12-06 0

-

HDMI接口的ESD保护设计要点2010-02-25 1971

-

用于SD卡保护的4重ESD保护阵列-PESD3V3X4UHM2023-02-20 156

全部0条评论

快来发表一下你的评论吧 !