Vivado调用第三方仿真软件查看波形的过程中存在的一些问题

描述

Vivado调用Questa Sim或ModelSim仿真中存在的一些自动化问题的解决方案。

Vivado调用Questa Sim仿真中存在的一些问题

首先说明一下Modelsim与Questa Sim都可以与Vivado联调,也比较相似,但是Questa Sim比Modelsim功能更加广泛,对于System Verilog的语法支持更加完善,本文以Questa Sim为例说明一下Vivado调用第三方仿真软件查看波形的过程中存在的一些问题。

1、添加新的观测信号需要重新仿真

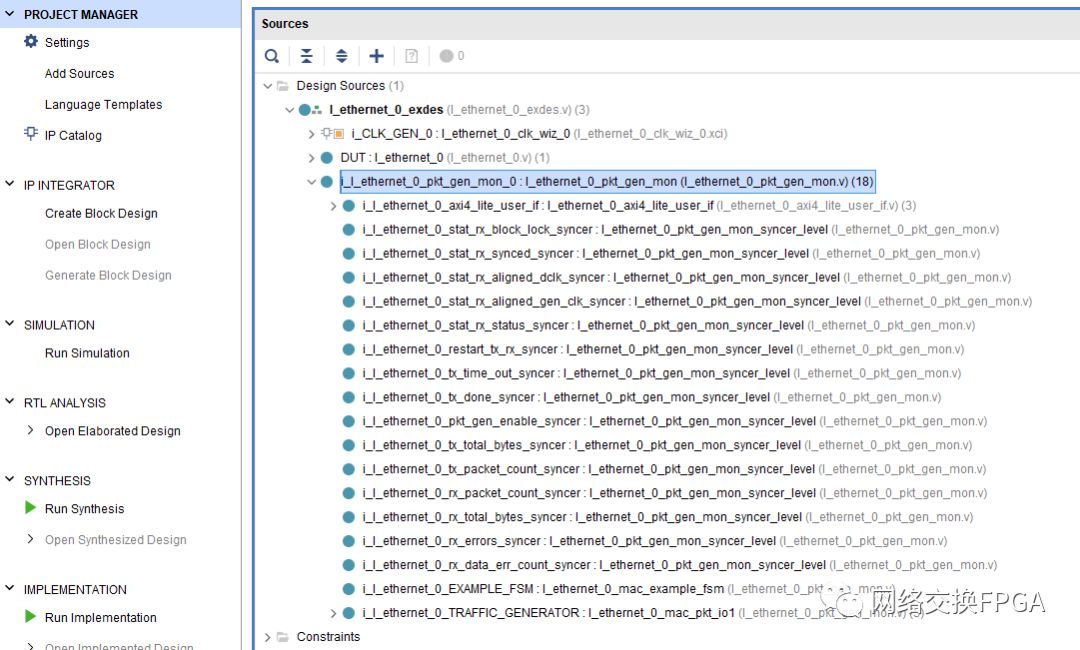

Vivado直接调用Modelsim/QuestaSim进行仿真时,波形文件里默认只会出现仿真最顶层中包含的信号,若此时将仿真运行一段时间后,想要查看其他模块信号波形时,需要重新仿真或者运行do XXX_simulate.do方可。 以图1所示工程为例,

图1 vivado示例工程

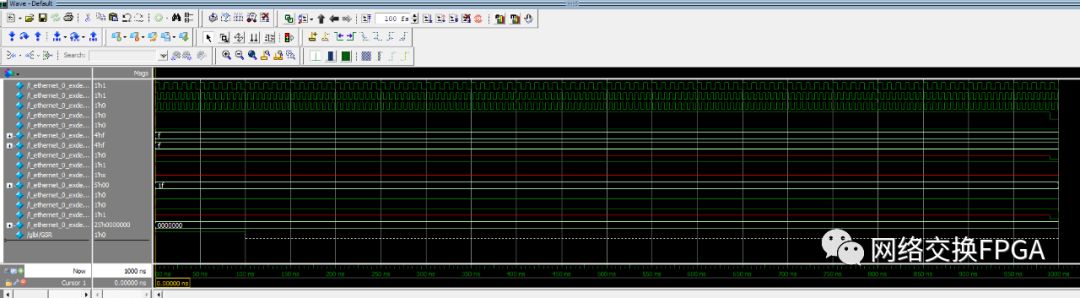

在这个工程中,我们调用Questa Sim进行仿真,可以看到顶层模块会自动跑100ns,如图2所示。

图2 QuestaSim仿真波形

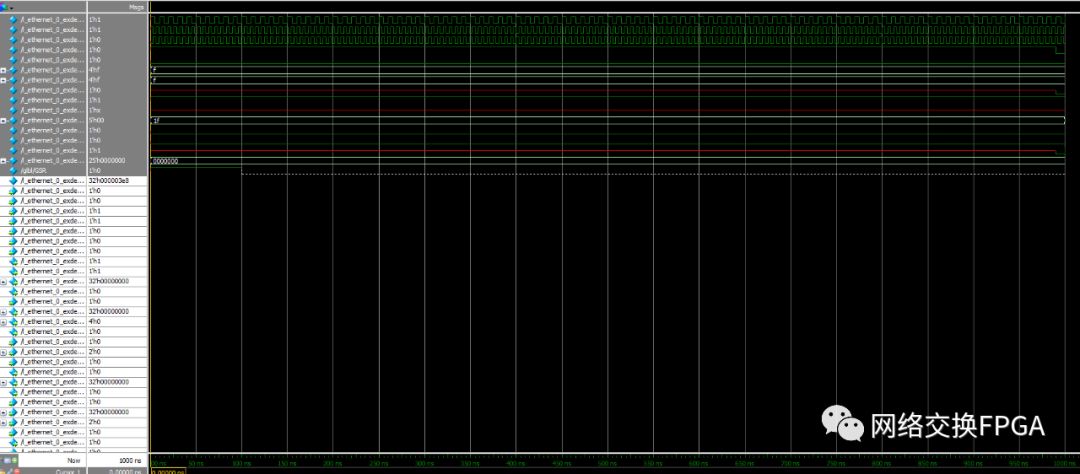

此时,我们若想查看l_ethernet_0_pkt_gen_mon这个模块的波形时,直接进入波形界面进行添加,结果如图3所示。

图3 QuestaSim仿真波形

从图3中可以看到,当模块的信号被添加进来后,已经运行过的仿真时间内,新加入的信号没有仿真结果。

2、修改逻辑代码后,需要重新调用仿真器

在代码调试过程中,修改部分逻辑代码后(不包括IP核),如果想要查看修改后工程的仿真结果,需要关闭当前的仿真器,从vivado中重新调用方可。

其原因是vivado在生成XXX_compile.do文件时,会在其末尾自动添加“quit -force”语句,而更改了相应的代码文件后,我们需要执行“do XXX_compile.do”命令重新编码整个库,然而在运行此文件时,当前的仿真器会被强制退出。

解决方案

为了解决上述问题,同时更加方便使用,本文使用TCL语言,编写了一个较为方便的do文件,其可以实现如下功能:

1、对XXX_compile.do自动修改

对XXX_compile.do自动修改,去除其末尾的“quit -force”,并生成新的compile.do文件,其对应的源代码如下:

set filename [glob *_compile.do]

set content [open $filename r+]

set row 0

while {![eof $content]} {

incr row

gets $content line

set list($row) $line

}

close $content

set filename2 "compile.do";

set content [open $filename2 w+]

for {set i 1} {$i <= $row} {incr i} {

if {![string match "quit -force" $list($i)]} {

puts $content $list($i)

}

};

close $content

2、使用“log -r /*”命令

该命令可以让modelsim/Questa Sim在进行仿真中,对所有信号同步进行仿真,从而解决新加入的观测信号没有仿真结果的问题;

3、保证仿真器不退出

当修改工程中的逻辑代码(不含IP核)后,只需要运行该do文件,其自动进行编译和仿真,且使用修改后的compile.do文件,保证仿真器不退出,其对应的源代码如下:

set filename compile.do do $filename set filename [glob *_simulate.do] do $filename log -r /* restart -force run 1ms

例程

在使用该do文件之前,需要首先通过vivado调用modelsim/ questasim,然后将do文件拷贝到工程对应的behave文件夹下。

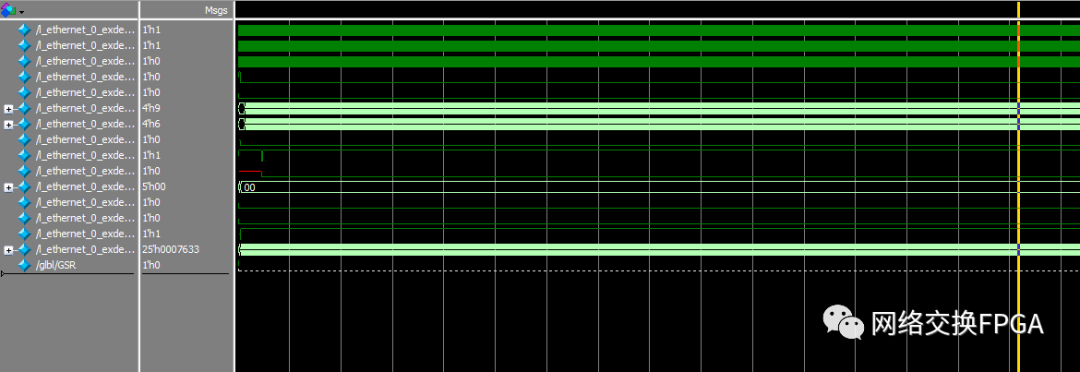

仍以图1所示工程为例,当修改了代码内部分逻辑后,在QuestaSim的transcrip界面,输入命令do auto_update_sim.do即可自动重新编译、仿真,结果如图4所示(默认仿真时间设置为1ms)

图4 QuestaSim仿真波形

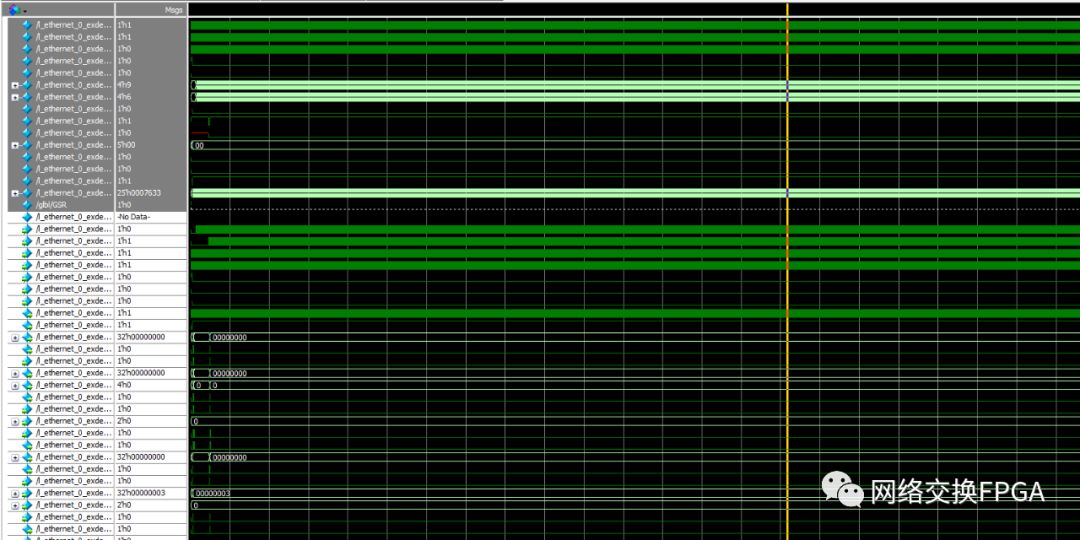

添加了l_ethernet_0_pkt_gen_mon这个模块,可以发现仿真过的时间内同样有仿真结果,如图5所示。

图5 QuestaSim仿真波形

完整源码

set filename [glob *_compile.do]

set content [open $filename r+]

set row 0

while {![eof $content]} {

incr row

gets $content line

set list($row) $line

}

close $content

set filename2 "compile.do";

set content [open $filename2 w+]

for {set i 1} {$i <= $row} {incr i} {

if {![string match "quit -force" $list($i)]} {

puts $content $list($i)

}

};

close $content

set filename compile.do

do $filename

set filename [glob *_simulate.do]

do $filename

log -r /*

restart –force

run 1ms

审核编辑:刘清

-

如何打开第三方软件2012-09-11 0

-

求高手讨教!求指点!求鄙视!各种求!调用第三方软件!2013-04-25 0

-

如何把第三方库加到PROTEUS中?2013-06-15 0

-

如何在LabVIEW中嵌入第三方软件界面2014-04-27 0

-

labview 通过API调用第三方软件 无法通过ID获取窗口元素的句柄2017-12-11 0

-

第三方dll调用问题!!!2018-05-11 0

-

LabVIEW与第三方软件交互问题2018-12-26 0

-

国内知名第三方检测认证机构排名2019-07-19 0

-

关于LabVIEW调用第三方exe,如何去控制第三方exe按钮的问题2020-08-12 0

-

buildroot如何添加支持第三方软件?2021-04-02 0

-

头文件中包含第三方文件2021-08-18 0

-

labview 控制第三方软件界面或控件的方式2021-11-16 0

-

鸿蒙开源第三方组件资料合集2022-03-23 0

-

在Framework下调用第三方的C++算法库2022-11-24 0

-

Vivado调用Questa Sim或ModelSim仿真小技巧2021-09-02 7550

全部0条评论

快来发表一下你的评论吧 !