Tapped routing知识点

电子说

描述

Tapped routing由Intel公司2015年3月份提出,主要用在处理器SKYLAKE平台,DDR4的走线方式;

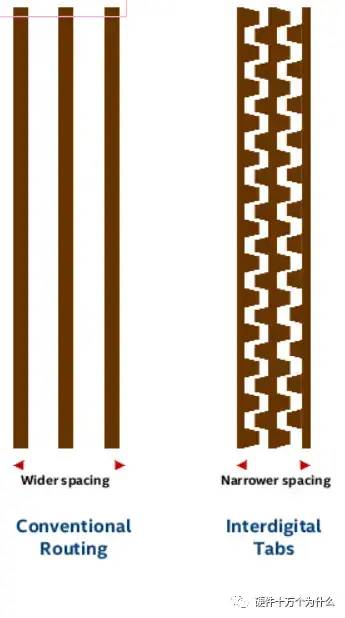

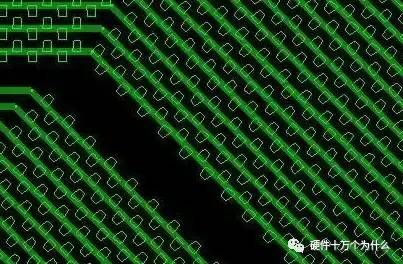

交叉手指状的tabbed routing 使用面对相邻差分线中tab之间空隙的交替梯形tab。这种tab可以压缩走线,建立新的走线通道,并降低串扰,这可以走更长的线。这种tabbed routing专门针对外部层面。

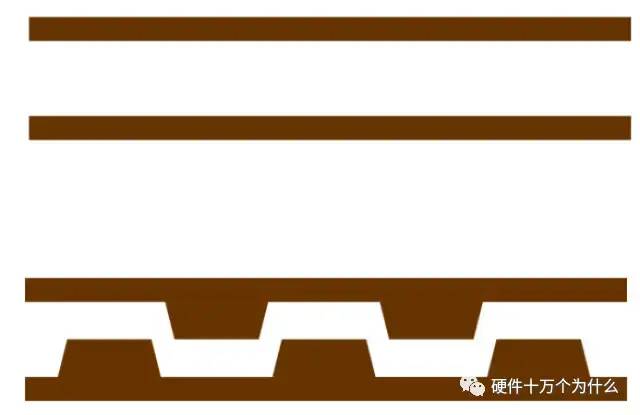

Tabbed Routing主要的方法是在空间比较紧张的区域(一般为BGA区域和DIMM插槽区域),减小线宽,而增加凸起的小块(Tab),如下图所示。

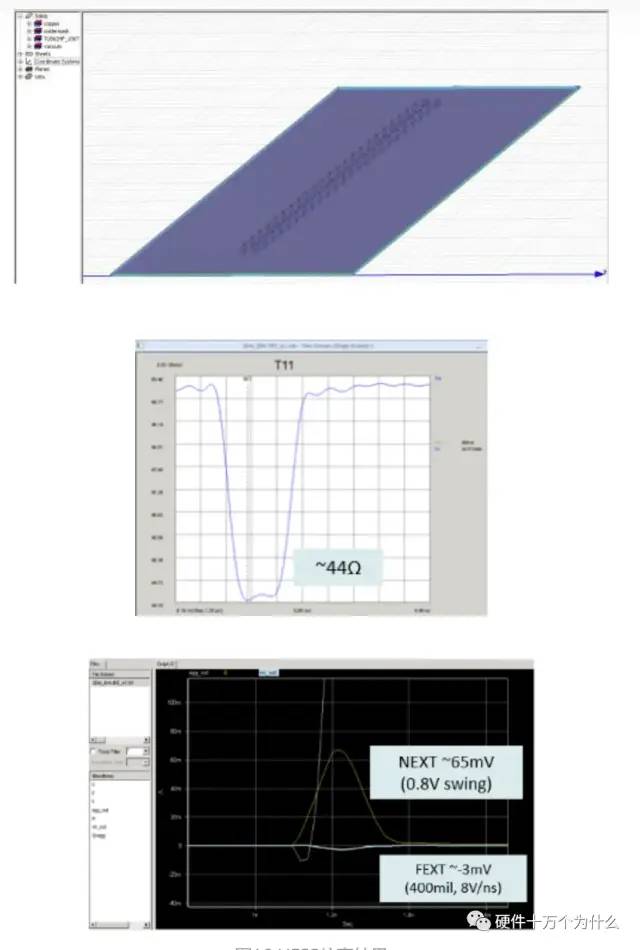

这种方法可以增加两根线之间的互容特性而保持其电感特性几乎不变,而增加的电容可以有效控制每一层的的阻抗,减小外层的远端串扰。仿真结果如下图所示。

由仿真结果可以看出来,该方法对阻抗和远端串扰确实可以很好的平衡,当然,对于Tab的尺寸,需要根据实际PCB做详细的仿真设计,Intel也提供了一些Tool可以参考。

PCB走线必须传输电流和相关电磁场,场的传输受到PCB材料的介电特性的影响。在均匀介质中,场以相同的速度传播(带状线),在非均匀结构中,场以不同的速度通过不同的介电材料传播(微带线)。这种传播差异导致在非均匀结构中产生正向波,从而在远端(接收器)处产生附加噪声。这在均质结构中不会发生,这种影响的严重程度随信号频率的增加而增加。

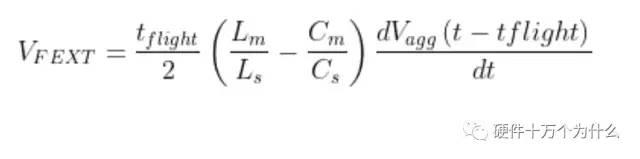

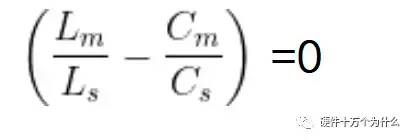

接收端的远端串扰就是奇模信号和偶模信号之间的传播延时。对于互相耦合走线,远端串扰的电压由以下公式定义:

FEXT一般指远端串音。远端串音(Far-End Crosstalk)是串音的一种,指信号传输中平行的两对线,干扰线对施加给被干扰线对远端的串音。VFEXT是指源端串音导致的电压变化。

传输时间固定,为了消除前向串扰,可以让感性容性关系为0,即:

因为感性已经固定,增加走线的tab(两个线之间的距离和间距)可以调整容性。Cs是自容,Ls是自感,Cm是互容,Lm是互感。通过tab的调整,让上面式子尽量为0。

所有的tabbed routing方案都会影响阻抗和噪声。Pin Field区域的tab可以改善阻抗管控,可以用在所有层面,Pin field区域的tab看起来像是蛇形走线,实际的走线布局由pin field区域的实际需求决定。

Pin Field区域的Tabbed Routing不会管控阻抗到一个实际的值,它相当于提供了一个额外的电容元件,根据它来确定阻抗,以提供跨供应商的更一致的阻抗结果。对于传统的pin field区域走线,阻抗会随着板厂变化,板厂也不会管控此区域的走线阻抗。

交叉手指状的tabbed routing 使用面对相邻差分线中tab之间空隙的交替梯形tab。这种tab可以压缩走线,建立新的走线通道,并降低串扰,这可以走更长的线

-

运放知识点2012-08-20 0

-

【信盈达】C语言知识点的总结2018-10-08 0

-

使用PADS软件进行PCB设计,有哪些基础知识点?2019-08-20 0

-

关于前端有哪些知识点2020-07-08 0

-

电机与电气控制基础的知识点2021-01-22 0

-

FPGA的基础知识点及工作原理是什么2021-04-30 0

-

电机与拖动知识点及其试题2021-06-29 0

-

STM32外部中断的知识点2021-08-13 0

-

STM32外部中断知识点概述2021-08-16 0

-

关于AUTOSAR架构的知识点看完你就懂了2021-10-18 0

-

GDB的知识点汇总,绝对实用2021-12-24 0

-

JTAG调试的知识点汇总,绝对实用2021-12-24 0

-

外部中断的知识点汇总,绝对实用2022-01-21 0

-

DBC编辑的知识点汇总,绝对实用2022-02-09 0

-

SPI协议的知识点大合集,绝对实用2022-02-17 0

全部0条评论

快来发表一下你的评论吧 !