有效的ESD和浪涌保护 - 平衡问题

描述

在为您的产品构建ESD保护策略时,需要解决和测试多个因素,关键在于获得平衡并测试其效率。

电子系统和组件对ESD越来越敏感。IC和半导体工艺的小型化、密闭空间内的多种电源要求、数据速率的提高、单个SoC上功能的更大集成、数据和电源接口的组合——所有这些都会导致更高的瞬态电压损坏风险。每个单独的因素对ESD和浪涌保护都有不同的要求,并且某些应用是所有因素的组合,这使得ESD保护选择更具挑战性。

在Nexperia,当我们考虑什么是有效的ESD保护器件时,我们会考虑三个关键参数 - 我们称之为ESD保护的三大支柱:

高鲁棒性 - 保护器件免受 ESD 和浪涌脉冲的影响

低钳位电压 - 为了保护 SoC,与低动态电阻齐头并进,以确保在浪涌电流增加时箝位电压不会上升

低电容 - 在高速接口中尤其重要,以保持出色的信号完整性。

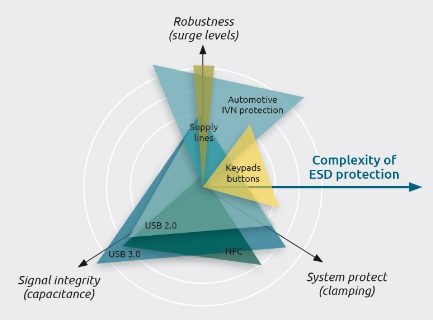

三个关键参数与不同应用领域的关系

如图所示,这些属性是相互依赖的,因此改进一个属性可能会对其他属性产生不利影响。对于某些应用,这不是问题,因为它们只需要在一个或两个属性中具有良好的性能。然而,随着通过接换数据的高速率,当今的互联世界对保护设备的需求越来越大,以便在所有三个领域提供最佳性能。在这些情况下,有效的解决方案必须平衡ESD保护的所有三大支柱。

Nexperia对此的回答是TrEOS保护,它实现了这种平衡,为系统提供了最先进的ESD保护。为了确保解决方案确实对瞬态和静电放电有效,我们还超越了理论,在现实条件下测试我们的解决方案。

TLP / VF-TLP 测试

大多数静电放电不会被用户注意到,但会严重损坏敏感的电子设备。国际公认的标准测试方法和技术(IEC61000-4-2 / IEC61000-4-5)提供了良好的洞察力,但结果可能因所使用的测试设备而异。因此,随着当今高速接口数据速率的提高,正在使用两种相对较新的测试来确保满足性能要求:TLP(传输线脉冲)和VF-TLP(超快速TLP)测试是广泛采用的表征完整接口和ESD保护组件的方法。

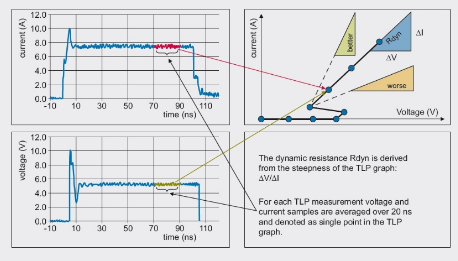

TLP 测量器件在脉冲宽度较短(通常为 100 纳秒持续时间)的应力下的性能属性,快速上升和下降时间为 1 纳秒或 600 皮秒。TLP脉冲大致相当于一个完整的ESD脉冲的能量。相比之下,VF-TLP使用更短的测试脉冲,上升和下降时间低至100 ps。这为确定ESD保护器件的开关速度提供了良好的指示,并且可以扩展到检查1圣和 2德·分别达到峰值。

使用测试产生的测量曲线有助于确定哪种保护装置适合安全可靠地保护产品。在我们的ESD测试实验室,我们不仅检查我们自己产品的性能,而且还对完整的电路板进行TLP测试。根据我们的经验,这是找到保护整个系统平衡的最佳方法,因为瞬态电压可以利用任何弱点。我们全面的真实测试带来了更深入的见解和更安全的结果。

从 TLP 测试事件导出的 TLP 曲线

为您的系统提供正确的平衡

了解核心参数和标准测试方法只是为您的系统选择正确的ESD保护策略的第一步。选择合适的保护解决方案还需要了解需要保护哪些接口,并且应考虑整个系统的设计及其应用。

审核编辑:郭婷

-

ESD如何选择最有效的保护方案?2021-04-08 0

-

RS-422/RS-485接口的ESD/浪涌保护2020-11-19 0

-

超低负载电容高浪涌ESD保护TVS阵列2020-10-27 0

-

HD-BNC接口静电浪涌保护2020-11-27 0

-

如何保护隔离总线节点免受ESD/EFT和瞬间浪涌的影响?2021-03-08 0

-

请问浪涌保护器能有效对抗雷击吗?2021-03-17 0

-

ESD保护装置·对策元件基础知识——ESD(静电放电・浪涌)保护装置・对策元件是什么?2017-03-02 4571

-

ESD保护装置·对策元件基础知识——ESD(静电放电・浪涌)保护装置・对策元件的种类2017-03-04 2554

-

关于ESD204对HDMI接口的浪涌保护2021-11-10 785

-

ESD和浪涌保护技术应用2022-04-20 4724

-

ESD204对HDMI接口的浪涌保护2022-10-31 216

-

ESD/浪涌保护器件使用方法:各类盘型压敏电阻2023-08-03 731

-

ESD/浪涌保护器件使用方法:贴片压敏电阻2023-08-03 950

-

串联电阻R与半导体ESD电路布线与防浪涌关系2023-08-17 598

-

ESD保护二极管原理介绍2024-02-02 651

全部0条评论

快来发表一下你的评论吧 !