STM32入门学习笔记之时钟树架构(上)

电子说

描述

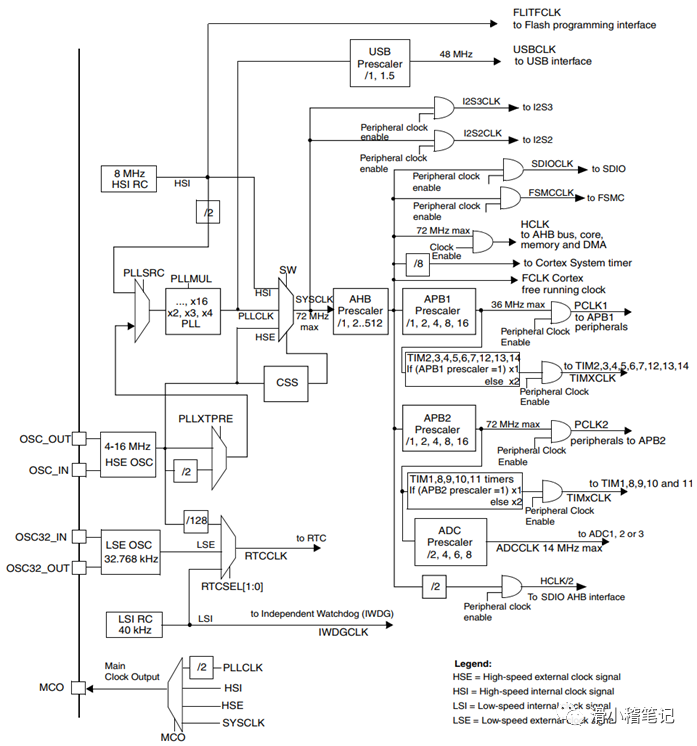

2.1 时钟树结构图

STM32属于Cortex-M3内核的单片机,时钟结构比之前的51单片机较复杂的多,根据数据手册,STM32F103的时钟结构如下图所示。

根据上图可以看到,STM32F103系列单片机具有4个时钟源,内部的8MHz时钟发生器,外部的晶体振荡器接口,最高支持16MHz,外部的32.768kHz晶体振荡器接口和内部的40kHz时钟发生器,其中32.768kHz和40kHz主要用于内部RTC时钟脉冲,8MHz的晶振通过PLL时钟倍乘器,将系统总线时钟提高为72MHz。

STM32F103系列内部具有2条外设时钟总线,APB1和APB2,其中APB2的时钟最高可达72MHz,APB1的时钟最高可达36MHz,通过配置对应的寄存器,就可以将CPU内核时钟提高到最大速度。

通过最小系统可以看到,我们使用外部高速晶体振荡器接口,外接8MHz晶振,RTC则是使用32.768kHz晶振,现在我们来通过数据手册来配置对应的寄存器位来配置APB2时钟达到72MHz,APB1时钟达到36MHz。

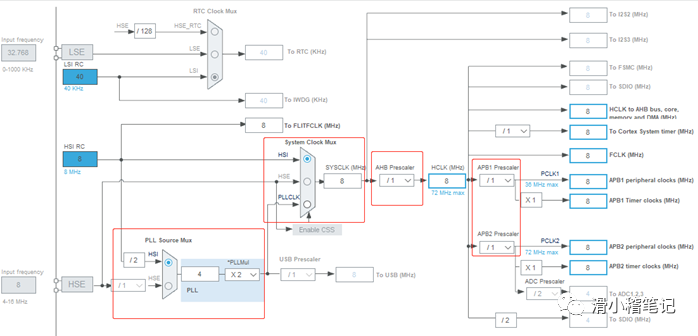

2.2 时钟配置

上图是ST公司推出的一款软件,这款软件可以自动生成寄存器代码,但是我们在这里只用到其中提供的时钟配置功能,通过上面的时钟结构,我们可以得到配置时钟的大概流程。

2.2.1 时钟配置流程

(1)开启HSE时钟接口,这个接口用于使能晶体振荡器输入端;

(2)设置PLL倍频系数为9,因为外接8MHz时钟,所以设置系数为9就可以轻松达到8×9=72MHz的时钟频率;

(3)设置时钟源为PLLCLK,因为HSE使用的时候可以发现最终的输出就是PLL时钟脉冲;

(4)设置APB1时钟总线的分频系数为2,因为APB1时钟总线最高频率只有36MHz;

(5)设置APB2时钟总线的分频系数为1。

2.2.2 相关寄存器

(1) 时钟控制寄存器 :RCC_CR

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | PLLRDY | PLLON | - | CSSON | HSEBYP | HSERDY | HSEON | ||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| HSICAL[7:0] | HSITRIM[4:0] | - | HISRDY | HISON |

Bit 25:PLL准备状态

0:PLL解锁

1:PLL锁定

Bit 24:PLL使能

0:PLL关闭

1:PLL打开

Bit 19:时钟安全系统开关

0:时钟保护关闭

1:时钟保护打开

Bit 18:HSE旁路(禁用HSE振荡器时才能写入)

0:HSE禁止旁路

1:HSE打开旁路

Bit 17:HSE准备状态

0:HSE未准备好

1:HSE准备完毕

Bit 16:HSE时钟使能

0:HSE时钟关闭

1:HSE时钟打开

Bit 15~ Bit 8:HSI校准值(这个值在启动的时候自动初始化)

Bit 7~ Bit 3:HSI微调(对其进行编程以适应电压和温度的变化影响内部HSI的频率。初始值16,步长约为40kHz)

Bit 1:HSI准备状态

0:HIS未准备好

1:HSI准备完毕

Bit 0:HSI时钟使能

0:HIS时钟关闭

1:HSI时钟开启

-

STM32 时钟树的学习2013-05-15 0

-

STM32学习笔记14:基本问题,来讨论一下软件架构2015-01-29 0

-

STM32时钟树学习汇总2021-08-02 0

-

STM32F407之时钟、频率、存储的整体特性2021-08-02 0

-

STM32的RCC时钟树学习内容2021-08-11 0

-

一文读懂时钟树2021-08-11 0

-

STM32时钟系统学习笔记2021-08-11 0

-

STM32时钟学习笔记2021-08-12 0

-

STM32时钟树学习记录2021-08-13 0

-

STM32入门学习笔记 精选资料分享2021-08-24 0

-

stm32之时钟树及systemclock简介2022-03-01 0

-

STM32各模块学习笔记2017-11-30 2981

-

STM32Cube学习教程之时钟树配置的详细资料概述2019-08-14 1182

-

MCU学习笔记_STM32时钟2021-10-28 584

-

STM32入门学习笔记之时钟树架构(下)2023-02-16 492

全部0条评论

快来发表一下你的评论吧 !