STM32入门学习笔记之时钟树架构(下)

电子说

描述

(2) 时钟配置寄存器 :RCC_CFGR

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| - | MCO[2:0] | - | USBPRE | PLLMUL[3:0] | PLLXTPRE | PLLSRC | |||||||||

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ADCPRE[1:0] | PPRE2[2:0] | PPRE1[2:0] | HPRE[3:0] | SWS[1:0] | SW[1:0] |

Bit 26~Bit 24:芯片时钟输出

0xx:禁止输出

100:选择系统时钟SYSCLK

101:选择HSI时钟

110:选择HSE时钟

111:选择PLL分频输出(2分频)

Bit 22:USB时钟分频系数

0:PLL时钟1.5分频作为USB时钟

1:PLL时钟不分频作为USB时钟

Bit 21~Bit 18:PLL倍频系数

0000:2倍频

0001:3倍频

0010:4倍频

0011:5倍频

0100:6倍频

0101:7倍频

0110:8倍频

0111:9倍频

1000:10倍频

1001:11倍频

1010:12倍频

1011:13倍频

1100:14倍频

1101:15倍频

1110:16倍频

1111:16倍频

Bit 17:HSE输入分频器

0:HSE输入不分频

1:HSE输入2分频

Bit 16:PLL时钟选择(PLL处于禁止模式才能写入)

0:HSI时钟2分频作为PLL时钟输入

1:HSE作为PLL时钟输入

Bit 15~Bit 14:ADC分频系数

00:PCLK2分频系数为2

01:PCLK2分频系数为4

10:PCLK2分频系数为6

11:PCLK2分频系数为8

Bit 13~Bit 11:APB2分频系数(最高可达72MHz)

0xx:HCLK不分频

100:HCLK分频系数为2

101:HCLK分频系数为4

110:HCLK分频系数为8

111:HCLK分频系数为16

Bit 10~Bit 8:APB1分频系数(最高只能达到36MHz)

0xx:HCLK不分频

100:HCLK分频系数为2

101:HCLK分频系数为4

110:HCLK分频系数为8

111:HCLK分频系数为16

Bit 7~Bit 4:AHB总线预分频系数

0xxx:SYSCLK不分频

1000:SYSCLK分频系数为2

1001:SYSCLK分频系数为4

1010:SYSCLK分频系数为8

1011:SYSCLK分频系数为16

1100:SYSCLK分频系数为64

1101:SYSCLK分频系数为128

1110:SYSCLK分频系数为256

1111:SYSCLK分频系数为512

Bit 3~Bit 2:系统时钟选择状态

00:HSI作为系统时钟

01:HSE作为系统时钟

10:PLL作为系统时钟

11:保留

Bit 1~Bit 0:系统时钟选择

00:选择HSI作为系统时钟

01:选择HSE作为系统时钟

10:选择PLL作为系统时钟

11:保留

2.3 设置例程

配置STM32的时钟需要创建几个文件,这几个文件如下表所示。

| 文件目录 | 文件名 | 文件功能 |

|---|---|---|

| ./SYSTEM/sys | sys.c | 时钟设置函数外部中断设置函数中断优先级设置函数 |

| sys.h | 数据类型定义 | |

| stm32f103x.h | 定义寄存器结构定义寄存器地址定义中断编号 |

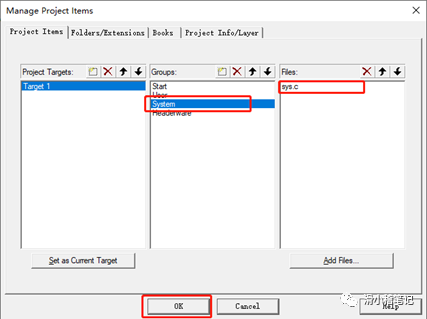

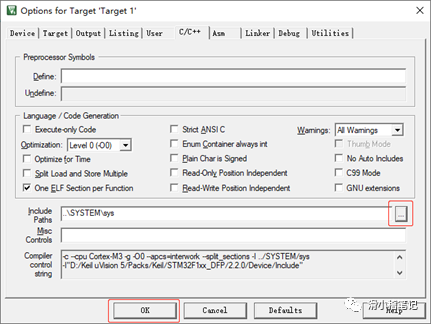

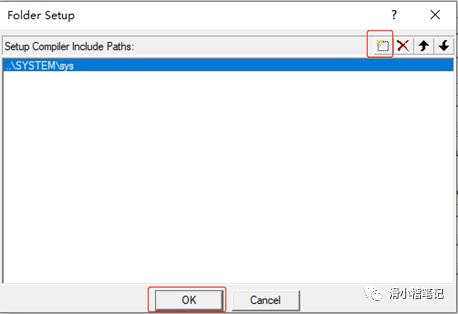

(1)创建上述三个文件,其中c文件添加进工程中,h文件包含进程序中,如下图所示。

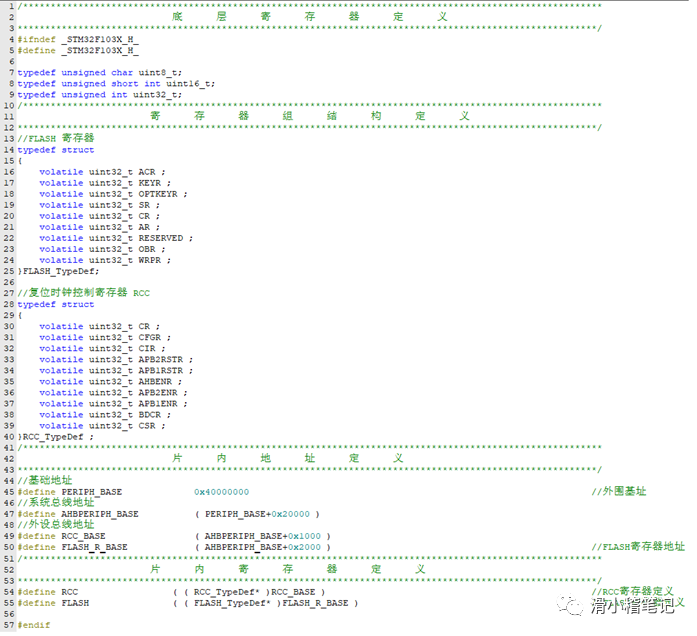

(2)stm32f103x.h文件输入以下内容:

这个文件用于定义程序用到的所有寄存器的地址和结构体,是整个STM32程序的最基础的文件。

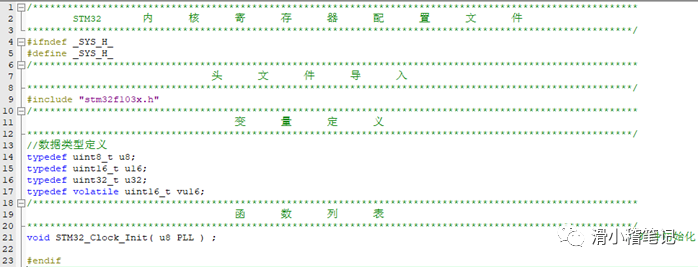

(3)sys.h输入以下内容

sys.h文件用于定义STM32的时钟配置和中断配置,以及后面的端口位操作模式。

(3)sys.c文件输入以下内容

void STM32_Clock_Init( u8 PLL )

{

RCC->CR |= 0x00010000 ; //外部高速时钟使能HSEON

while( !( RCC->CR>>17 ) ) ; //等待外部时钟就绪

RCC->CFGR = 0x00000400 ; //APB1=DIV2;APB2=DIV1;AHB=DIV1;

PLL -= 2 ; //抵消2个单位(因为是从2开始的,设置0就是2)

RCC->CFGR |= ( u32 )PLL<<18 ; //设置PLL值 2~16

RCC->CFGR |= 1<<16 ; //PLLSRC ON

FLASH->ACR |= 0x32 ; //FLASH 2个延时周期

RCC->CR |= 1<<24 ; //PLLON

while( ( RCC->CR&0x02000000 )!=0x02000000 ) ; //等待PLL锁定

RCC->CFGR |= 0x00000002 ; //PLL作为系统时钟

while( ( RCC->CFGR&0x0000000C )!=0x00000008 ) ; //等待PLL作为系统时钟设置成功

}

这个文件的函数就是真正配置时钟的过程,可以对照之前描述的配置时钟的过程来看这段代码

-

STM32 时钟树的学习2013-05-15 0

-

STM32学习笔记14:基本问题,来讨论一下软件架构2015-01-29 0

-

转:STM32F746 Discovery学习笔记4 STM32F107和STM32F746时钟树2016-08-10 0

-

STM32时钟树学习汇总2021-08-02 0

-

STM32F407之时钟、频率、存储的整体特性2021-08-02 0

-

了解一下STM32的时钟树2021-08-06 0

-

STM32的RCC时钟树学习内容2021-08-11 0

-

STM32时钟系统学习笔记2021-08-11 0

-

STM32时钟学习笔记2021-08-12 0

-

STM32时钟树学习记录2021-08-13 0

-

stm32之时钟树及systemclock简介2022-03-01 0

-

STM32各模块学习笔记2017-11-30 2981

-

STM32Cube学习教程之时钟树配置的详细资料概述2019-08-14 1182

-

MCU学习笔记_STM32时钟2021-10-28 584

-

STM32入门学习笔记之时钟树架构(上)2023-02-16 760

全部0条评论

快来发表一下你的评论吧 !