超结高压功率MOSFET驱动参数对开关特性有什么影响

模拟技术

描述

刘松 刘瞻 艾结华 曹雪 张龙

新一代的超结结构的功率MOSFET中有一些在关断的过程中沟道具有提前关断的特性,因此,它们的关断的特性不受栅极驱动电阻的控制,但是,并不是所有的超结结构的功率MOSFET都具有这样的特性,和它们内部结构、单元尺寸以及电压额定等多个因素相关。

超结结构的功率MOSFET外围驱动电路的设计,通常需要外加一些元件和栅极电阻相配合,控制器件的开关速度,保持栅极驱动电路对器件关断过程的相关参数的可控或部分的可控,从而保证器件在极端的条件下工作在可靠的工作区,同时满足系统的效率、温升和EMI要求。

驱动电路设计的关键的控制参数有:

(1)外部串联的栅极电阻(RG);

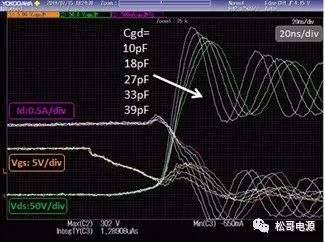

(2)外部并联的栅极、漏极的电容(Cgd);

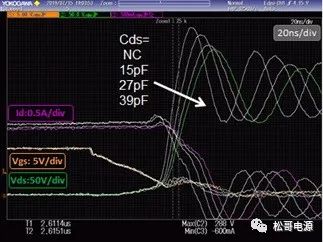

(3)外部并联的漏极、源极的电容(Cds)。

(4)快速关断的二极管和三极管。

(5)外部并联的漏极、源极的电容(Cds).

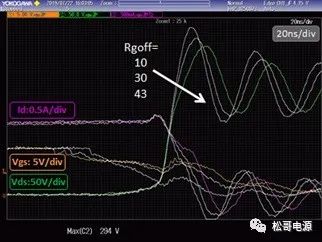

栅极电阻低,开关速度更快,开关损耗更低,但会增加开关过程中功率MOSFET的寄生电感和寄生电容所产生的VDS尖峰电压,加剧栅极的振荡,同时增加开通和关断过程中,电压和电流上升的斜率dV/dt,di/dt。

反之,增加栅极电阻,会增加开关过程中的开通损耗和关断损耗,减小VDS的尖峰电压,减小栅极的振荡,同时降低在开通和关断过程中,电压和电流上升的斜率dV/dt,di/dt。

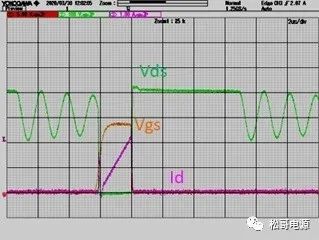

图1: 超结结构的功率MOSFET开关波形

因此,要基于实际的应用和电路特性以及设计的要求,选择合适的RG值。RG的最大值要保持功率MOSFET的开关损耗和温升在设计的范围内,RG的最小值保证VDS的尖峰电压,栅极的振荡,dV/dt,di/dt在设计的范围内。

图2、图3和图4展示了不同的外部参数对关断过程中VDS的尖峰电压,dV/dt和di/dt 的影响,外部并联的栅极漏极的电容(Cgd)以及外部并联的漏极源极的电容(Cds),对于VDS的尖峰电压以及dV/dt的影响,和RG一样具有相同的趋势。

图2:外部的栅极关断电阻对关断特性影响

图3:外部并联栅极源极电容对关断特性影响

图4:外部并联漏极源极电容对关断特性影响

超结结构的功率MOSFET外部驱动参数影响其开关的dV/dt和di/dt,从而影响器件的开关损耗以及相对应的器件的效率和温升和系统效率;另外也会影响系统的EMI和可靠性。这些要求往往相互间彼此矛盾和对立,因此,需要工程师做出优化的处理,满足系统的设计要求。

-

功率MOSFET的阻性负载开关特性2016-12-16 0

-

高压MOSFET驱动器电路2011-12-17 4973

-

功率MOSFET特性参数的理解2022-07-13 535

-

三分钟读懂超级结MOSFET2017-08-09 0

-

超级结MOSFET的优势2018-10-17 0

-

在低功率压缩机驱动电路内,意法半导体超结MOSFET与IGBT技术比较2018-11-20 0

-

超级结MOSFET2018-11-28 0

-

MOSFET的开关特性及其温度特性2018-11-28 0

-

超结功率MOSFET技术白皮书2019-06-26 0

-

如何为电源用高压超结MOSFET增加晶圆级可配置性?2023-02-27 0

-

降低高压MOSFET导通电阻的原理与方法2023-02-27 0

-

高频功率MOSFET驱动电路及并联特性研究2010-11-11 1554

-

功率MOSFET与高压集成电路2011-07-22 2043

-

SiC Mosfet管特性及其专用驱动电源2015-06-12 4764

-

功率MOSFET结构和参数解读2023-10-18 873

全部0条评论

快来发表一下你的评论吧 !