逻辑门电路的基础知识

应用电子电路

描述

一、基本逻辑门电路

1、关于逻辑电路的几个规定

①有关高电平,低电平的规定;

在逻辑电路中,电位的高低常用高电平,低电平来描述,单位也用“V”表示。 实际的高电平和低电平都不是一个固定的数值,因此通常规定一个电平变化范围,如果在此范围内,就判断为1(或0)状态。 例如一个供电电源为+5V的电路,高电平可在35V之间波动,低电平可在00.4之间拨动。 实际使用中,各集成逻辑门电路都规定了高电平的下限值和低电平的上限值。

②正逻辑与负逻辑

1表示高电平,0表示低电平,称为正逻辑体系; 1表示低电平,0表示高电平,称为负逻辑体系,一般使用正逻辑体系。

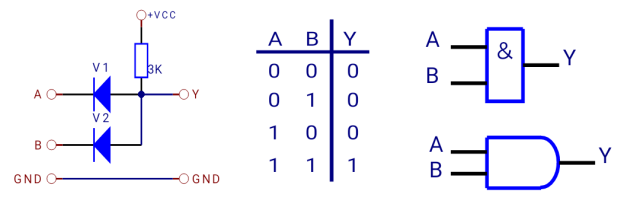

2、与门电路

①电路: ②真值表: ③逻辑符号:

④逻辑表达式:Y=A*B

⑤逻辑功能:有0出0,全1出1

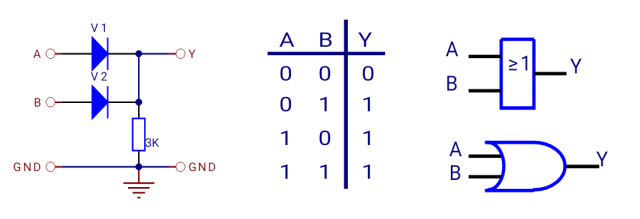

3、或门电路

①电路: ②真值表: ③逻辑符号:

④逻辑表达式:Y=A+B

⑤逻辑功能:有1出1,全0出0

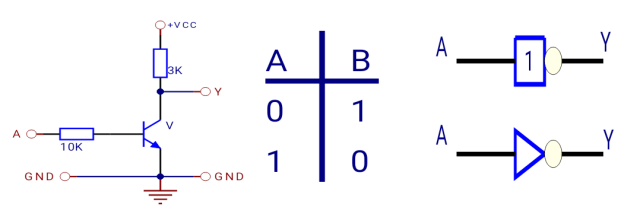

4、非门电路

①电路: ②真值表: ③逻辑符号:

④逻辑表达式:

⑤逻辑功能:有0出1,有1出0

二、组合逻辑门电路

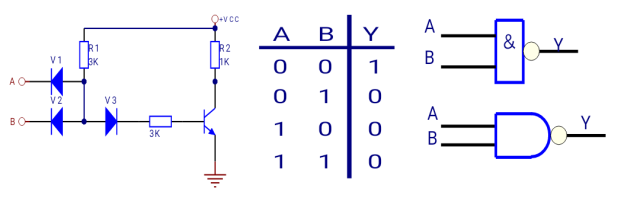

1、与非门

①电路: ②真值表: ③逻辑符号:

④逻辑表达式:Y=(A*B)

⑤逻辑功能:有0出1,全1出0

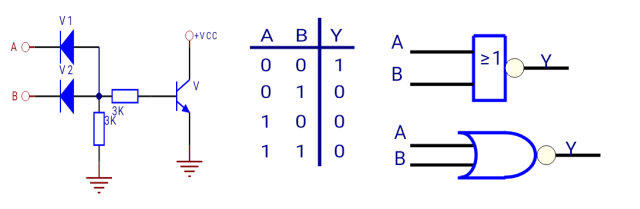

2、或非门

①电路: ②真值表: ③逻辑符号:

④逻辑表达式:(AB+CD)

⑤逻辑功能:有1出0,全0出1

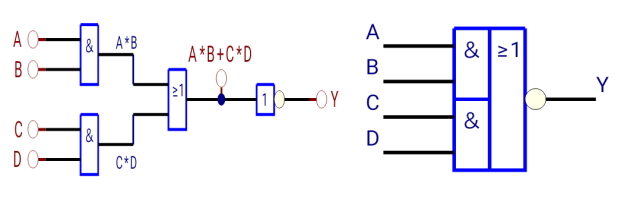

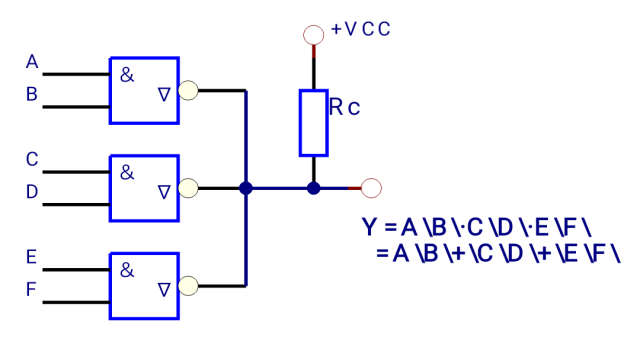

3、与或非门

①电路: ②逻辑符号:

③逻辑表达式:Y=(AB+CD)

④逻辑功能:输入AB或CD一组全为1时,输出为0,

输入AB和CD各组至少有一个为0时,输出才能为1。

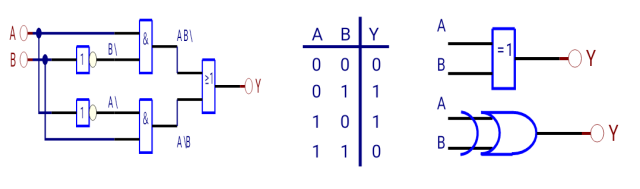

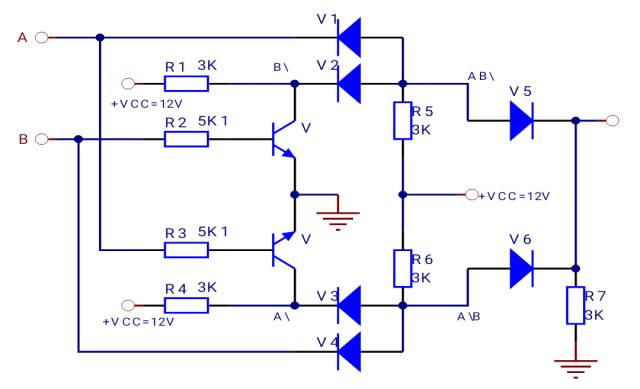

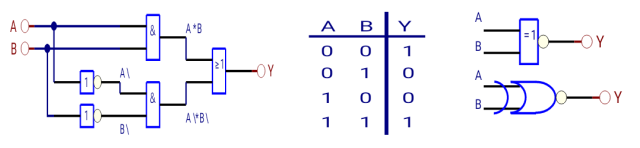

4、异或门

①电路: ②真值表: ③逻辑符号:

④逻辑表达式:Y=A*B+A*B=A⊕B

⑤逻辑功能:输入不同出1,输入相同出0。

⑥分立元件的电路设计

5、同或门

①电路: ②真值表: ③逻辑符号:

④逻辑表达式:Y=A*B+A*B=A⊙B

⑤逻辑功能:输入相同出1,输入不同出0

⑥分立元件的电路设计(仿异或门自行设计,并画出电路图)

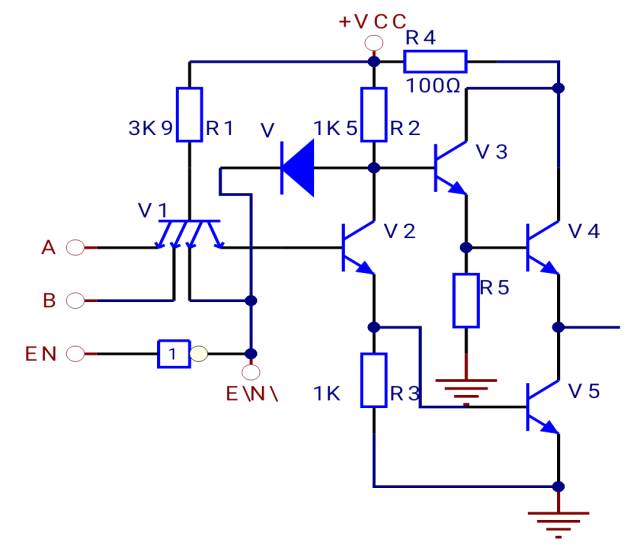

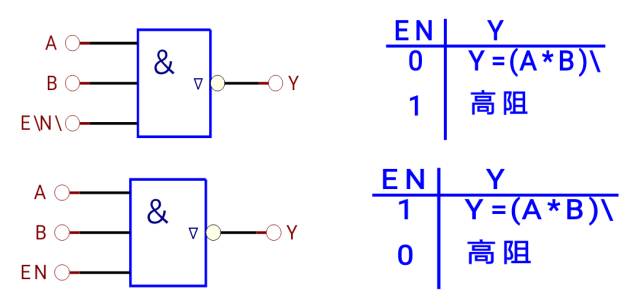

6、三态门(输出端状态:高电平,低电平和高阻)

三态门输出“与非”门又称为三态电路,三态门。 它与TTL“与非门”的不同之处是:它的输出端除可以具有高电平和低电平两种输出状态外,还能出现第三种输出状态——高阻输出状态。

如图所示为一个三态门电路,

当EN=0,经反相器后,EN=1,此时二极管V反偏,此时的状态由AB本身决定(Y=A*B的工作原理可自行分析)。

当EN=1时,经反相器后,EN=0,此时二极管V正向偏置,使三极管的V3基极降至低电平,导致V3、V4、V5都截止,输出端Y呈现高阻状态。

上述这种只用当控制端为低电平时,电路才能处于工作状态,称为低有效三态门,若在上图中的EN端再加一级非门,当控制端EN为高电平时,电路处于工作状态,称为高有效三态门。

三态门常用于实现同一根线轮流传送几个不同的信号或数据,即构成总线传送。

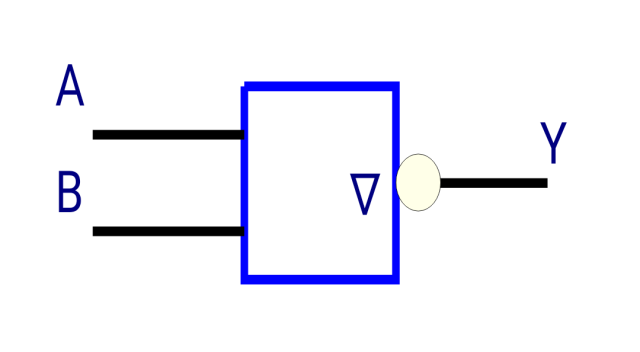

7、OC门(集电极开路与非门)

在电子计算机中广泛使用“母线”结构,即与非门输出

并联使用,实践证明普通与与非门是不允许的,为了满足这一要求,制造厂生产出一种输出晶体管的集电极开路的与非门电路,简称OC门电路,该电路使用时要外接负载电阻,其逻辑功能同一般的与非门,符号见右图。

当所有OC门的输入端均为1时,则Y=0,当某个OC门的输入全为1时,而其他OC门输入均有低电平时,由于其中一个OC门输入均为1,则相应OC门输出导通,而其它OC门的输出截止。 所以输出为低电平。 只有当各OC门输入端均有低电平时,输出端Y才为高电平。

三、逻辑门电路使用的几个实际问题

1、组合逻辑门电路功能特点;

在组合逻辑门电路中,任何时刻的输出状态直接由当时的输入状态决定,输入状态小时,则相应的输出状态立即随之小时,电路没有记忆能力。

2、数字集成电路按照内部组成器件的种类可分为两大类:

一类是普通三极管型数字集成电路,简称TTL电路; 另一类是场效应管型数字集成电路,简称CMOS电路。

3、数字集成电路的使用规则;

①TTL数字集成电路使用规则:

电源供电+VCC:只允许在+5V±10%范围内,超过范围会使逻辑功能混乱或损坏器件。

电源滤波:TTL为高速器件,在状态切换时会在公共走线上产生压降引起噪声干扰,可在电源端并联一个100UF的电容作为高频滤波。

输出端的连接:不允许输出端直接接地或接+5V,除OC门和三态门,其他门电路不允许并联使用,否则会英气逻辑混乱或损坏器件。

输入端的连接:输入端可以串接1只1~10K电阻与电源或直接与电源相连获得高电平输入。 直接接地为低电平输入。 TTL门电路多余输入端不能悬空,对于或门、或非门只能接地,对于与门、与非门只能接高电平或与其他输入端并联使用,增加电路可靠性。

②CMOS数字集成电路使用规则

电源电压+VDD:CMOS集成电路的电源电压+VD范围较宽,一般在+5V~+15V范围内均可正常工作,并允许波动±10%,同时要求+VDD接电源正极,VSS接电源负极(接地)。

输入端的连接:输入端信号VI应为VSS≤VI≤VDD,超出范围会损坏器件,多余的输入端不允许悬空,应按照逻辑要求接+VDD或VSS,工作速度不高时允许输入端并联使用。

其他:测试CMOS电路时,应先加+VDD,后加输入信号,关机时应先切断输入信号后断开电源+VDD,所有仪器外壳应良好接地。

-

基本逻辑门电路原理2009-04-06 0

-

逻辑门电路电子教案2009-09-16 0

-

逻辑代数基础及基本逻辑门电路2009-07-02 979

-

逻辑门电路 第2章2010-05-12 446

-

第六讲 逻辑门电路2009-03-30 3454

-

基本逻辑门电路2009-04-06 18415

-

TTL逻辑门电路2009-04-07 17274

-

逻辑门电路符号图2009-04-07 10645

-

或逻辑及或门电路2009-09-24 4336

-

非逻辑及非门电路2009-09-24 4635

-

逻辑门电路2016-09-02 1095

-

逻辑门电路讲义2017-02-07 943

-

逻辑门电路相关概念2023-04-26 1259

-

逻辑门电路有关概念2023-09-15 990

-

逻辑门电路基本概念介绍2023-10-10 1686

全部0条评论

快来发表一下你的评论吧 !