双倍数据速率(DDR)内存简介

存储技术

描述

了解围绕这种数字通信技术的双倍数据速率 (DDR) 内存关键概念和应用,该技术在一个时钟周期内传输两个数据字。

与并行数据传输相比,串行数据传输具有重要优势,在许多系统中,这些优势足以证明添加电路是合理的: 序列化和反序列化 并行数据,以便可以作为串行数据传输。然而,计算机内存是并行数据传输仍然普遍存在的一个应用领域。因为他们可以读写很多 数字信号 同时,并行接口速度很快,设计人员一直在寻找使其更快的方法。

实现数据传输速率大幅提高的一种古老但仍然相关的技术称为双泵浦,此功能将内存系统转变为双倍数据速率 (DDR) 内存系统。“单泵浦”存储器系统采用历史悠久的策略,将数据从一个IC同步移动到另一个IC。基本上,逻辑信号每个时钟周期变化一次,并由接收器在时钟的上升沿或下降沿进行采样。在此方案中,单词传输的速率不能超过时钟频率。

例如,如果您的时钟以 133 MHz 运行,则(理想情况下)每秒可以传输 1.33 亿字。请注意,位传输速率取决于系统架构,因为不同的计算系统使用不同的字长——8 位、16 位等。双泵浦系统可以在 133 MHz 时钟下实现 266 MT/s(每秒数百万次传输)。

在本文中,我们将了解单数据速率接口和双数据速率接口之间的差异、使用 DDR 的原因及其应用。

SDR 与 DDR:单数据速率和双数据速率接口

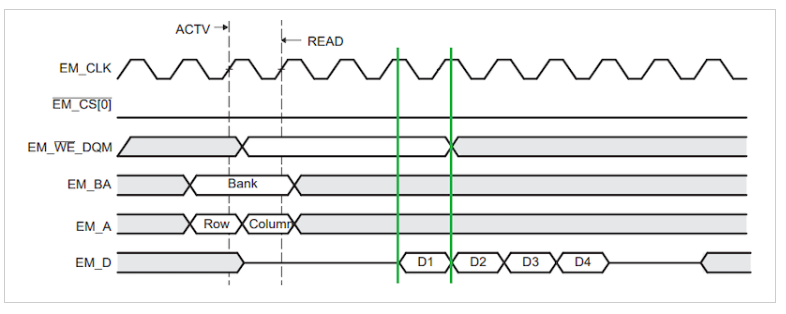

图1所示的时序图是单个数据速率存储器接口的示例。

图1. 单个数据速率存储器接口的示例。图片 [修改] 使用由 德州仪器

首先,使用EM_BA信号选择存储库,并通过EM_A信号建立行和列地址。数据字D1、D2、D3和D4输出在EM_D引脚上。请注意一个数据字如何占据EM_CLK信号的整个周期。

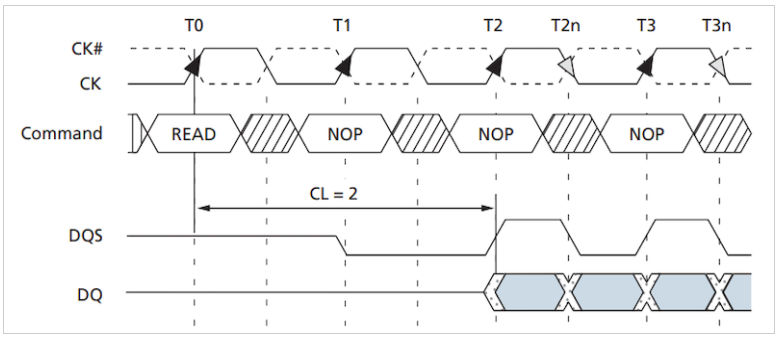

下一个时序图(图2)将介绍双倍数据速率接口。

图2. 双倍数据速率接口的示例。图片由 微米

“DQ”线表示数据信号,阴影区域之间的无阴影X形区域表示从一个单词到下一个单词的过渡。您可以看到每个单词只需要一个完整时钟周期的一半。请记住,此芯片使用 微分 时钟,这就是为什么时序图有一个 CK 信号和一个互补的 CK# 信号。

动机:为什么要将数据速率提高一倍?

您可能想知道为什么工程师在为 DDR 信令创建新逻辑时会遇到麻烦,而他们本可以增加 时钟频率 两倍。对这一决定的主要解释包含在代表无数小时高速研发的两个词中:信号完整性。

高频信号(相对于给定技术时代或应用场景的限制来理解“高频”)是电路板设计人员非常震惊的根源。这些信号:

由于信道带宽有限而导致的更多色散

需要更多功耗

更容易患 电容耦合 和 反射,

更有效地从任何PCB上存在的各种无意天线进行辐射

使用测试设备进行表征和故障排除也更加困难。例如,示波器的模拟和数字带宽有限,随着频率的增加,它会在波形中引入更多的失真。

因此,在尝试实现更高的时钟速率之前,从现有时钟速率中提取尽可能多的吞吐量是有意义的。通过从单个数据速率接口迁移到DDR接口,设计人员可以在不改变系统最大信号频率的情况下显著提高数据传输速率。即使数据信号的最大频率增加了两倍,所有这些都可以完成,这个新的数据频率并不高于以前的时钟频率。

DDR 内存应用

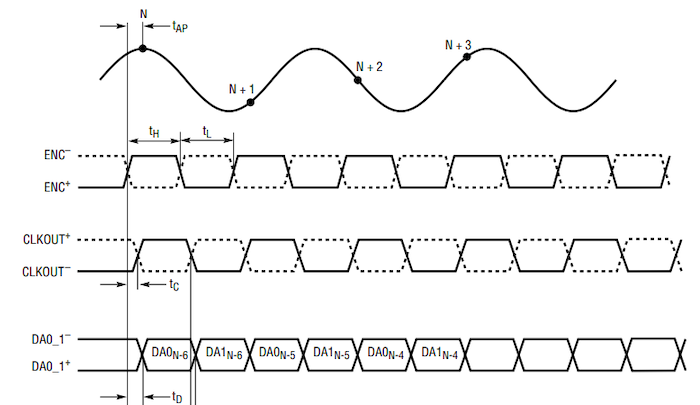

双泵浦是已在各种并行数据传输接口中使用的通用功能。甚至高速数据转换器也采用了这种技术。在 模数转换器 (ADC) 例如,图3所示的时序图,一个样本在一个完整时钟周期所需的时间内数字化,但数字输出使用DDR时序,因为每个输出上多路复用了两个数据位。

图3. 示例ADC时序图,其中显示的所有信号均为差分信号。图片由 模拟/线性技术

但是,DDR并行传输仍然与SDRAM(同步 动态随机存取存储器) 用于计算系统。几十年来,工程师们一直在努力提高计算机移动和处理数字数据的速度,DDR信号使他们能够将吞吐量翻倍,同时保持当时可行的最大时钟频率。

1998年发布的第一代DDR SDRAM支持高达200 MHz的时钟频率和高达400 MT/s的相应传输速率。然后是DDR2,DDR3,DDR4,最后是我们目前使用的DDR5。DDR5 的最大传输速率超过 7 GT/s。

在 DDR 内存中奠定基础

DDR计算机内存的开发是一个相对漫长的过程,这证明了我们在本介绍性文章中没有研究的许多复杂性和设计挑战。尽管如此,我希望您现在了解DDR数字通信的基本前提。

-

了解单数据速率接口和双数据速率接口之间的差异2023-02-23 0

-

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR52023-08-09 15372

-

保持输入双倍数据速率的时间错误的解决办法?2020-05-01 0

-

Arm®CoreLink™ DMC-620动态内存控制器技术参考手册2023-08-02 0

-

JEDEC即将完成DDR4内存标准关键属性2011-08-24 1734

-

电源设计小贴士:DDR内存电源2011-12-16 3652

-

DDR存储器电源的内存解决方案2019-03-25 4151

-

DDR SDRAM是拥有着双倍数据传输率的SDRAM2020-07-16 1994

-

如何去解决LVDS差分接口的DDR信号问题2022-08-20 1978

-

介绍一款灌电流和拉电流双倍数据速率 (DDR) 终端稳压器2022-09-30 735

-

双倍数据率 (DDR) 内存简介2023-04-06 681

-

DDR信号的处理2023-06-16 903

-

DDR内存终端电源2023-06-26 644

-

简单认识双倍速率同步动态随机存取存储器2023-11-20 495

-

GDDR和DDR代表什么?GDDR和DDR内存有什么区别?2024-03-17 648

全部0条评论

快来发表一下你的评论吧 !