基于EV10AQ190的高速ADC接口设计

描述

回顾:

今天看了这篇论文,感觉还挺有吸引力,就做了如下的笔记:

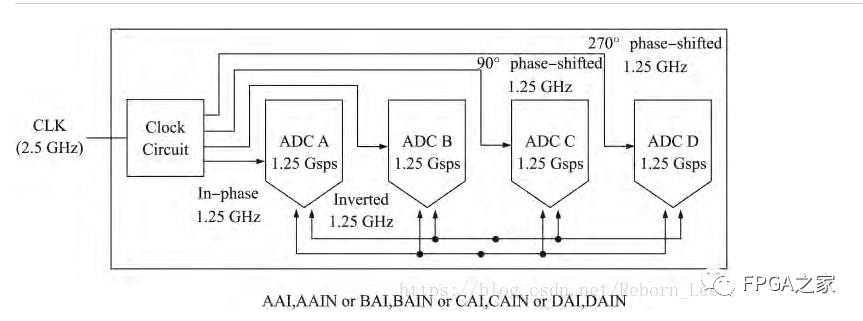

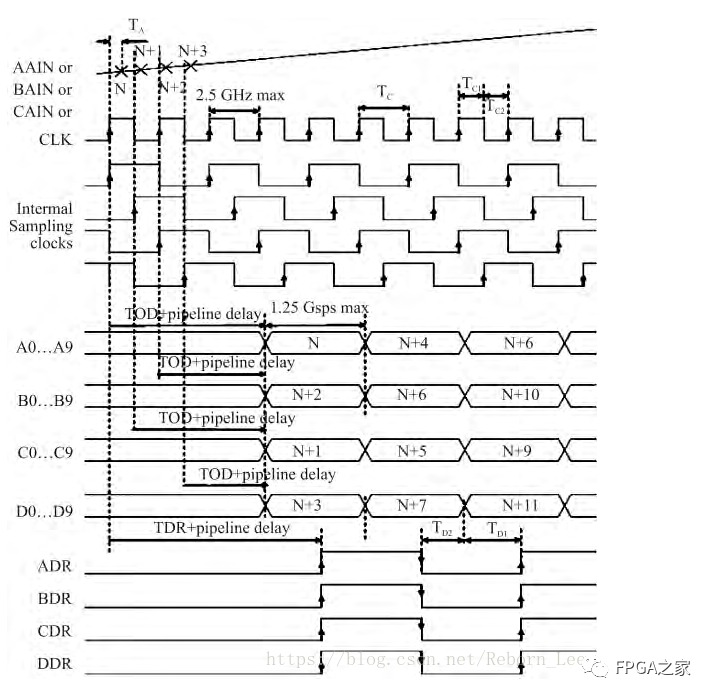

如下图,首先以单通道工作方式为例,回顾一下这款ADC芯片的工作模式:

外部给该ADC芯片提供一个时钟CLK,频率为2.5GHz,通过内部时钟电路,2分频之后的时钟送到核A(ADC A),相位翻转180°的二分频时钟送到核B(ADC B),相位偏移90°的二分频时钟送到核C(ADC C),相位偏移270°的二分频时钟送到核D(ADC D)。四个ADC核(A、B、C、D)同时工作(同时采样),工作频率相当于5GHz。

也可以根据论文上的描述:

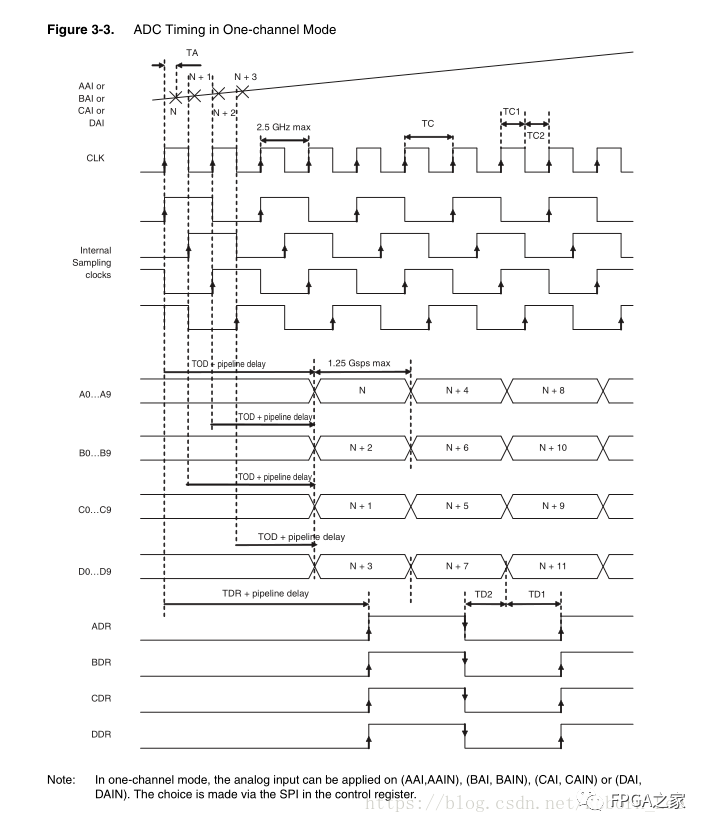

从上面的分析大概也能明白了采样时钟的波形是什么样子的:

描述一下采样顺序就是ADC A采样的数据为第1个,然后ADC C 采样的数据为第2个, ADC B采样的数据为第3个, ADC D采样的数据为第4个,依次循环。

正如数据手册的描述:

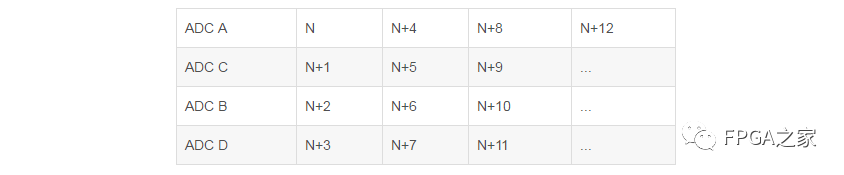

为了简化定时器的目的,关于采样的端口的时间顺序是A C B D,因此输出端口的采样顺序如下:

A: N, N + 4, N + 8, N + 12…

C: N + 1, N + 5, N + 9…

B: N + 2, N + 6, N + 10…

D: N + 3, N + 7, N + 11…

画个表格更直观些:

回顾就到这里吧。

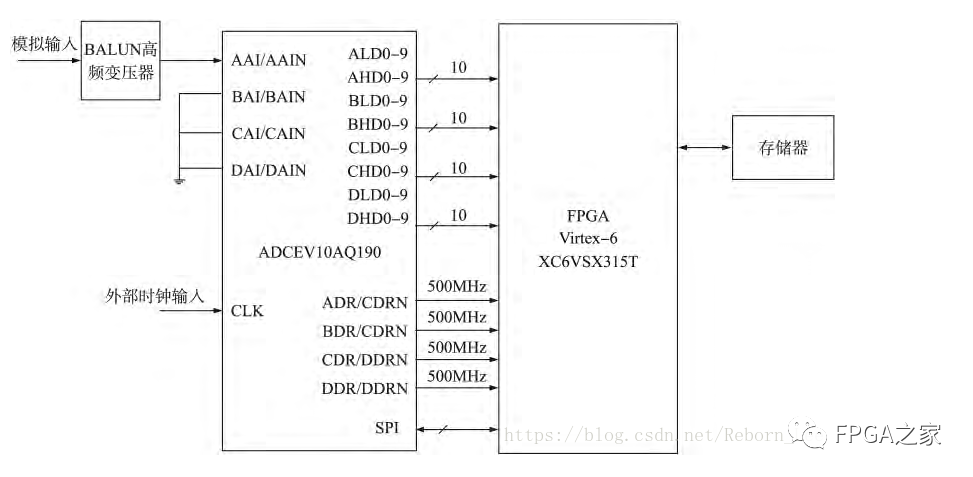

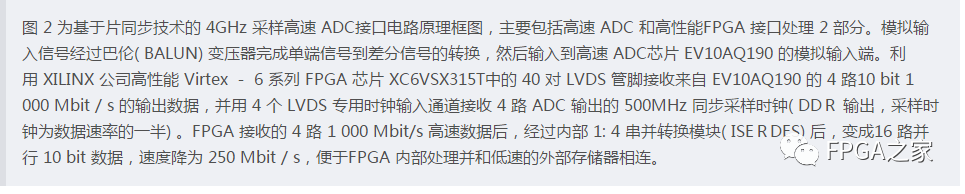

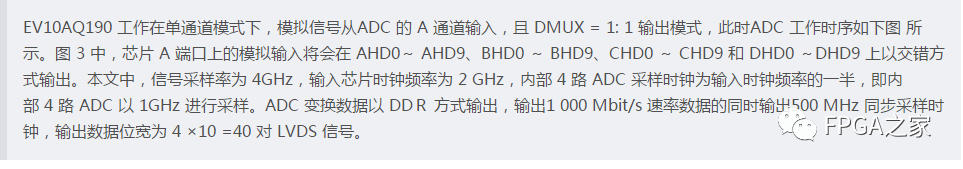

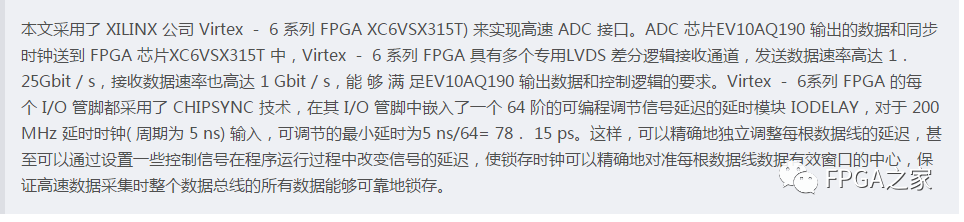

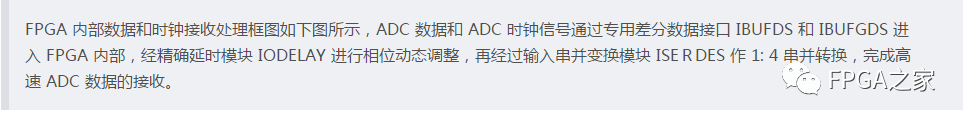

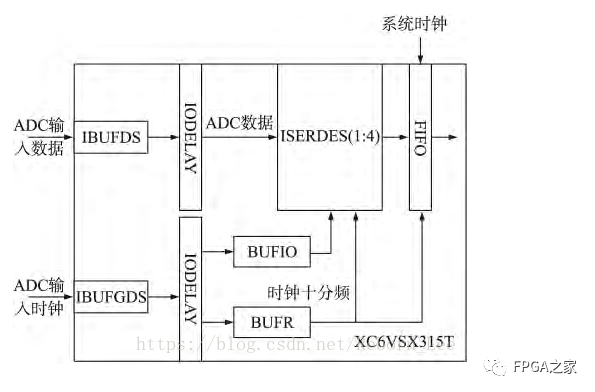

基于片同步技术的高速 ADC 接口

片同步( CHIPSYNC) 是 XILINX 公司命名的一种同步技术,其本质是一种源同步技术,目的是为FPGA 提供一个高速的源同步数据总线接口。它是XILINX 公司在 Virtex - 4 及之后系列 FPGA 上采用的一种技术,XILINX FPGA 内部具有若干全局时钟缓冲器( BUFG) 和区域时钟缓冲器( BUFR) ,特别适合做源同步接口。FPGA 片内每个 I/O 管脚中集成了一个 64 阶的可编程调节信号延迟的延时模块( IODELAY) ,可精确控制信号延时实现采样时钟和数据相位的动态调整,从而确定信号采集的最佳采样点,实现高速 ADC 接口的可靠、稳定工作。

上面说的4GHz的意思是ADC等效的采样速率,这也就意味着外部输入时钟的频率为2GHz,如此数据同步时钟是外部时钟的1/4,也就是500MHz。等效采样速率为4GHz,那么每一个通道的采样速率就是1GHz,也就是1000MHz,那么EV10AQ190的每一路输出数据速率为1000Mbit/s,且由于该ADC芯片的采样分辨率为10bit,也就是每个采样点数据为10bit。

4路1000Mbit/s的输出数据经过FPGA的接收后,经过FPGA内部1:4串并转换后,每一路串行数据变成4路并行数据,那么4路数据串行数据变成16路并行数据,此时并行数据的速率为串行的1/4,也就是250Mbit/s,这样速率就降低了,便于FPGA内部处理并和低速的外部存储器相连。

高速ADC

ADC 与 FPGA 数据接口

至于接下来的仿真等,我还实现不了。就记到这里吧,以后积累了经验在回头看。

审核编辑:汤梓红

-

哪位大神用过 EV10AQ190 高速ad 求指导2015-11-18 0

-

EV10AQ190AVTPY 模拟多路复用器现货2018-11-14 0

-

EV12DS4602019-03-12 0

-

请问一下EV12AQ605有哪些特点?2021-07-09 0

-

EV8AQ160型ADC在2.5 Gsps双通道高速信号采集系统中的应用2011-11-03 1588

-

FPGA与高速ADC和DAC的配合使用方法2017-10-18 1432

-

关于高速ADC和DAC与FPGA的配合使用浅析2018-10-31 10858

-

一种高速ADC接口电路设计方案2019-04-12 12487

-

EV12AQ605,EV12AQ600面向竞争激烈的大用量应用的优化版本2019-11-11 1882

-

基于EV12AQ600设计的四通道模数转换器EV12AQ605介绍2019-11-21 3831

-

高速adc四路光纤2020-04-24 3581

-

EV12AQ600/EV12AQ605数模转换器介绍2021-08-27 848

-

解读ADC采样芯片(EV10AQ190A)的采样(工作)模式(双通道模式)2023-02-22 2881

-

解析高速ADC和DAC与FPGA的配合使用2023-07-13 3317

全部0条评论

快来发表一下你的评论吧 !