一文详解锁相环位同步

描述

1 运行平台

硬件:CRD500数字信号处理板

系统:win7/64;win7/32;win10/64

软件:Quartus/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

3.2.1主要功能

1)产生基带原始数据

2)位同步信号提取

3.2.2主要性能指标

1) 发送端

系统时钟:50MHz

基带数据码率:1.5625Mbps

数据内容:“11111010”循环码

2) 接收端

系统时钟:50MHz

同步方式:超前-滞后型锁相环位同步

同步精度:1/8 码元宽度

3 程序结构框图说明

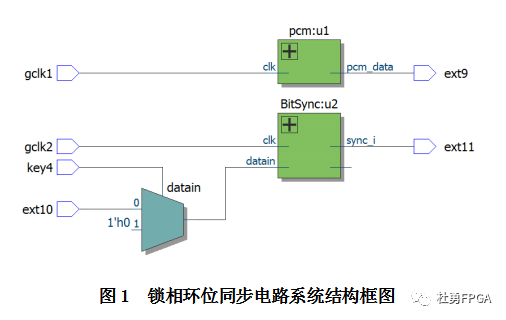

锁相环位同步电路系统主要由基带数据生成模块(pcm.v)、位同步模块(BitSync.v)组成。

基带数据生成模块生成的原始数据(1.5625Mbps)送至开发板上扩展口的第9脚,经短接线由第10脚送回FPGA芯片;位同步模块从接收到的原始数据中采用锁相环法提取位同步信号,提取出的位同步信号由扩展口的第11脚输出。为真实的验证位同步通信功能,发送端(pcm.v)的时钟由CRD500开发板上的X1晶振驱动,接收端(BitSync.v)的时钟由X2晶振驱动。

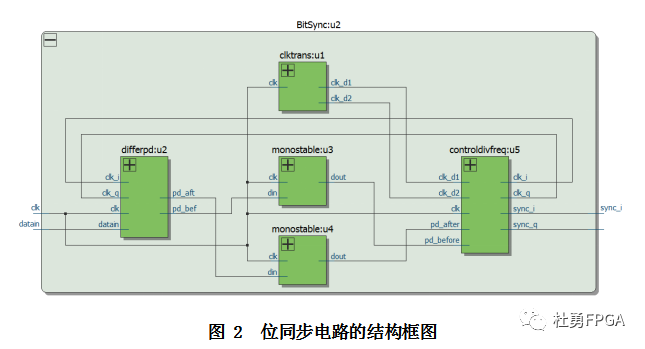

位同步电路的结构框图如图2所示。

实例采用超前-滞后型锁相环位同步电路实现位同步的提取功能,电路主要由鉴相模块(differpd.v)、双相时钟模块(clktrans.v)、单稳触发器模块(monostable.v)和控制分频模块(controldivfreq.v)组成。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

锁相环知识2011-12-21 0

-

数字锁相环设计步骤2012-01-12 0

-

锁相环2012-08-13 0

-

锁相环在电力系统中的应用2015-01-04 0

-

请问ADF4351能做数字锁相环实现位同步吗2018-09-14 0

-

AD9957锁相环一直失锁2018-12-10 0

-

AD9516的内部锁相环不能稳定锁相2019-02-19 0

-

分两部分介绍锁相环2019-06-21 0

-

PVA0865AF-LF锁相环2021-04-03 0

-

SFS11000Y-LF锁相环2021-04-03 0

-

求一种锁相环位同步提取电路的设计方案2021-04-29 0

-

MCU锁相环的相关资料分享2021-11-04 0

-

LabVIEW锁相环(PLL)2022-05-31 0

-

锁相环如何进行锁相呢?2023-04-24 0

-

模拟锁相环与数字锁相环的主要区别在哪里?2023-04-24 0

全部0条评论

快来发表一下你的评论吧 !