深度解读SerDes(Serializer-Deserializer)3

电子说

描述

3.抖动和信号集成( Jitter, SI )

抖动是指信号的跳边时刻偏离其理想(ideal)或者预定(expected)时刻的现象。噪声,非理想的信道,非理想的电路都是产生抖动的原因。

3.1 时钟的抖动(clock jitter)

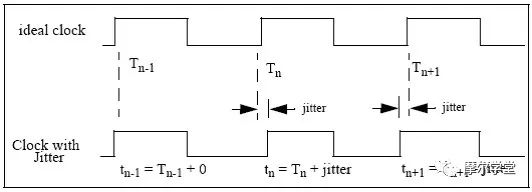

Figure 3.1 Clock Jitter

对于时钟信号,根据应用场景的不同,对抖动的定义也不一样。比如数字逻辑计算时序余量的时候,关心的是周期抖动。而时钟设计人员更喜欢相位抖动,因为可以利用频谱评估相位抖动,并可以用频谱来评估具体的干扰对总相位抖动的贡献。

参考图3.1,介绍一下几种抖动的定义。

l 相位抖动(phase jitter)

J phase (n)= tn – n*T。理想时钟的每个周期T都是相等的,没有抖动。真实时钟的跳边沿相对于理想时钟的偏离称作相位抖动。

l 周期抖动(period jitter)

J period (n)= (t n - t n-1 )– T。周期抖动是实际时钟的周期相对于理想周期的偏离(deviation)。显然J period (n) = J phase (n) - J phase (n-1)。

l Cycle-to-Cycle jitter

J cycle (n) = (t n - t n-1 ) - (t n-1 - t n-2 )。前后相邻的两个周期的偏差是Cycle-Cycle抖动。显然J cycle (n)= J period (n) – J period (n-1)。

假设相位抖动的最大值为 +/-Jp, 而且抖动的频率fjitter = 0.5fclock = 0.5/T,也就是,

tn-2时刻的相位抖动为最大值+Jp ,tn-1时刻的相位抖动为最小值-Jp

tn时刻的相位抖动为最大值+Jp , tn+1时刻的相位抖动为最小值-Jp

那么,周期抖动最大值 J period =+/- 2* Jp

那么,Cycle-Cycle抖动最大值 Jcycle ~ =+/- 4* Jp~

3.2. 数据的抖动(data jitter)

在高速SerDes领域每个人都在说抖动,因为抖动直接和误码率(BER)相关。

SerDes发送端的一个重要要求是抖动(jitter generation)----针对特定的码型(pattern),速率和负载情况下,发送端所生成的抖动。

信号经过信道(channel)到达接收端时,又会进一步放大抖动,不同的码型(pattern)包含的频率成分也不一样,信道对不同频率成分的传输延时也不一样(非线性相位), 产生和数据pattern相关的确定性抖动。阻抗不连续产生的反射,相邻信号的串扰和噪声都会引起数据抖动。

SerDes接收端的一个重要指标是抖动容忍能力(Jitter Tolerance)----针对特定的码型和误码率要求(BER<10 ^-12^ ),SerDes接收端能够容忍的抖动大小。对抖动评估时,会使用眼图(eye-diagram),浴缸曲线(bath curve),抖动分布柱状图(PDF),抖动频谱(jitter spectrum)等图形手段。

有一点需要说明,在谈论高速SerDes的数据抖动时(Tj,Rj,Dj etc.),是不包括低频率抖动的。这是因为低频率的抖动被认为是一种wander,可以被CDR跟踪,不会引起误码。在用示波器(SDA)测量数据抖动的时候,可以设置示波器内嵌的CDR环路带宽,示波器测量的抖动数据已经滤掉了低频抖动。

根据抖动产生的原因和概率密度函数,常常将抖动分为几类。对抖动进行分类的意义在于某些类型的抖动可以被校正,而其他类型的不能被校正。经典的,总抖动Tj(Total Jitter)被分类为确定性抖动Dj ( deterministic jitter )和随机抖动Rj ( random jitter )。抖动以UI或者ps为单位,可以是均方根值,或者峰峰值。

3.2.1 Dj

Dj被进一步细分,

l DCD( Duty cycle distortion )

占空比失真抖动。差分信号的正端负端的偏置电压不一致,或者上升沿和下降沿时间不一致会导致占空比失真。因为DCD和数据pattern相关,是可以被校正的抖动。

l DDJ( Data dependent jitter )

数据码型相关的抖动,也称 码间干扰ISI( intersymbol interference )。DDJ是由于不理想的信道导致。是可以被均衡器校正的抖动。

l Pj( Periodic jitter )

周期性抖动。Pj由电路上周期性干扰源导致。比如开关电源的开关频率,时钟信号的串扰等。虽然电源的开关频率一般在CDR的跟踪范围内,但是低次谐波成分可能会落在环路带宽外,或者jitter peaking区域, 更重要的是电源谐波对CDR内VCO的干扰是不能被抑制和跟踪的,所以对于基于Ring VCO的CDR一定要尽可能的使用LDO供电。Pj不能被均衡器校正.

l BUJ( Bounded uncorrelated jitter )

BUJ由非时钟的干扰源引起。如果干扰源aggressor和victim是异步的,抖动的概率分布为有界的高斯分布,此时也称作CBGJ( Correlated Bounded Gaussian Jitter )。BUJ/CBGJ不能被校正。

3.2.2 Rj

Rj有半导体本身的噪声引起,一个重要特征就是Rj的概率密度函数是高斯分布的,没有边界,且和数据pattern无关。只有在一定误码率约束下,才可以被认为是有界的。

3.2.3 Tj

数学意义上,抖动的概率分布函数可以近视为高斯分布和双底拉克分布的卷积。

对高斯分布有贡献的抖动为:

n Rj为高斯分布

n 大量Pj叠加的效果也为高斯分布

n 部分BUJ也为高斯分布

对双底拉克分布有贡献的抖动为:

n DCD被近视为双底拉克概率分布

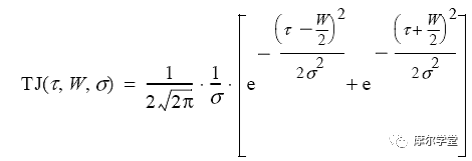

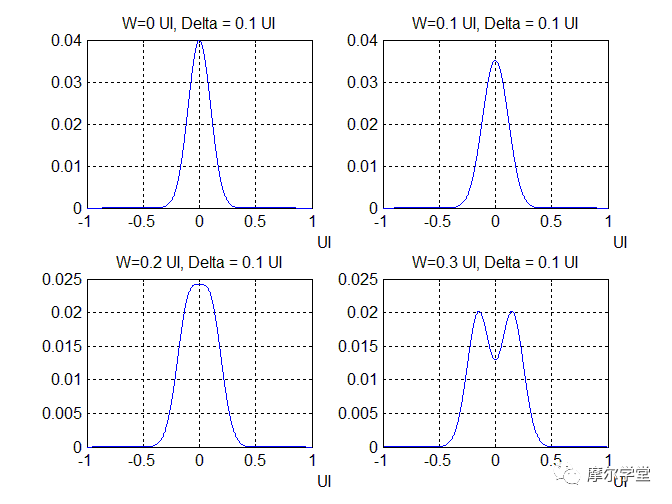

高斯分布和双底拉克分布的卷积:

其中,W被认为是确定性抖动的峰峰值,δ是高斯分布的均方差。见图3.2, 可以看到,随着确定性抖动W的增加,概率密度分布曲线的顶部出现了双峰。一般来讲顶部曲线反映了确定性抖动的大小程度。

Figure 3.2 PDF of Tj with different Dj and Rj

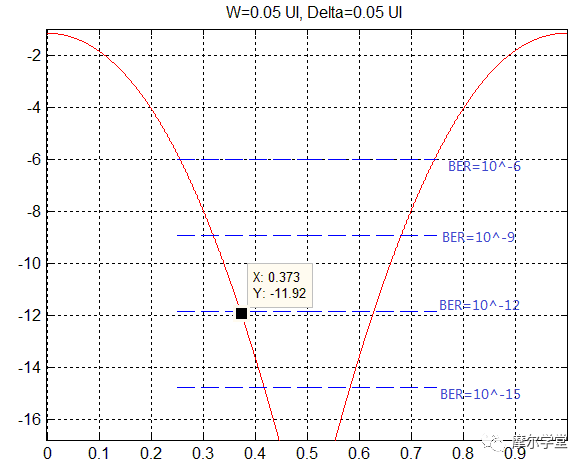

把一个UI内的两个跳变沿处(0 UI处和1UI处)的概率分布函数放在一张图中,就是抖动的浴缸曲线( bathtub curve )。因为对数的宽动态范围,Y坐标以对数显示。图3.3为确定性抖动W=0.05UI, 高斯抖动方差0.05UI的浴缸曲线。

Figure 3.3 Bathtub Curve of Tj with 0.05 Dj peak and 0.05 Rj RMS

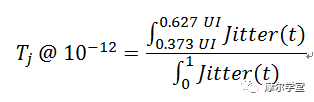

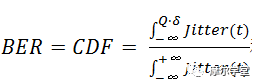

浴缸曲线还会标出对应的误码率BER坐标,比如图中BER=10^-12的峰峰值抖动为Tj(p-p)=0.373*2 = 0.746 UI。曲线下面的面积占总面积的比率就是误码率。比如图中,

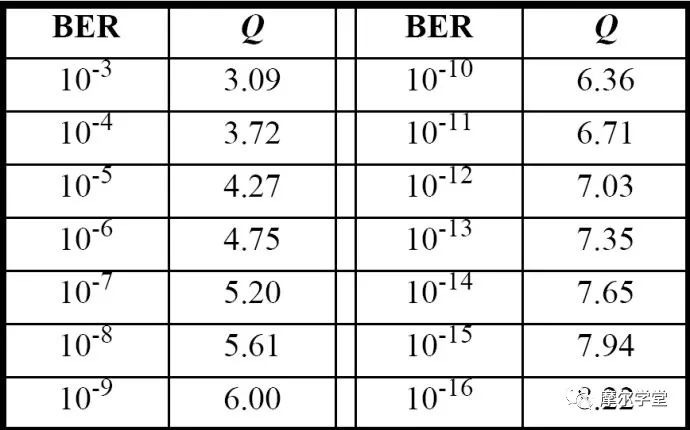

浴缸曲线的顶部主要为确定性抖动Dj的贡献,越靠近底部,高斯抖动的贡献越大,并以高斯曲线的斜率衰减,也因此常利用高斯分布的特性进行估算。下表为高斯分布

和均方差关系。

在规定的BER内,利用该表可以快速估算均方差值和峰峰值之间的关系。比如高斯抖动的均方根0.05UI,误码率要求为10^-12 BER,查表可知Q=7,那么高斯抖动的峰峰值要求是0.05UI72 = 0.7UI。

如前所述,W=0.05UI,Rj=0.05UI计算出的总抖动Tj=0.746UI;

利用高斯特性估算的高斯抖动为0.7UI。

如果按Tj = Rj(0.7UI)+Dj(0.05UI)计算得到0.75U,基本是一致的,差异是因为画图程序有量化误差。

4.信号集成(SI)及仿真

4.1信道channel

SerDes信道关注的频率范围是0Hz到奈奎斯特频率,也就是2倍的信号基频。信号的基频是信号线速率的一半,也就是说信号的奈奎斯特频率就是线速率。信道对信号的损伤包括插入损失(insertion loss),反射 (reflection),串扰(crosstalk)等。这些损伤可以用S-parameter信道模型来表达。S-parameter可以有矢量网络分析仪测量(Vector Network Analyzer)得到。信道不是一个纯阻性网络,还包括容性和感性。这样对不同频率里成分的时延也不一样,从而产生和data pattern相关的抖动。

信道上的每一个不连续阻抗点都会产生反射,根据反位置的不同,反射信号会以不同的相位叠加在原始信号上,增加或者减小信号的幅度。

SerDes信号为差分形式,对共模干扰有较强的抑制。如果在+/-端上的干扰有差异,就会引入串扰。通常外部PCB可以保证SerDes数据和干扰源保持足够的距离,但是芯片内部由于考虑到经济性,很难保证SerDes信号和干扰源足够的隔离距离,尤其是一个通道自己的发送信号干扰自己的接收信号。

4.2 芯片封装Package

封装package也是信道的一部分。芯片外部的信道可以通过VNA测量的到,而封装的S-parameter通常有芯片制造商提供,仿真时可以把两者级联起来。封装package由于距离较短,insertion loss通常不是主要问题,主要考虑的是阻抗匹配问题。

4.3 SI仿真

信号集成性(SI)仿真可以通过把SerDes发送端SPICE模型,封装和信道的S-parameter模型,接收端SPICE模型级联起来搭建仿真平台,利用仿真工具对不同的激励在不同的测试条件作电路仿真。通过测量SerDes接收端的眼图来评估是否满足设计需求。也可以通过实测接收端眼图,检验是否满足接收端的眼图模板,或者协议规定的眼图模板。图4.1为一个实测的3.125Gbps信号的眼图及模板,同时也包含了浴缸曲线和统计图。

Figure 4.1 Rx-end Eye-diagram of A 3.125Gbps SerDes

对于高速SerDes(>5Gbps),这种传统的电路仿真方法已经不能满足设计的需求。首先,过量的码间干扰ISI导致接收端眼图完全闭合,但是通过芯片内的DFE均衡后,眼图可能是很好的。其次,电路仿真(SPICE)的速度非常慢,即使是有办法把DFE均衡加入仿真,由于DFE仿真需要足够长时间的bits来训练,此时,电路仿真的仿真时间是不可接受的。

对于高速SerDes的仿真需要借助统计分析 (statistical analysis) 的方法。统计分析的方法把发送端-信道-接收端的连接近视为线性系统,计算系统脉冲响应h(t),加入噪声源来模拟抖动,然后用激励对脉冲响应进行卷积,得到接收端的信号,这种方法可以把厂家私有的FFE,DFE自适应算法加入仿真。

统计分析 (statistical analysis)方法不能仿真电路的非线性和时变特性,所以高速SerDes往往要两者结合起来仿真SI。更多关于统计分析 (statistical analysis)方法可以参考。

-

Evaluate Serializer-Deserializ2008-07-25 831

-

利用眼图模板评估串行器和解串器(SerDes)的性能2008-11-26 2092

-

SerDes是怎么工作的2021-07-28 0

-

符合EMIEMC标准的SerDes—基本测试策略和指南2011-04-01 666

-

An Introduction to Preemphasis and Equalization in Maxim GMSL SerDes Devices2011-11-27 1949

-

SerDes的基本结构2022-10-31 1449

-

深度解读SerDes(Serializer-Deserializer)12023-03-16 2100

-

深度解读SerDes(Serializer-Deserializer)22023-03-16 1724

-

SerDes是怎么设计的?(一)2023-10-16 741

-

什么是SerDes呢?为什么我们需要此项技术呢?有哪些设计要求和技巧?2023-11-07 619

-

SerDes的技术原理 SerDes的重要概念和技术概述2023-11-14 6985

-

SERDES的作用 SerDes基础知识详解2024-01-04 1322

-

汽车以太网发明人押宝SerDes!一文详解车载SerDes技术2024-03-12 830

全部0条评论

快来发表一下你的评论吧 !