ADG1211开关实现采样保持电路

描述

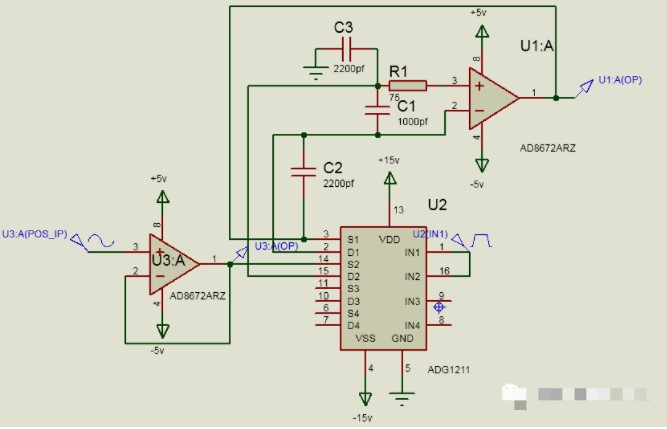

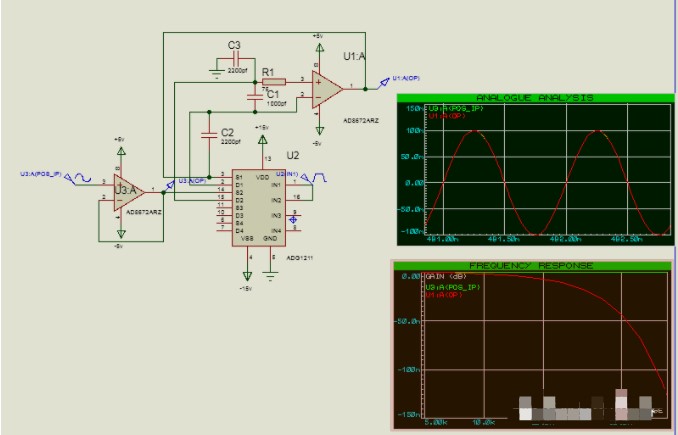

电路原理图

在可编程逻辑控制器(PLC)输出模块中存在每通道采样保持架构,它采用开关电容和缓冲器作为采样保持放大器(SHA),以便存储单通道高性能DAC的选定输出样本。这些样本通过-一个模拟开关或多路复用器在不同保持电容之间切换。

开关和多路复用器在必须获取瞬时模拟值的数据采集应用中很有用。模拟开关的输人信号向-一个与运算放大器输人相连的保持电容充电。理想情况下,闭合开关仅向电容传送输人信号。但在实际应用中,该开关也会传送-一个电荷包,称为电荷注人。ADG1211具有业界领先的1pC电荷注人性能,而市场上现有解决方案的电荷注人性能为10pC至20pC。ADG1211还具有出色的电容与泄漏性能,因而它是此电路的理想选择。

电路功能

该电路是-个精密、快速的采样保持电路。在采样模式下,SW2闭合,输出Vour跟随输人信号Vn。在保持模式下,SW2断开,信号由保持电容CH保持。由于开关和电容泄漏影响,保持电容上的电压会随着时间而下降。ADG1211具有低泄漏特性,能使这种电压下降最小。在25°C时,ADG1211的典型泄漏电流为20pA,最大泄漏电流为100pA。采用聚苯乙烯保持电容还可进--步使下降率更低。此电路还有另-一个开关SW1,它与SW2并联工作,用来降低基底误差。由于两个开关处于相同电位,因此对运算放大器的输出均具有差分效应,从而使电荷注入影响最小。补偿网络Rc和Cc也可降低基底误差。该补偿网络还可减小保持时间尖峰,同时优化采集时间。利用上述电路可得到如下结果:下降率为2 mV/ms,基底误差低于0.5 mV ,采集时间为3ms。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

转:采样保持电路2011-07-28 0

-

【每天看电路第77期】采样保持电路2019-01-04 0

-

怎么实现高速采样保持电路的设计?2021-10-11 0

-

ADG1211/ADG1212/ADG1213,pdf da2009-10-27 869

-

一种新型高速采样保持电路2010-05-24 821

-

采样保持电路原理(S/H)2009-04-12 23076

-

单片采样保持电路2010-05-23 3022

-

ADG1211_ADG1212_ADG1213 datasheet2016-10-12 718

-

低电容低电荷注入的CMOS四路SPST开关ADG1211/ADG1212/ADG1213数据表2017-10-20 781

-

采样保持电路图(五款采样保持电路设计原理图详解)2018-02-23 96642

-

ADG1211 低电容、低电荷注入、±15 V/+12 V iCMOS、四通道单刀单掷开关2019-02-22 3055

-

ADG1211 SPICE宏模型2021-04-12 406

-

ADG1211/ADG1212/ADG1213:低电容、低电荷注入、±15 V/+12 V<em>I</em>CMOS;四路SPST开关数据表2021-04-14 567

-

采样保持电路设计及其工作原理2022-10-20 5364

全部0条评论

快来发表一下你的评论吧 !