加法器的应用举例

描述

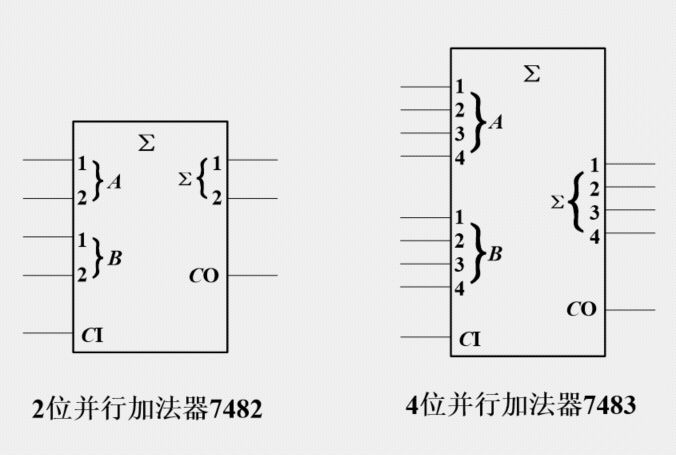

通用加法器集成电路

加法器应用举例

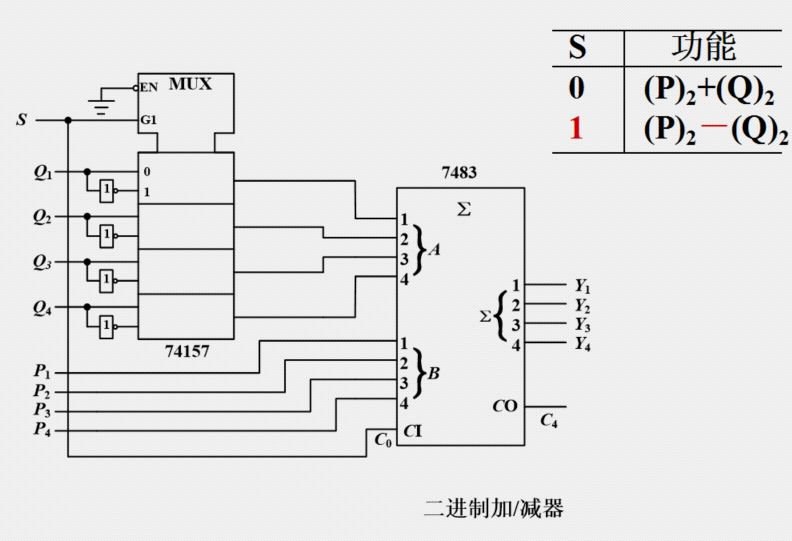

用4×2选1数据选择器74157和4位全加器7483,构成4位二进制加/减器。

在二进制补码系统中,减法功能由加“减数”的补码实现。

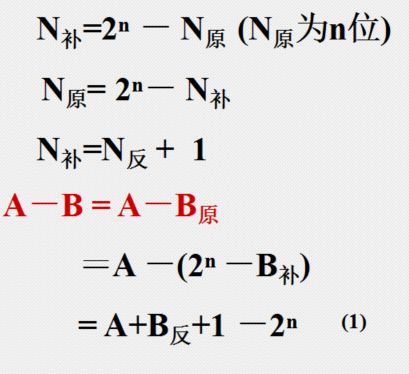

关于减法电路探讨

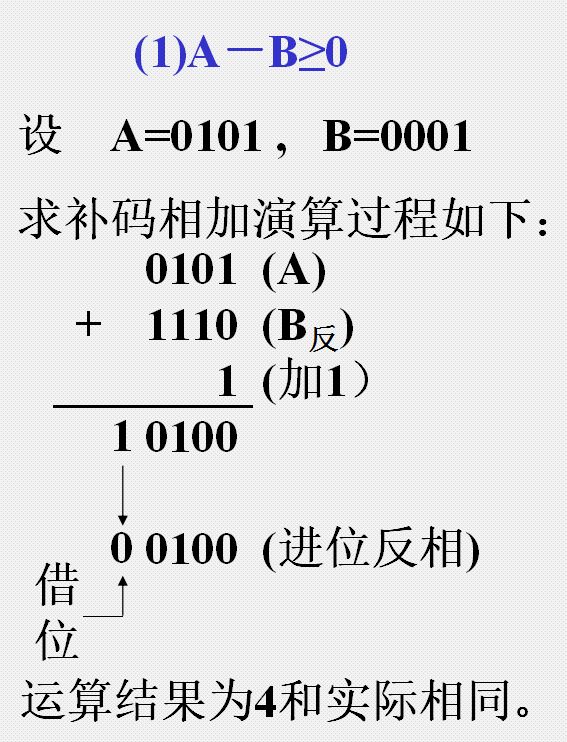

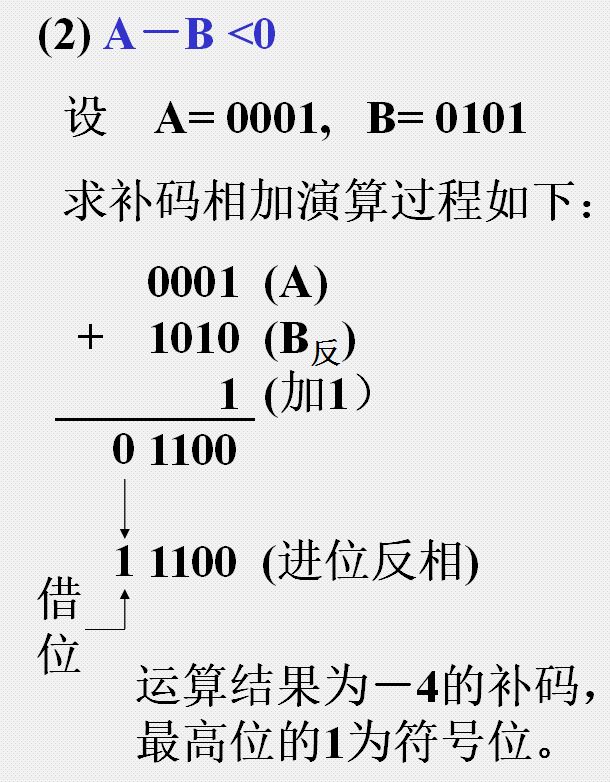

二进制减法运算

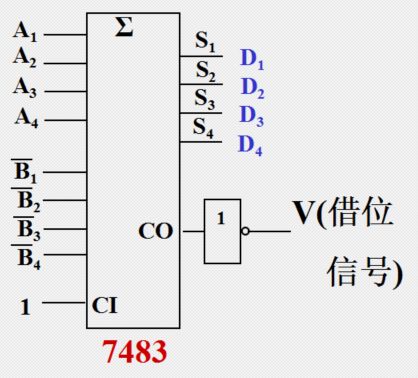

(1)式的实现方法: (以4位数相减为例)

借位信号实现减2n 的功能: 当A+B反+1 的高位有进位时,

该进位信号和2n 相减使最高位为0, 反之为1。

分两种情况讨论:

由符号决定求补的逻辑图

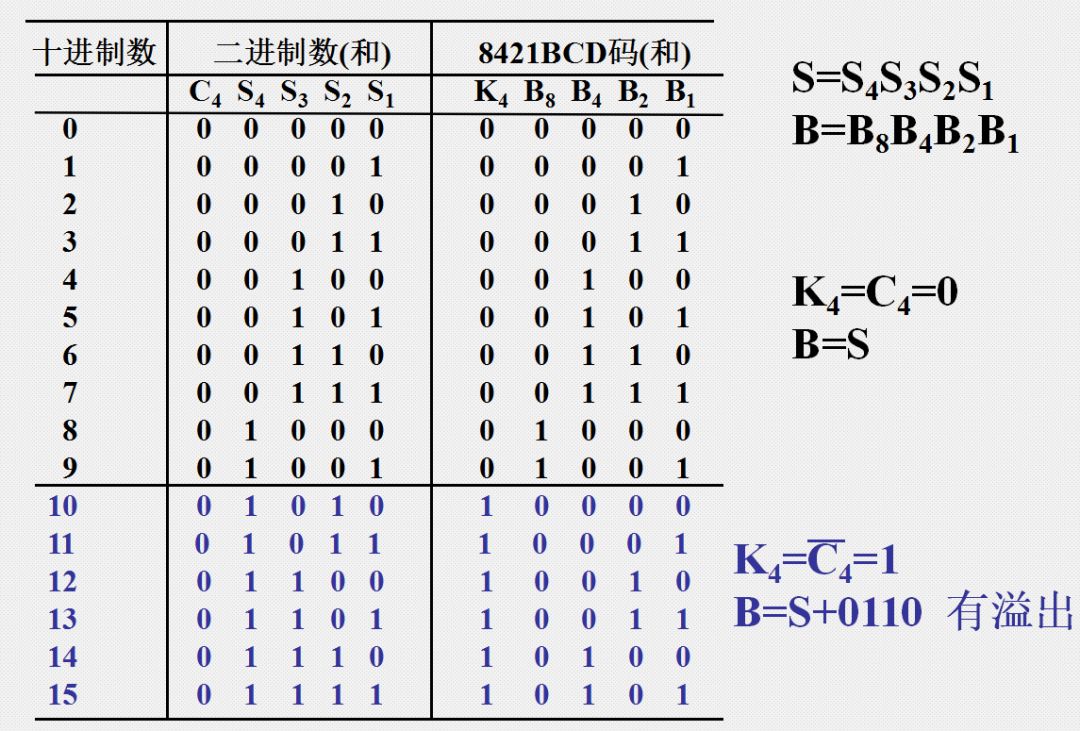

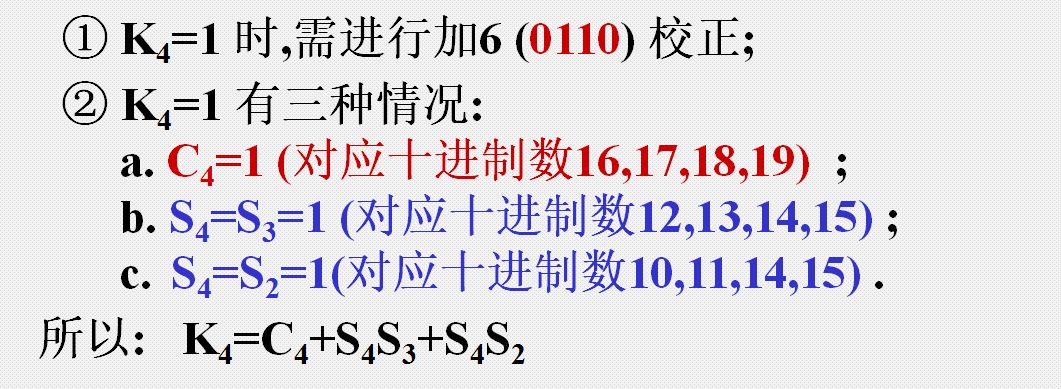

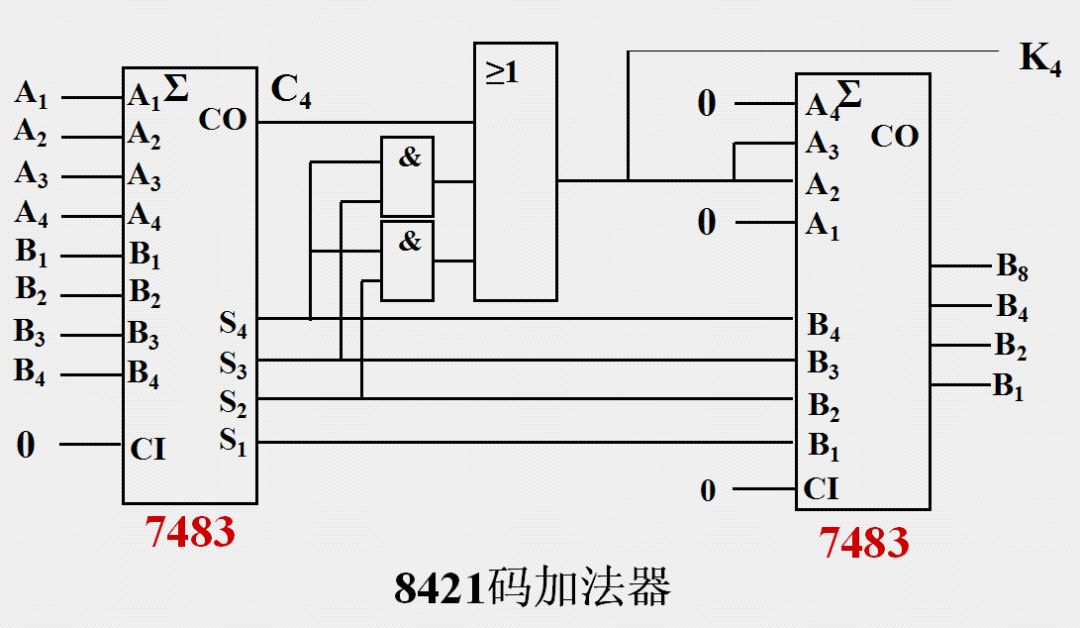

利用7483(四位二进制加法器)构成8421BCD码加法器.

二进制数和8421BCD码对照表

总结上表,可得:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

4位并行的BCD加法器电路图2009-03-28 12524

-

加法器2016-10-20 0

-

什么是加法器?加法器的原理是什么 ?2021-03-11 0

-

多位快速加法器的设计2010-05-19 934

-

加法器,加法器是什么意思2010-03-08 5195

-

十进制加法器,十进制加法器工作原理是什么?2010-04-13 13057

-

FPU加法器的设计与实现2012-07-06 915

-

同相加法器电路原理与同相加法器计算2016-09-13 55915

-

加法器原理2019-06-19 25176

-

加法器设计代码参考2021-05-31 828

-

运算放大器的同相加法器和反相加法器2022-08-05 24066

-

加法器的原理及采用加法器的原因2023-06-09 4021

-

4位加法器的构建2023-07-04 218

-

镜像加法器的电路结构及仿真设计2023-07-07 1480

全部0条评论

快来发表一下你的评论吧 !