聊一聊IC领域中的SRAM

电子说

描述

在IC领域,SRAM(Static Random-Access Memory)是一种静态的随机存取存储器。“静态”是相对于动态随机存取存储器(DRAM)而言,只要系统不断电,里面储存的数据就可以一直保持。而DRAM里面用电容储存的数据就需要周期性地刷新。

为什么要聊一聊SRAM,因为比较大一点的IC芯片中都可能有SRAM的电路。如CPU中的 caches,或者一些芯片中用作缓存大量的数据(如果用常规的LATCH 或者 DFFP存大量数据,那所耗费的面积就太大了),或者作为IP用在ASIC和FPGA中。而且SRAM的基本原理相对比较简单,好掌握。

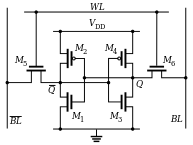

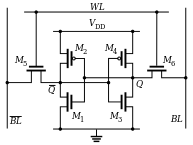

其实常用的SRAM的架构也很简单,下图就是包含6个晶体管的CMOS SRAM最基本单元。

两个反相器的输入、输出Q,Q非交叉连接,再加上2个控制管M5和M6。

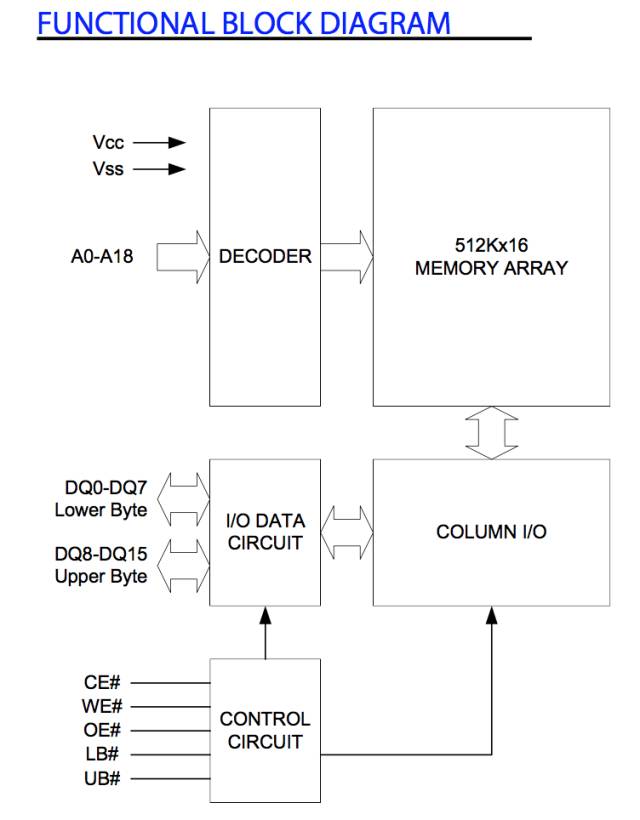

网上随便找了一个SRAM的datasheet,截了一张功能块的图:

这个SRAM的容量就是8M bit ,就是8M X 6管基本单元。 左上是一个地址译码电路 产生6管单元中的WL/BL 信息。 中间的I/O DATA CIRCUIT 和 COLUMN I/O就是用来写数据的bus线输入以及读数据bus线的输出。最下面的CONTROL CIRCUIT是读写的控制电路。

SRAM有3种工作状态:空闲standby , 读 reading ,写 writing .

Standby

如果WL都没选中,那么控制管M

5与M6断开,由M1– M4组成的两个反相器作为latch一直保持自己的状态。Reading

假设SRAM一开始存的内容为 0 , Q点的电位为低, Q非点为高。读操作开始后,有上拉信号将BL/BL非这2条线拉为高电压VDD,随后译码选出的WL电压变成VDD, 使得控制管M

5与M6导通,因为BL和BL非连到一个SA(放大器)的两端,只要BL与BL有电位差,SA就会把这种差异放大,得到最终的输出结果。当然这边要注意这几个管子的size,如果M6管比较强,BL在被拉低的过程中,Q点会被充电,电压有可能会变高到超过M1的阈值电压,从而导致这个latch存的值被冲掉。所以这边M3 M6存在管子的size要求,简单而言M3 > M6。具体的计算方法一些教科书上都有。

Writing

写操作开始后,同样也会有上拉信号将BL/BL非 拉为高电压VDD,选中的WL电压变成VDD,使得控制管M

5与M6导通,写控制电路会驱动BL和BL非。假设现在要写0,原来存的是1, 那BL和BL非就会被驱动成0和1,M6 与M4管开始fighting,直到Q点的电压降到低于M1管的阈值电压,M1关断,SRAM存储的值才能翻转。同样这边管子M4 M6存在特定的size要求,简单而言M6 > M4,不然M6 fighting 不过 M4,无法写入数据。具体的size计算方法一些教科书上都有。

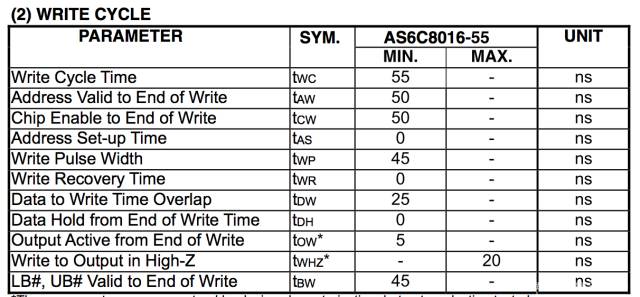

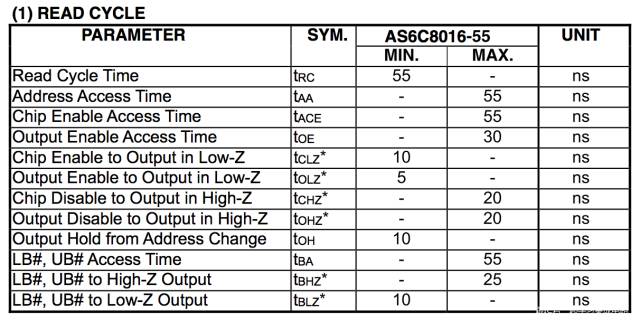

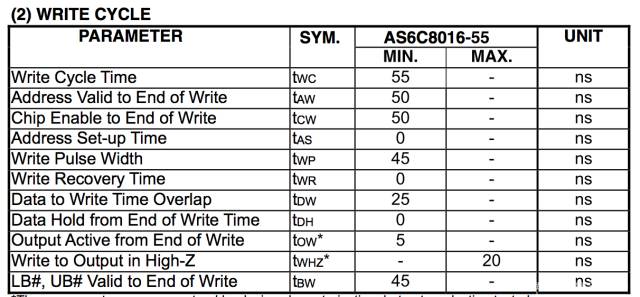

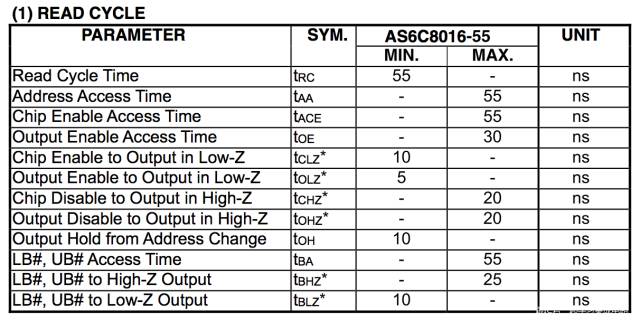

上面2张图是我从SRAM datasheet里面找的AC特性,可以看出读写量级都是几十ns的量级,不过这个时间应该跟SRAM的容量有很大的关系,容量小的更快一点,大家设计的时候可以参考一下

全部0条评论

快来发表一下你的评论吧 !